2020年11月5日(木)・6日(金) 9:00 〜 18:00 JST(GMT+9) オンライン開催

スケジュール

DAY 1 : 2020年 11月 5日 (木) 9:00 〜 18:00 JST(GMT+9)日本時間

DAY 2 : 2020年 11月 6日 (金) 9:00 〜 18:00 JST(GMT+9)日本時間

質問の受付方法と デモブースのご案内

- RISC-V 協会の Slack に参加しよう! この Slack は RISC-V 関係の情報交換の場であると共に、RISC-V Day Tokyo 2020 の質問受付用のチャンネルがそれぞれの講演に対して用意してあります。ぜひ この RISC-V 協会の Slack にご参加いただき、参加者との交流を深め Day Tokyo をもっともっとエンジョイしてください!

- セッションに対するご質問は、RISC-V 協会の Slack もしくは、Twitter で受付ます。Twitter でご質問をする場合には、以下のプログラムのプレゼン題名の下に付記したハッシュタグを付けて Tweet してください。Tweet には、あわせて #riscv_day と #risc_v のハッシュタグも付記していただくと、RISC-V 関連の情報を探している方々の手助けになりますので、どうぞよろしくお願いいたします。

- オンライン開催の新しい試みとして「バーチャルデモブース」をご提供しています。ライブストリームを通した臨場感あふれるデモや質疑応答、また個別の「プライベート・トーク(Email)」も可能です。ぜひこの新しい試みを RISC-V Day Tokyo でご体験ください!

DAY 1 : 2020年 11月 5日 (木) 9:00 〜 18:00 JST(GMT+9)日本時間

| 時間 | 言語 | プレゼンテーション題名 | 発表者 | 所属機関 | 講演資料 |

|---|---|---|---|---|

| 9:30 | 日英 | カンファレンス紹介 (プレゼンテーション と 仮想デモブースシステム) | 笠原 栄二 | エスペラント テクノロジーズ(米国) | |

| 10:10 | 英 | RISC-Vには制約がありません:テクノロジーを自由に使え、イノベーション機会があり、コミュニティによる開発が可能です。 | キャリスタ レッドモンド | CEO, RISC-Vインターナショナル (スイス) | |

| 11:00 | 日 | SiFive RISC-Vの最新概要とArchiTek社によるユーザ事例紹介 | 石井 敦 | 日本代表, SiFive社(米国), 近藤 芳人 | RISC-V担当マネージャ, DTSインサイト(日本), 高田 周一 | 代表取締役, Architek社(日本) | PDF1 |

| 11:50 | 日 | AIチップ設計拠点 | 内山邦男 | 拠点長, AIチップ設計拠点, NEDO事業, 産業技術総合研究所(日本) | |

| 12:20 | 英 | RISC-V用Linuxとファームウェア事情:RV64開発状況、RV32 フェドラLinux ブートストラップスの展開、Linuxプラットフォーム仕様の更新 | ウエイ フー | シニアソフトウエアエンジニア, プラットフォーム活性化本部, レッドハットソフトウエア(IBM) 上海(中国) | |

| 12:50 | 英 | ヴァンガード-ベトナムで最初のオープンソースRISC-V SoCプロジェクト | Quynh Do-ngoc* and Quan Nguyen-hung(ベトナム)| VLSIテクノロジページ | |

| 13:20 | 日 | 医薬を設計するための専用高性能RISC-Vコンピュータ | 泰地 真弘人*, 理化学研究所 生命機能科学研究センター(日本) | Video |

| 13:50 | 日 | ASIP Designerを用いたRISC-V ISAプロセッサの実現とその拡張 | 伴野 充 | アプリケーション・エンジニア, ソリューション・グループ, 日本シノプシス合同会社(米国) | |

| 14:20 | 日 | RISC-Vアーキテクチャを適用し派生させた高度なSIMDアーキテクチャ | 山口佳樹*, Tan Yuxi, Abdelhamid Riadh Ben | 筑波大学(日本) | Video |

| 14:50 | 英 | TEEハードウェアのためのRISC-V実装 | クリスチャン デュラン*, トロン-トック フエン, 範 公可 | 電気通信大学, 塚本 明, 須崎 有康 | 産業技術総合研究所, セキュアオープンアーキテクチャ・エッジ基盤技術研究組合(日本) | |

| 15:20 | 日 | 「Chiselで始めるデジタル回路設計」の翻訳作業について | 宗藤誠治 | 日本IBM、Chisel勉強会(日本) | |

| 15:40 | 英 | 「チゼルを使ったデジタルデザイン」(Digital Design in Chisel)著者による言語の使用法の説明 | マーティン スケベル*, 助教授, デンマーク工科大学(デンマーク) | |

| 16:10 | 日 | ハードウェア記述言語Chiselをもっと活用するためのDip | @msyksphinz | FPGA開発日記著者 | |

| 16:30 | 英 | RISC-VのIoT応用に関する研究開発活動 | Duy-Hieu Bui* | 助教授, SISLAB研究所, ベトナム国家大学ハノイ校ベトナム国家大学ハノイ校(VNU)and Xuan-Tu Tran | 助教授, ベトナム国家大学ハノイ校ベトナム国家大学ハノイ校(ベトナム) | |

| 17:00 | 日 | なぜ教育用モデルプロセッサにRISC-Vを使用すべきか? | 天野 英晴* | 慶應大学(日本) | |

| 17:20 | 英 | RVfpga:RISC-Vに基づく世界初の完全なコンピュータアーキテクチャコース | ジーユーワンヤン フィー | イマジネーションテクノロジー(英国) | |

| 17:40 | 英 | 「大学のプログラム」–私たちは皆、このフレーズを聞いたことがありますが、それは実際にはどういう意味ですか? | ロバート C.W. オーウエン他 | イマジネーションテクノロジー(英国) | Video |

| 18:00 | 日 | プログラムガイド (1日目反省事項と2日目プログラムの案内) | RISC-V 協会(日本) | Video |

DAY 2 : 2020年 11月 6日 (金) 9:00 〜 18:00 JST(GMT+9)日本時間

| 時間 | 言語 | プレゼンテーション題名 | 発表者 | 所属機関 | 講演資料 |

|---|---|---|---|---|

| 9:00 | 英 | PolarFire SoC 入門 | ティム モリーン | マイクロチップス FPGAビジネスユニット マーケティング テクニカルフェロー(米国) | |

| 9:30 | 英 | SiFive の HiFive Unmatched RISC-V Linux PC mini-ITX フォームファクターボード | ヤンサップ リー | チーフテクノロジーオフィサー SiFive (米国) | |

| 10:00 | 英 | エッジAI / ML、セキュリティ、スマートIoTセンサー向けに最適化されたASA RISC-Vプロセッサ | Islam Md Ashraful* | ASAMicros社(米国) | |

| 10:30 | 英 | エスペラントのRISC-V機械学習SoCの検証メソドロジー | Shankar Jayaratnam、Raymond Tang | エスペラント テクノロジーズ(米国) | |

| 11:00 | 日 | RISC-VマイコンGD32VF103のご紹介 | 影山 賢二 | ギガデバイスジャパン株式会社(中国) | |

| 11:30 | 日 | JASAにおけるRISC-V活動とET & IoT Digital 2020 展の紹介 | 竹岡 尚三 | 技術本部長 兼 応用技術調査委員長, 一般社団法人 組込みシステム技術協会(日本) | |

| 12:00 | 日 | nVidia-ARM合併、ルネサスのRISC-V採用、その裏にある大きなオープンソースハードウェアの潮流 | 河崎 俊平 | SHコンサルティング株式会社(日本) | |

| 12:30 | 英 | AI:RISC-V Linuxを使用したエッジ → サーバーへスケーリングするロードマップ | Florian Wohlrab*, EMEA日本地域営業代表, アンデステクノロジ(台湾) | |

| 13:00 | 英 | キーノート: 最新で最先端のRISC-V開発ツールで一歩先を行く製品開発を実現 | ショーン・プレストリッジ | 米国 FAEチームリーダ, IARシステムズ(スエーデン) | |

| 13:30 | 日 | リアルタイムOS「VxWorks」のRISC-Vサポートについて | 木内 志朗 | ウインドリバー株式会社 営業技術部 シニアエンジニア(米国) | |

| 14:00 | 日 | AdaCore社 RISC-V Ada/C言語ソフトウエア開発ツール モデルベース、形式検証、各種安全規格対応#day2_10_adacore | 福徳 信夫 | アイティアクセス株式会社 AdaCore(エイダコア)(仏) | |

| 14:30 | 英 | シンタコア社 32ビット/ 64ビットRISC-V IP製品ラインアップ と SCRxファミリのソフトウェアエコシステム(仮称) | アレキサンダー レッドキン | シンタコア社(ロシア) | |

| 15:00 | 英 | ASICおよびFPGA開発における完全なオープンソースおよび継続的インテグレーション主導のフローの実現(仮題) | マイケル ジエルダ | チップスアライアンス(米国) | |

| 15:30 | 英 | クラウドベア社のRISC-VプロセサIP製品ラインアップ | アレキサンダー コゾロフ | クラウドベア社(ロシア) | |

| 16:00 | 日英 | イマジネーションテクノロジーズプレゼンテーション | クリストフ ビーツ | シニアダイレクタ、 プロダクトマネージメント、イマジネーションテクノロジーリミテッド(英国), 内村 浩幸 | 代表取締役社長, イマジネーションテクノロジーズ株式会社(日本) | |

| 16:50 | 日英 | RISC-V協会2021年度プログラム予告 | RISC-V協会(日本) |

バーチャルデモブース

バーチャルデモブースは、デモの様子をライブストリーミングにて一般公開するものです。デモ実演者に対する質問も可能で、技術内容をより深く理解する絶好の機会です。

| 時間 | 内容 | Company / Organization | デモ資料 |

|---|---|---|---|

| 5日 10:00-16:00 6日 10:00-16:00 | SiFive最先端技術ショーケース | DTSインサイト LSI設計サービス部会員 (日本) | |

| 5日 10:00-17:00 6日 10:00-17:00 | AdaCore社 RISC-V Ada/C言語ソフトウエア開発ツール紹介:モデルベース、形式検証、各種安全規格対応 | AdaCore(仏) | PDF Video |

| ライブなし | RISC-V版 VxWorks 7 リアルタイムOSと Workbench 4 開発環境のご紹介 | ウインドリバー株式会社(米国) | PDF Video |

| 5日 14:00-16:00 6日 14:00-16:00 | SHC RISC-Vデモ:Amazon AWS IoT サービス プラットフォームへのAndesN22 RISC-V安全接続 | SH コンサルティング カンパニー リミテッド(ベトナム) | PDF Video |

| TBD | ARSIMを使用したAR32Zのラピッドプロトタイピングとテスト | Islam Md Ashraful (CTO), Mir Tanveer Islam (FPGA設計エンジニア) | ASAマイクロシステムズ Inc. (米国) | PDF Video |

| 11/5-6 2pm-4pm | 西田 圭吾, 理化学研究所 生命機能科学研究センター(日本) | Slides | |

| ライブなし | IAR システムズ(スウェーデン) | PDF1 PDF2 Video | |

| 5日 15:00-17:00 6日 15:00-17:00 | 伴野 充 | ソリューションズグループ プロセッサソリューション シニア・アプリケーション・エンジニア, 日本シノプシス合同会社(米国) | PDF Video | |

| 6日 13:00-17:00 | Florian Wohlrab | Andes TechnologyのEMEAおよび日本営業責任者 | PDF Video |

写真: RISC-V Day Tokyo 2019 の様子

「Chiselを使ったデジタルデザイン」の日本語訳

Chisel Study Groupは、Martin SchoeberlのChisel本(http://www.imm.dtu.dk/~masca/chisel-book.html)の日本語訳の発行に取り組んでいます。 Githubでリリースされたソース(無料、https://github.com/chisel-jp/chisel-bookに予定)。 PDFは上記のURLからダウンロードできます。 近い将来、紙版の販売も計画しています。以前、RISC-V協会は、次のRISC-Vの出版物の日本語訳を出版するよう手配しました。「RISC-Vリーダー」および「コンピュータアーキテクチャ:定量的アプローチ」

背景説明

RISC-V Day Tokyo Online 2020のテーマは『5Gモバイル、ストレージ、ウエアラブル、自動車応用の次に控えるRISC-Vの研究、開発、技術、市場』です。

カリフォルニア大学バークレー校は、1980年代にコンピュータアーキテクチャにRISC(リスク、縮小命令セットアーキテクチャ、Reduced Instruction Set Architecture)という新機軸を提案し、コンピュータの潮流に大きな影響を残しました。そのカリフォルニア大学が2015年に世に問うたのがRISC-V(リスクファイブ)です。RISC-Vは(1)プロセッサアーキテクチャ、(2)実装設計、(3)知財配布、に新モデルを提供し、令和元年にIBM、ARM、MIPSなどのビジネススタイルにも大きな影響を与えました。

1945年に最初のコンピュータを開発した際にも、主たる発明者の1人ジョンフォンノイマンは、オープン命令セットとオープン実装をシェアすることがベストと考え、特許出願を放棄しました。競合他社は、みな、独自コンピュータアーキテクチャ(命令セットアーキテクチャ、ISA = Instruction Set Architectureに走りました。以来、各企業が独自の命令セットアーキテクチャ(ISA = Instruction Set Architectureという)を開発し、製造権、使用権を独占して、コンピュータにおける独占禁止法案件の多くはISAに関連したものでした。最近、75年前にジョンフォンノイマンが考案した、1つのISAを業界全体で共有し、ソフトを業界で共有する理想を実現する試みが行われています。これがRISC-Vです。

RISC-Vは(1) オープンな命令セット、(2) オープンソースプロセッサ、(3) オープンソースソフトウエア、(4) オープンソースEDAツール等、(5)ユーザ拡張命令 をサポートする、新ビジネスモデル、新知財モデルを提示しました。この新モデルは、現在多くの企業に採用されるのみでなく、IBM Power、MIPS、ARMの独占モデルを採用している企業にも影響を与え、2019年には、これら企業もビジネスモデル、知財モデルを一部変更するということが相次ぎました。

RISC-Vは、スイスジュネーブに本拠を置くRISC-V Foundationが主導的な役割を持っています。国内外の半導体会社は、すでにRISC-Vを試作、量産、出荷し始めています。令和元年に、世界のメンバ企業の数は360を超え、RISC-V標準に沿って開発されたプロセサIPは56種類に達し、SoCプラットフォームIPは21種類、SoCは9種類が生産されました。

令和元年には、RISC-V(リスクファイブ)は、研究開発から商品流通フェーズへ確実に進化しました。大学や研究機関や企業における研究を活性化しました。、オープンソースEDAツール、オープンソースIP、フォーマル検証、セキュリティ、他の分野を含みます。

を去年末に作りました。半導体調査会社Semicoは2025年までに624億個のRISC-Vが出荷されると予想。RISC-Vがサムソン「5G」モバイル2020年モデルに採用。です。

2019年 リスクファイブ 10大ニュース

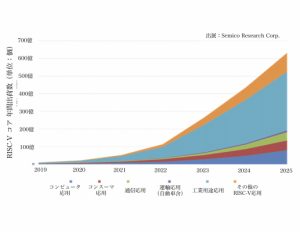

1。Semico Research Inc.が2025年までに624億個のRISC-Vが出荷されると予想: 11月25日、Semico Research Inc.がRISC-Vの将来マーケット規模予測を発表しました。Semico Researchは、RISC-Vは、2018年から2025年にかけて146.2%の年間伸び率(CAGR)が期待できると予測しています。Semicoは、2025年までに624億個のRISC-V CPUコアが出荷されると予測しています。最大のセグメントは産業用で、167億個のコアを使用するとしています。

Semicoは、5つの主要エンドマーケット(コンピューター、消費者、通信、運輸、産業)の25応用のデータを分析、4つの応用製品カテゴリーについて予測出荷数量を見積もりました。Semicoの算定では、2018年から2025年までの出荷数量ベースの年間成長率予測で、RISC-V CPUコア出荷数の年間成長率が最も高くなるのは「5G」ワイヤレスにより出現する応用製品です。したがって、通信応用セクターがRISC-V出荷数量の最大の伸び率を達成すると予測しています。

自動車業界の電子化へ関心は高く、安全性、車内体験、運転者支援、無線通信のためのCPUベースのシステム採用が増えており、輸送機器がで2番目に年間成長率の高いRISC-V CPUコア応用セグメントとしています。下図にSemico Research社が発表したRISC-Vコアの年間出荷数値のグラフを紹介します(出展: Semico Research Inc. 和訳: RISC-V協会)

2。RISC-V がサムスンの2020年型「5G」モバイル機器に搭載出荷中:12月20日、韓国サムスン電子は、RISC-Vを使った「5G 」通信モジュールが2020年モデルのサムソン「5G」モバイルフォン、および将来の、車載「5G」ネットワーク機器に搭載されると公表しました。

日本でも、2020年に実用化予定の「5G」通信は現在の携帯通信の100倍の速度があります。2時間の映画を3秒でダウンロードでき、一部の海外市場ではすでに採用が始まっています。韓国サムスン電子は、次世代通信規格「5G」に対応したスマートフォンの開発に積極的に取り組んでおり、主要企業の基幹製品にRISC-Vが使用されるのは、nVidia社のAIチップセット、Western Digital社のストーレージ用チップセット、に続くものですが、「5G」通信は数量も多く、大きなインパクトを持つ動きです。

サムスン電子は、2017年に「5G」RF IC試験チップをRISC-Vで試作。2018年にアンテナ + PAモジュール用「5G」マルチバンドフェーズドアレイRFICにRISC-Vで試作、2019年に、セントラル「5G」RF ICをRISC-Vで試作し、技術開発を積み重ねて今回の発表にこぎつけたとのことです。

下にサムスン電子が12月20日のRISC-V Summitで発表したスライドの1枚にある「5G」チップセットのブロック図を示します。

3。IBM(Redhat)とGoogleが後押しでRISC-Vにマイクロサービス用の言語やOS部ソフト移植が相次ぐ。

12月10日にIBM(Redhat)は、システム管理や検出を容易化し、サービスのスケーラビリティを向上するRISC-V用『クーバネテス』のデモを米国で行いました。Google開発のGo言語で書かれた『クーバネテス』システムのRISC-Vへの移植作業も進行中です。

120億円を資金調達したRISC-V企業であるカリフォルニア大学スピンアウトのSiFive社社長が6月に「5年以内にRISC-Vサーバを商業的運用にこぎつける」と宣言しました。この宣言で、ステークホールダのオープンソースコミュニティが一斉に立ち上がり作業を始めました。RISC-Vは2019年にデビアン移植対象アーキテクチャに格上げされ。レジリエンス、運用率、スケーラビリティを保証する、コンテナ技術、マイクロサービス技術など、の移植が次々とRISC-Vに実装されています。

RISC-V 命令セット(ISA)の基盤は言語サポートです。1月からRISC-V用新コンパイラのLLVM/ClangのDARPAファンディングが始まり、Clang、OpenCL、Rustに渡る広範な言語サポートの基盤構築がスタートしました。5月に、GNU Debugger(GDB)「GDB 8.3」が、C、C++、Ada、Go、Rust言語をサポートするRISC-Vのサポートを実装。9月3日に、Google社開発のサーバシステム言語Goも次期レリースVersion 1.14でRISC-Vを正式サポートすると公表しました。

従来のコロケーションとか、仮想マシンなどに代わり、サーバ応用は、マイクロサービスなどの抽象度の高いサービスに移行しつつあります。これにRISC-Vを対応させる動きが商用化の前段階として着々と進んでいます。システム運用インフラストラクチャサービス(IaaS)、アプリケーション実行環境サービス(PaaS)、マイクロ機能サービス(FaaS)などのソフトもRISC-Vへの移植が続々と行われています。OpenFaaSの全機能版サーバーレスRISC-V実装では、プルリクエストがアップストリームにマージ中です。

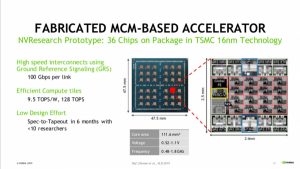

4。NVIDIAが 超低消費電力 深層学習推論アクセラレータをRISC-Vで開発、9.5Tオペレーション/ワットを達成

NVIDIA社では、2016年からGPU製品の制御マイコンとしてRISC-Vを採用しています。9月4日、高性能コンピューティング企業のNVIDIAは、今後の、RISC-Vの使用分野を開示しました。NVIDIAは電力性能の高い推論エンジンを含むRC18テストチップをTSMC標準16ナノメートルプロセスで試作し、9.5Tオペレーション/ワットを実測しました。推論アクセラレータ部品の入力/出力コアとしてRISC-Vを使用した約13.5ワットで推論できるチップを開発しました。

Google社やAmazonが積極的に構築しているハイパースケーラーやクラウドビルダーでは、推論エンジンに一定の電力プロファイルと性能が集約された総合的な電力性能が求められます。NVIDIA社のRC18は、高エネルギー効率設計で、13.5Wで毎秒128兆兆回のオペレーションを行えるディープラーニング推論ワークロード用高性能アクセラレータです。1チップに、8個のベクトル積和(MAC)ユニットを持つ要素(PE)もち、入力および出力機能は、RISC-V命令セットアーキテクチャを持つ単一のマスターコアが実行します。

RC18アクセラレータは、現行世代「NVIDIA深層学習アクセラレータ」(NVDLA = Nvidia Deep Learning Accelerator)を置き換えるこできます。NVDLAと非常によく似た設計で、ベクトル幅、ベクトル単位数、バッファ配列サイズ、ループ並列化 で 演算をステージングする方法などのソフトツール開発用にチップ開発を行いました。NVIDIAは、オープンISA、拡張性、柔軟性、ロイヤリティを払わなくていいという理由でRISC-Vを採用しました。

電力性能の良いアクセラレータを構築する方法を見つけ出すために、クロック速度を十分に遅くして、チップで最も低い電圧を使えるコア部が追随できるようにし、すべてのクロックを実行して電力とタイミングマージンをどこが浪費するかを調査しました。チップの微小領域からなる処理要素(Pes)は局所的に論理生成され、電源を追跡する個別クロックで演算実行します。マージンを測定するため、演算が実行できるギリギリの限界まで周波数を上げ、落ちた時を見極めて再度減速します。

微小領域を出入りする信号は同期する必要があるため、NVIDIAは、半クロックサイクルで同期する高速な同期化回路を開発しました。従来システムでは、1つのクロックドメインから別のクロックドメインに移行するのに5~6クロックサイクルかかります。この同期化テクノロジーは、 5月の非同期回路とシステムに関する国際シンポジウム(ASYNC)で最優秀論文賞を受賞しました。

RISC-Vを使用したNVIDIAのRC18深層学習推論アクセラレータを下図に示します。36個のチップ(2.4mm x 2.5mm)をマルチチップモジュール(MCM = 47.5mm x 47.5mm)に実装しています。100 Gbpsの通信速度を持つ高速の相互接続と高電力性能計算タイルを16個ずつTSMC 16nmテクノロジーで製造し、これら36個のチップをMCMに実装し0.52Vから1.1Vで駆動、0.48-1.8GHzで動作させます。9.5テラオペレーション/ ワットの電力効率で、1ユニットで毎秒128テラオペレーションの演算能力を実現します。

下に、NVIDIAが8月18日にスタンフォード大学で開催されたホットチップスで発表したスライドの1枚を示します。

5。RISC-Vフラッシュマイコンからサーバ応用RISC-VまでチップとIPが勢ぞろい

(1)中国資本ギガデバイス社がRISC-Vフラッシュマイコンを販売開始:8月23日に、NORフラッシュメモリを供給している中国資本のギガデバイス社(GigaDevice)がRISC-Vフラッシュマイコンを発表。同社はSTM32互換のARM MCUのGD32シリーズをSTから調達するより安価な代替品としてシェアを伸ばしていることで知られていました。新たにラインアップに加えられたRISC-VベースのフラッシュマイコンGD32Vシリーズは、同社ARM Mコアよりも15%高速。消費電力は50%減としています。GD32Vシリーズでは、STMとの互換性に拘泥せず、周辺機能は 独自独自機能拡張をしており、GD32シリーズより周辺機能が豊富です。

(2) SiFive社RISC-V IPラインアップ拡充: SiFive社は、2017年より出荷していた32-ビットマイコン用コアE3、64-ビットLinux実行可能コアU5に加え、令和元年にラインアップを大拡充しました。E2/E3/E7: マイコン、エッジコンピューティング、AI、IoT応用32ビット組み込み用途、S2/S5/S7: ストレージ、AR / VR、機械学習応用64ビット組み込み用途、U5/U7/U8:リナックス、データセンタ、ネットワークベースバンド用 64ビットアプリケーションプロセッサシリーズ、の3シリーズを拡充しました。SiFive社は、上記以外に7nmプロセスのアウトオブオーダ方式のU8コアも開発しており、ARMの全クラスに対応するプロセッサコアが出揃ったこととなります。

(3) Andes Technology社RISC-V IPラインアップ拡充: RISC-VアーキテクチャのN22「Bumblebee」IPコアは、ARM Mシリーズに比較し(1) CoreMark/MHz, (2) DMIPS/MHz, (3) CSiBe Code Sizeのベンチマークで凌駕しているとAndesは公表しています。アンデス社は、(1) Aシリーズ:アプリケーションプロセッサ(ARM Aに対応)(2) Nシリーズ:組み込みプロセッサクラス(ARM Mに対応)(3) ネットワークプロセッサのDシリーズ(ARM Rに対応)と、3つのラインアップを持っています。(1)(2)は32ビット、64ビットを両方対応しています。Aシリーズでは、エッジ応用のみでなく、サーバ応用もカバーします。

(4)「チップス・アライアンス」、FOSSi、などのRISC-Vシステムプロファイルを標準化する組織の誕生:

3月より、Google等の後援でLinux Foundation内に作られた「チップス・アライアンス」(CHIPS Alliance)、FOSS、FOSSiなど、RISC-Vでシステムを作りやすくするための周辺機能のIPを集積活動が始まりました。8コアの高性能システムを簡単にオープンソースで作れる。従来高付加価値だったチップ製品をオープンソース技術で作れるようになりました。

6。地域ニュートラルなオープンなRISC-V技術をグローバルに提供するための組織のグローバル化: 中国スマホ分野では、世界最強なAIプロセサとして、Huawei Ascend 910を7nmプロセスでARMで開発したことを発表しましたが、同チップをRISC-Vでも設計しているという2CPU戦略を表明しています。通商ブロック化が背景でスマホシステムでもRISC-VがARM(現在世界シェア99%)と並ぶ可能性があるかもしれません。

3月に、通商のブロック化によりRISC-Vの発展が妨げられないように、RISC-V Foundationは、Linux Foundationと融合しました。欧州のFree and Open Source Software(FOSS)、 Free and Open Source Silicon(FOSSi)、他の組織とも連携し、単なる米国の組織からグローバルな組織に変革しつつありました。FOSSとFOSSiは、陰陽のように、ISAを媒介として根源で一つに統合された血の通ったモノリシックな活動として展開されているように見受けます。 RISC-Vは、ヨーロッパ発のFOSS / FOSSi活動の中心的要因の1つを提供しました。FOSSとFOSSi活動は今後数年間で業界に大きな違いをもたらします。

7。RISC-Vによるデジタル半導体研究を促進

(1)カーボンナノチューブRISC-Vの製造プロセス: MITは先週、標準CMOS製造設備と、市販CMOS製造工場にある材料とプロセスを使用して、カーボンナノチューブ(CNT)MOSFETで作られたRISC-V CPUを発表しました。カーボンナノチューブFETを使ったのRISC-Vプロセッサだと。エネルギー効率が10倍良いとしています。

(2)オープンソースEDAツールがRISC-Vをビークルに急伸:RISC-Vをビークルとして、新世代のオープンソースEDAツールがと開発されつつあります。新刊本”Digital Design with Chisel”が正式に発刊され、新設計フローも確立しつつあります。従来から存在していたVerilatorのようなEDAツールが広く使われるようになり、その信頼性と性能と機能が急激に向上しました。オープンソースEDAツールは、過去20年間どんぐりの背比べでしたが、今年になって強いコンテンダが出現しました。コシミュレーションとかのメソドロジもオープンソースで実現できるようになりました。

FPGAツールYosys+nexpnrは、その単純さゆえに商用FPGAツールに比較して実行速度がとてつもなく速い。FPGA自動配置配線ツールnextpnrはデバイス依存部と一般処理部からなり、デバイス依存部を書き換えればどんなFPGAにマップできます。現在は、ラティスICE40とECP5、ザイリンクスのFPGAがサポートされています。オープンソースツールは多様なユースケースを可能にします。検証フェーズでテストベクタを高速で試すために「部分コンフィギュレーション機能」を活用することができます。形式的検証の重要性も高まりつつあります。ハードウェアトロイの木馬などの意図しないロジックは、開発プロセスの複数のポイントで挿入される可能性がありますが、これらを形式的検証で検出することができます。

(3)NVIDIA の オープンソース化への取り組み:nvidiaは、オープンソース機械学習エコシステムを開発する取り組みNVDLAをリードしています。 NVDLA Deep Learning Inference Compilerも、NVDLAのRTLもオープンにしました。

(4)IBMの オープンソース化への取り組み: サーバ・CPUの世界は確実に変わろうとしています。IBMは、Powerアーキテクチャを無償化しました。RISC-Vに慣い、Power CPUの命令セットを無料化しました。RTLをオープンソース化しました。マイクロワット(Microwatt)というOpenPowerのソフトコアも発表されました。VHDL 2008で書かれた小さなOpen POWER ISAソフトコアで、シンプルでわかりやすいことを目指しています。IBMが「開発者がハードウェアとソフトウェアがPower上で連携して動作することを保証するために使用する定義」、Power Instruction Set Architecture(ISA)をオープンソース化、Power ISAソフトコア、のみでなくOpenCAPIインターコネクト技術、OMIメモリインタフェース技術の参照実装もオープンソース化します。

(5)MIPSの オープンソース化への取り組み: Wave Computing社がMIPS Openが展開する動きもRISC-Vがモデルになっています。

8。RISC-V Foundationのメンバ数とイベント参加者の増加

2019年末日時点で、RISC-V Foundationのメンバ企業数は460社に達しました。12月10-12日にカリフォルニア州で開かれたRISC-V Summit 2019には1650人が登録しました。9月30日に東京で行われたRISC-V Day Tokyo 2019は、日立製作所株式会社、トヨタ自動車株式会社、AdaCore社(米国)、Andes Technology社(台湾)、Codasip社(チェコ共和国)、富士ソフト、IARシステムズ(スエーデン)、NSI-TEXE(株式会社デンソー子会社)、Rambus社(米国)、SiFive社(米国)、Syntacore社(ロシア)、ユビキタスAIコーポレーション、ultraSoC社(英国)、SHコンサルティングがスポンサーとなり、360人が参加登録し、日立製作所の国分寺中央研究所内の日立馬場記念ホールで開催しました。

9。ARM TrustZonesのセキュリティを凌駕するRISC-V「シールド」「ワールドID」の概要が公表に

(1)米国DARPAセキュリティ研究プロジェクトにおけるRISC-V: 米国DARPAの助成金を使うセキュリティチッププロジェクトでは、RISC-Vアーキテクチャの使用を義務付けています。この影響で、RISC-Vはセキュリティアーキテクチャの研究に多く使われています。RISC-Vを使用したセキュリティIPは世界各国で20種類以上開発されていると推定されます。

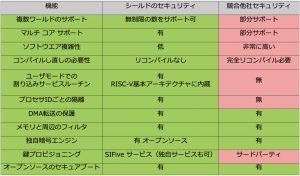

(3)SiFive社「シールド」「ワールドID」: 10月23日に米国SiFive社がARM「トラストゾーン」に対抗する「シールド」「ワールドID」の機構を公開しました。さらに、オープン標準規格、オープンソース実装を公開し誰でも使えるようにすると宣言。ARM「トラストゾーン」は、2003年にARM社が発表したプロセッサセキュリティの方式です。「ワールドID」は、ARM Aシリーズの「トラストゾーン」の機能を整理して、あらゆる尺度で「トラストゾーン」を凌駕するシステムとしました。トラスト実行環境(TEE)のサポート、ルートオブトラストのサポート、鍵管理のサポートも実装します。

下図に、SiFive社の発表資料から「シールド」「ワールドID」の競合他社との機能比較を示します。出展:SiFive社ウエブサイト、和訳:RISC-V協会

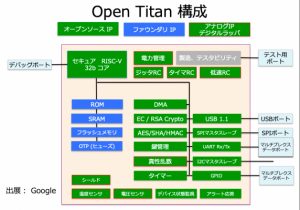

10。Google社が自社ルートオブトラスト技術をオープンソース公開する「Open Titan」: 10月14日に、Googleは、データセンターとインフラストラクチャで使用されるオープンソースのセキュアなチップ設計を開発するために、OpenTitanと呼ばれるイニシアチブを開始し、いくつかの企業や非営利団体と提携していることを発表しました。 オープンソースセキュリティは、設計を独立に検証し強化し構築することでより強力なセキュリティを実現できます。コンピューター上で実行されるアプリはウイルスに感染する可能性があります。これに対抗するサイバーセキュリティで最も重要な点は、ファームウェアとチップレベルにあります。 「Open Titan」により、多くの人々が初期設計を改善し、実装のセキュリティを強化できます。

このプロジェクトは、データセンターとPixel Phoneで使用されている既知のルートオブトラストで起動を確認し、ファームウェアが改ざんされていないことを確認するGoogle独自のTitanチップにちなんで命名されました。 検証に使用される暗号要素は、Root of Trust(RoT)と呼ばれ、「Open Titan」プロジェクトの中心です。下図に「Open Titan」のブロック図を示します。出展:Google社発表、和訳:RISC-V協会

RISC-V協会 ウエブサイト: http://riscv.or.jp/

フェースブック: https://www.facebook.com/Risc-V-Association-102528267773380/

ツイッター: @riscv_a

RISC-V Tokyo Meetupサイト: https://www.meetup.com/RISC-V-Group-Tokyo/