# Stay ahead with the latest advances in RISC-V development tools

Shawn A. Prestridge US FAE Team Leader, IAR Systems

### Agenda

- Development tools for RISC-V

- Compiler and optimizations

- Debugging

- Trace

- Code analysis

- Demo

### **Development tools for RISC-V**

#### IAR Embedded Workbench for RISC-V

- Complete build and debug toolchain for RISC-V

- User-friendly IDE features and broad ecosystem integration

- Outstanding performance through sophisticated optimization technology

- Comprehensive debugger

- ISO/ANSI C/C++ compliance with support for C18 and C++17

- Integrated static analysis

#### Device support

#### Supported base instruction sets:

- RV32I Base Int instruction set

- RV32E Base Int instruction set (embedded)

#### Supported extensions:

- M integer mul & div

- A atomic instructions

- F single precision float

- D double precision float

- C compressed instructions

- P DSP and Packed SIMD

Device support for RISC-V devices from:

- Andes

- CloudBEAR

- Microchip

- SiFive

- Syntacore

- GigaDevice

## **Compiler and optimizations**

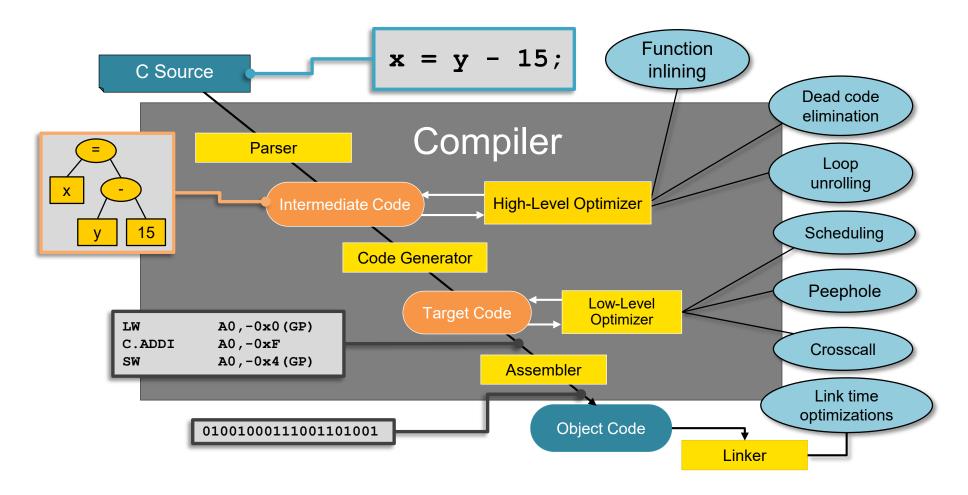

#### Compiler design

- Proprietary design based on over 37 years of experience

- Based on a platform that is common among different targets to handle global optimizations, etc.

- Target unique backend for specific adaptations and optimizations

- RISC-V specifics:

- Primary focus will be on adding standard extensions

- Initial prioritization is on code size

- Canary stack protection

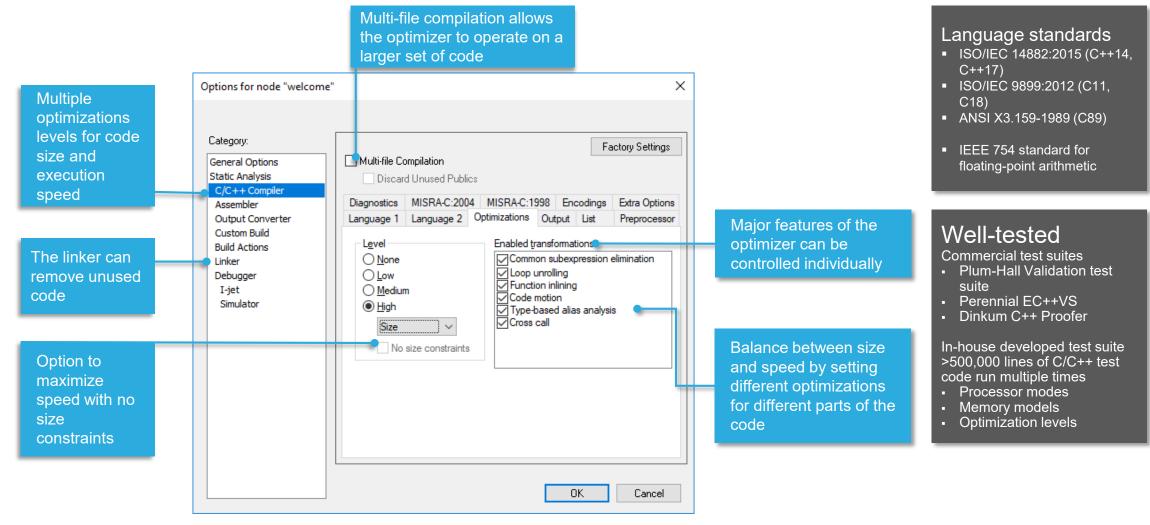

#### Compiler technology

#### **Compiler optimizations**

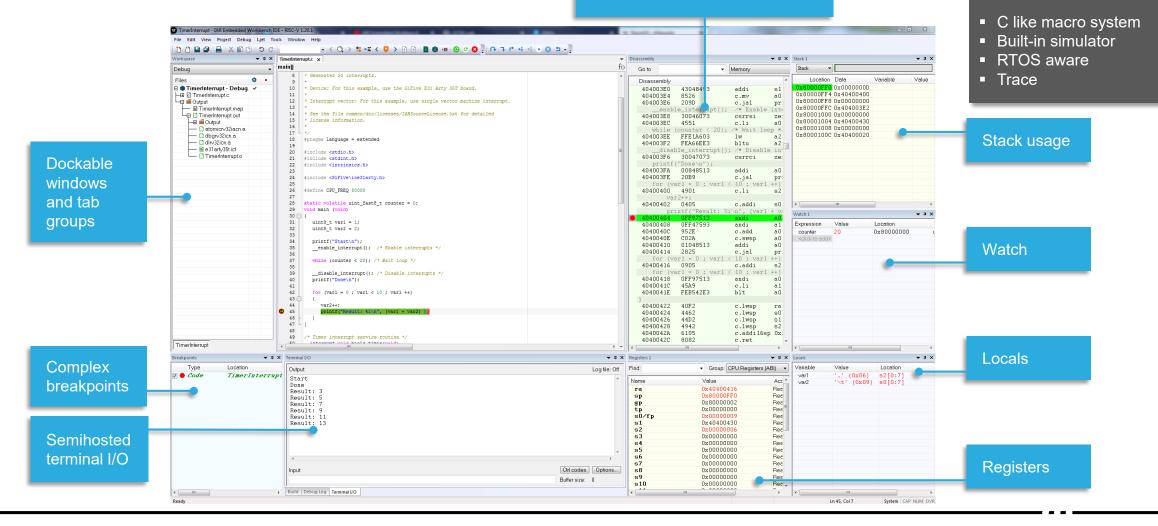

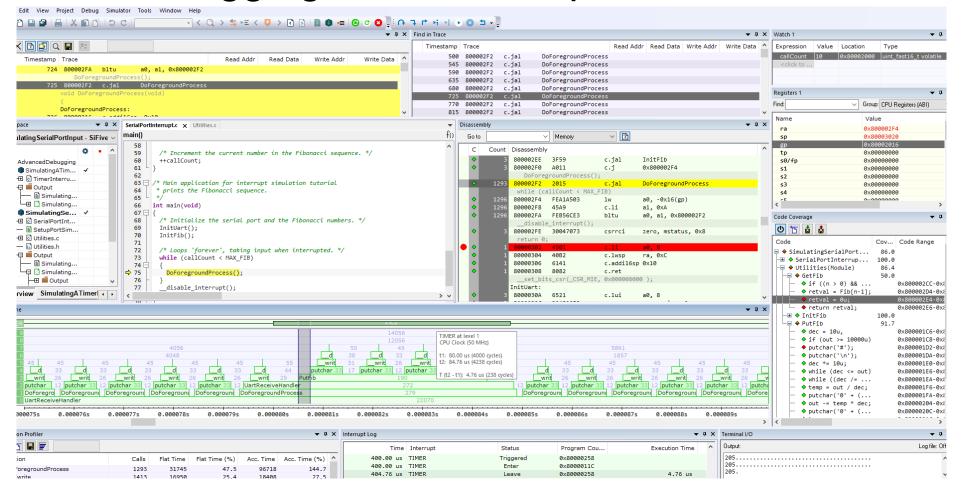

# The IAR Embedded Workbench for RISC-V offers a fully integrated debug solution

- Built on the same C-SPY debugger interface that is used in the IAR Embedded Workbench for different architectures

- Built in Simulator

- RTOS awareness plugins

- Support for C-SPY debug macros that can be used to automate debug sessions

- IAR Systems I-jet debug probe support (3<sup>rd</sup> party debug probe support will be added in future releases)

- Trace support

#### Integrated debugger for source and disassembly debugging

#### IAR Systems I-jet debug probe

- Supports RISC-V and Arm cores

- Hi-speed USB 2.0 interface (480Mbps)

- Target power of up to 400mA can be supplied from I-jet with overload protection

- Target power consumption can be measured with ~200µA resolution at 200kHz

- JTAG and Serial Wire Debug (SWD) clocks up to 32MHz (no limit on the MCU clock speed)

- Support for SWO speeds of up to 60MHz

- Unlimited flash breakpoints (\*to be added for RISC-V)

## Trace

#### Advanced debugging and trace capabilities

\*Nexus IEEE-ISTO 5001<sup>™</sup> compatible trace

#### Trace

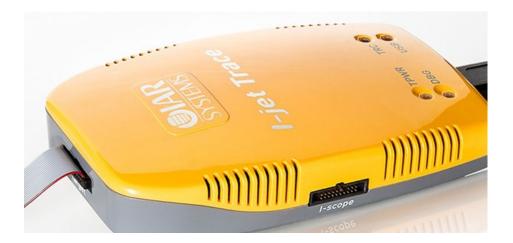

#### IAR Systems I-jet Trace debug probe

- Supports RISC-V and Arm cores

- SuperSpeed USB 3.0 interface (5 Gbps) Fully compatible with USB 2.0 (480 Mbps)

- JTAG and Serial Wire Debug (SWD) clocks up to 100MHz (no limit on the MCU clock speed)

- Up to 150MHz trace clock

- 64-bit time stamp with CPU cycle accuracy for timing analysis

- Support for SWO using Manchester and UART, at up to 200 Mbps

## Code analysis

#### Code analysis

#### IAR Systems C-STAT static code analysis

- Complete static analysis tool fully integrated in IAR Embedded Workbench

- Intuitive and easy-to-use settings with flexible rule selection

- Support for export/import of selected checks

- Support for command line execution

- Extensive and detailed documentation

- Image: total total control

Image: total contro

Image: total control

- Checks compliance with MISRA C:2004, MISRA C++:2008 and MISRA C:2012

- Includes ~250 checks mapping to hundreds of issues covered by CWE and CERT C/C++

http://cwe.mitre.org/ https://www.sei.cmu.edu/about/divisions/cert/index.cfm

#### Demo

#### Summary

Advanced toolchain for RISC-V

CODE A

IS

- Sophisticated compiler technology

- Comprehensive C-SPY debugger including Simulator

DOMAIN EXPENSE

dded systems, and lifecycle management

- Built in static code analysis C-STAT

- More than an ordinary toolbox