RISC-V Day Tokyo 2023 Summer Conference and RISC-V Booth

June 20 (Tue) , 2023 9:00 ‐ 20:30 JST (UTC+9)

Venue : Ito International Research Center , The University of Tokyo

B2 floor: Ito Hall, Foyer, Event Space

The RISC-V Day Tokyo 2023 Summer Conference will be at Ito International Research Center B2 floor: Ito Hall

[ 1 ] Conference “RISC-V Solution” (Ito Hall)

- Date and Time : June 20 (Tue) , 2023 9:00 ‐ 20:30 JST (UTC+9)

- at Ito International Research Center B2 floor: Ito Hall

- Date and Time : June 20 (Tue) , 2023 13:00 ‐ 19:00 JST (UTC+9)

- at Ito International Research Center B2 floor: Event Space / Special Presentation Venue

[ 3 ] RISC-V Booth (Foyer of Ito Hall, Event Space)

- at Ito International Research Center B2 floor: Foyer of Ito Hall, Event Space

- Date and Time : June 20 (Tue) , 2023 12:00 ‐ 19:00 JST (UTC+9)

About B2 ( Ito Hall , Event Space, Foyer ) at Ito International Research Center

https://www.u-tokyo.ac.jp/adm/iirc/en/about.html#b2

Access by train and bus: Ito International Research Center

https://www.u-tokyo.ac.jp/adm/iirc/en/access.html

RISC-V Day Tokyo 2023 Summer Conference

RISC-V Day Tokyo 2023 Summer Conference is Japan’s largest RISC-V real event. RISC-V Day Tokyo 2023 Summer Conference will be held on June 20, 2023 (Tuesday) from 9:00 to 20:30 Japan time (JST). A real presentation will be held at Ito Hall ( B2 floor of Ito International Research Center, the University of Tokyo ). The “RISC-V Booth” will be held in the foyer and the Event space of Ito Hall. We will also have an “Online RISC-V Booth” on our website. RISC-V Day(s) Tokyo gathers excellent RISC-V related technologies and products, as well as key persons and engineers, to improve product recognition, realize collaboration between companies, exchange technology, collect information, etc. We aim to provide business opportunities for We are looking forward to your participation at this opportunity! At a later date (around the end of August), we are planning to post a video and the presentation material on the web page. Information will be provided on a website.

Online RISC-V Booth

- We are offering “ Online RISC-V Booth” as a new attempt to hold online. Interactive demos and Q & A sessions through live streams, as well as individual “private talks (Emails)”, are possible. Please experience this new attempt at RISC-V Day Tokyo!

RISC-V Day Tokyo 2023 Summer Conference

[ 1 ] Conference “RISC-V Solution” (Ito Hall)

Date and Time : June 20 (Tue) , 2023 9:00 ‐ 20:30 JST (UTC+9)

at Ito International Research Center B2 floor: Ito Hall

Schedule in Japan Standard Time (UTC+9)

Please note that the speakers and contents are tentative and subject to change, and the schedule may change on the day of the event due to various reasons.

| Start-End | Dura-tion | Lan-guage | Presentation Title | Speaker | Affiliation (with URL) | Media |

|---|---|---|---|---|---|

| 8:00-8:45 | 45min | E&J | Registration | Administration | — |

| 8:45-9:00 | 15min | E&J | Opening Remarks | RISC-V Alliance Japan | VIdeo |

| 9:00-9:25 | 25min | J | Opening: Japan’s Digital Industry Strategy and Semiconductor Fab (Invited Lecture) | SAITO Hisashi | Deputy Director, IT industry division, Commerce and Information Policy Bureau, Ministry Economy, Trade and Industry | |

| 9:25-10:05 | 40min | E | Keynote Speech: The Future of RISC-V and RISC-V AI (Invited Lecture) | Jim Keller | CEO, Tenstorrent (Canada) | |

| 10:05-10:35 | 30min | – | Break | Administration | — |

| 10:35-11:15 | 40min | J | SoC Functional Visibility –Introduction to Tessent Embedded Analytics | Hiroshi Fujimatsu | Technology Solutions Sales, Field Application Engineer, Siemens (Germany) | |

| 11:15-11:40 | 25min | J | Imagination’s RISC-V CPU Product overview | Haruhiko Ogawa | Staff Field Application Engineer, Imagination Technologies (UK) | Video |

| 11:40-12:05 | 25min | J | Green Hills Software for Safe and Secure RISC-V systems | Ryan Kojima | Green Hills Software GK, Embedded Software Consultant / Green Hills Software GK | |

| 12:05-12:30 | 25min | J | Introduction of MCU with GD32 RISC-V | Kenji Kageyama | Marketing Director, GigaDevice Japan / GigaDevice (China) | |

| 12:30-12:55 | 25min | J | RISC-V Debugging and Perfect Trace Solutions | Takahito Kagawa | Sales Manager, Lauterbach Japan Ltd. / Lauterbach (Germany) | |

| 12:55-13:00 | 5min | J | New large-scale call for international joint research! ASPIRE(Adopting Sustainable Partnerships for Innovative Research Ecosystem) | TomohiroTeraminami | Japan Science and Technology Agency / Senior Program Coordinator (Japan) | |

| 13:00-14:00 | 60min | – | Lunch: Payment in the in-house Metro cafeteria is by cash or transportation card for non-students | Administration | — |

| 14:00-14:40 | 40min | J | Imperas RISC-V design support tools that support the foundation of RISC-V technology | Yukiharu Sato | Senior Product Sales, Sales division, eSOL TRINITY Co., Ltd. / Imperas (UK) | |

| 14:40-15:05 | 25min | E | Espressif RiscV developments – towards multicore and more standardization | Jeroen Domburg, senior software manager, Espressif (China) | Video |

| 15:05-15:45 | 40min | J | Custom compute – Architect your ambition | Takaaki Akashi | Country Manager, Japan , Codasip (Germany) | |

| 15:45-16:10 | 25min | J | RISC-V Application Case Study by Akaria | Tomoaki Katano | NSITEXE,Inc. (Japan) | |

| 16:10-16:35 | 25min | J | Why IAR compiler is vital for open source ISA:RISC-V business? | Hiroki Akaboshi |Technical team, FAE, IAR Systems K.K.(Japan) | |

| 16:35-16:50 | 15min | E | Bootstrapping an Open Source Silicon Ecosystem: a retrospective Google for Academics | Johan Euphrosine | Google Japan, Developer Relations Engineer | Video |

| 16:50-17:40 | 50min | – | Networking & Break : Prepare snacks. | Administration | — |

| 17:40-18:20 | 40min | E | High Performance Leadership in Action: Powering Next Generation Data Center and Automotive Architectures | Greg Favor | Co-Founder and Chief Technology Officer, Ventana Micro Systems(USA) | |

| 18:20-18:45 | 25min | E | Enable IoT Future with Next Generation Processor | HIROAKI SATO | Triton Corporation, Senior Advisor | Andes Technology (Taiwan) | |

| 18:45-19:10 | 25min | E | Tenstorrent Data Center AI Accelerator: Current Generation and Next Generation | David Bennett | CCO, Tenstorrent | |

| 19:10-19:50 | 40min | E&J | Transforming the Tech Landscape: Generative AI’s Role in Shaping the Future of RISC-V, AI Accelerators, Power Efficiency, and Environmental Sustainability | Moderator/Shumpei Kawasaki, Jim Keller | CEO, Tenstorrent(Canada), Wei Fu | Red Hat (China), Omar Hassen | Ventana Micro Systems(USA) | Video |

| 19:50-20:05 | 15min | E | Recent RISC-V Architecture Situation | Mark Himelstein | CTO, RISC-V International | |

| 20:05-20:15 | 10min | E&J | Closing Remarks | RISC-V Association | — |

| 20:15-21:00 | 45min | – | Cleanup | Administration | — |

Date and Time : June 20 (Tue) , 2023 13:00 ‐ 19:00 JST (UTC+9)

at Ito International Research Center B2 floor: Event Space / Special Presentation Venue

Schedule in Japan Standard Time (UTC+9)

Please note that the speakers and contents are tentative and subject to change, and the schedule may change on the day of the event due to various reasons.

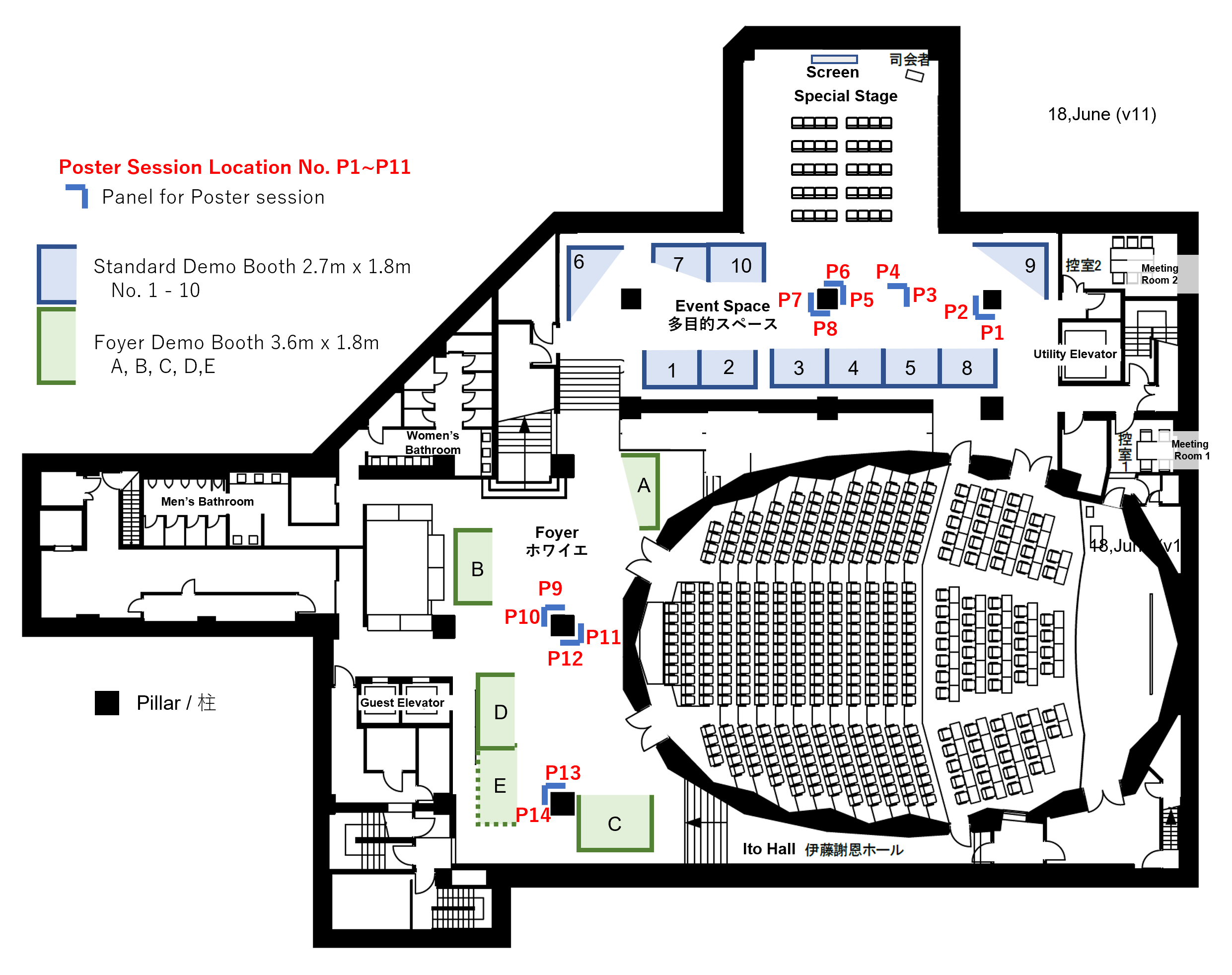

Poster session Poster display location: Location No. P1-P11

Please refer the Figure of “[ 3 ] RISC-V Booth (Foyer of Ito Hall, Event Space)”

| Start-End | Dura-tion | Lan-guage | Presentation Title | Speaker | Affiliation | Poster Slide | Location No. |

|---|---|---|---|---|---|---|

| 13:00-13:10 | 10min | EJ | Poster Session Introduction | Hideharu Amano | Keio University | — | – |

| 13:10-13:17 | 7min | J | Design example of a triple modular redundancy ALU and a register file for RISC-V processors | Masato Isobe | Faculty of Engineering, Okayama University, student |

P1 | |

| 13:17-13:24 | 7min | E | A Multi-SATA FPGA Implementation for Quantum Computer Simulator Qulacs | Kaijie Wei | Keio University, Project Assistant Professor | P2 | |

| 13:24-13:31 | 7min | E | An Introduction to the Arch Linux RISC-V Port and Related Works | Ruizhe Pan | Chair Intern, Programming Language and Compiler Technology Lab, Institute of Software at the Chinese Academy of Sciences (China) | P3 | |

| 13:31-13:38 | 7min | E | Performance Survey of Current Gate Model Quantum Processors | Yikai Mao | PhD Student, Kondo Lab, Keio University | P4 | |

| 13:38-13:45 | 7min | J | SLMLET, a SoC with mixed RISC-V core, high-speed IF, and eFPGA | YANAI Yosuke | Keio University Graduate School of Science and Technology, Amano-lab | P5 | |

| 13:45-13:52 | 7min | J | Field Testing and Evaluation Environment for FPGA-equipped RISC-V SoC SLMLET | Takuya Kojima | Graduate School of Information Science and Technology, University of Tokyo | P6 | |

| 13:52-13:59 | 7min | J | SHAMIKO: Development of a New Open-source Evaluation Board Designed for Side-channel Analysis (Invited Call for Action) | Presenter : Ryotaro Ohara | Third year of a Phd’s program, Graduate School of System Informatics, Kobe University, Co-author : Haruka Hirata | First year of a Ph.D program at The University of Electro-Communications. | P7 | |

| 13:59-14:06 | 7min | E | IoT-oriented RISC-V-based SOTB-65nm System-on-Chip Implementations | Khai-Duy Nguyen | Department of Computer and Network Engineering, The University of Electro-Communications | P8 | |

| 14:06-14:13 | 7min | E | An Effective Way to Perform Correlation Power Analysis Attack on Cryptographic RISC-V SoC | Tran Thai Ha | Ph.D. Student, Department of Computer and Network Engineering, The University of Electro-Communications | P9 | |

| 14:13-14:20 | 7min | J | Vector Register Sharing Mechanism: High Bandwidth Data Transfer Method for Accelerators | Michiya Kato | Department of Electrical Engineering and Computer Science, Graduate School of Engineering, Tokyo University of Agriculture and Technology | P10 | |

| 14:20-14:27 | 7min | EJ | Optimizing Efficiency in Extended SIMD RISC-V-Based Architectures through Minimization of Idle Computational Cores | NISHIMURA Masaru | Graduate School of Science and Technology, University of Tsukuba | P11 | |

| 14:27-15:00 | 3min | EJ | Poster Session Transiton (Location No. : P1 to P11) | Hideharu Amano | Keio University | — | – |

| 14:30- 15:00 | 30min | EJ | Poster session discussion @ poster location | Poster Session Presenter | — | – |

| 15:00-15:40 | 40min | EJ | Bootstrapping an Open Source Silicon Ecosystem: a retrospective Google for Academics | Johan Euphrosine | Google Japan, Developer Relations Engineer Ryo Shigeta | Google Japan | Video | |

| 15:40-15:55 | 15min | E | Intermission | Intermission | — | – |

| 15:55-16:35 | 40min | E | ChipIgnite Program: Even 8-year-old children can turn FPGA designs into chips (Invited Lecture) | Mohamed Kassem | CTO, eFabless.com (USA) | Video | |

| 16:35-17:00 | 25min | J | The Journey of Two Novice LSI Enthusiasts: Tape-Out of CPU+RAM in Just One Month | Kazuhide Uchiyama | University of Electro-Communications, Information Security Program Yuki Azuma | University of Tsukuba | ||

| 17:00-17:50 | 50min | E | Lowering Costs & Barriers to Chip Design | Mehdi Saligane | University of Michigan / Michigan Engineering, Electrical Engineering and Computer Science Department (EECS) | ||

| 17:50-18:05 | 15min | – | Intermission | Intermission | — | – |

| 18:05-18:20 | 15min | J | Introduction to the Embedded Systems Association and technical projects in the RISC-V Working Group | Tomohisa Kohiyama | JASA RISC-V WG, Chief (Japan) | ||

| 18:20-19:00 | 40min | E | Linux on RISC-V — status update from firmware to distros (Invited Lecture) | Wei Fu | Red Hat (China) | ||

| 19:00-19:40 | 40min | E | RuyiSDK: Get ready for 1 million RISC-V software developers | Wei Wu | ISCAS, Director of PLCT Lab (China) | ||

RISC-V Booth (Venue)

[ 3 ] RISC-V Booth (Foyer of Ito Hall, Event Space)

at Ito International Research Center B2 floor: Foyer of Ito Hall, Event Space

Date and Time : June 20 (Tue) , 2023 12:00 ‐ 19:00 JST (UTC+9)

The Booth a provides opportunities for visitors to “see” demos and ask questions

RISC-V Booth ” A ~ E ” Foyer of Ito Hall

B2 floor of Ito International Research Center , The University of Tokyo

Please note that the speakers and contents are tentative and subject to change, and the schedule may change on the day of the event due to various reasons.

| Booth # | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| A | June 20 (Tue) 12:00 – 19:00 | Product Introduction by Codasip | Codasip | |

| B | June 20 (Tue) 12:00 – 19:00 | Product Introduction by Lauterbach | Lauterbach / Lauterbach Japan Ltd. | |

| C | June 20 (Tue) 12:00 – 19:00 | Tool Product Introduction by Siemens EDA | Siemens EDA | |

| D | June 20 (Tue) 12:00 – 19:00 | Open Silicon Pavilion | Google | eFabless | ISHI-Kai | |

| E | June 20 (Tue) 12:00 – 19:00 | Ventana Micro Systems Inc. | Ventana Micro Systems Inc. |

RISC-V Booth ” No. 1 ~ 10 ” Event Space and Foyer of Ito Hall

B2 floor of Ito International Research Center , The University of Tokyo

Please note that the speakers and contents are tentative and subject to change, and the schedule may change on the day of the event due to various reasons.

| Booth # | Time | Lang | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|---|

| 1 | June 20 (Tue) 12:00 – 19:00 | Product Introduction by Andes PurePlay IP | Andes Technology Corporation | ||

| 2 | June 20 (Tue) 12:00 – 19:00 | Product Introduction by GigaDevice | GigaDevice Semiconductor Inc. | ||

| 3 | June 20 (Tue) 12:00 – 19:00 | Product and Rvfpga Introduction by Imagination | Imagination Technologies K.K. | ||

| 4 | June 20 (Tue) 12:00 – 19:00 | Product Introduction by Imperas Software | Imperas Software Ltd. (UK) / eSOL Trinity (Japan) | ||

| 5 | June 20 (Tue) 12:00 – 19:00 | Product Introduction by NSITEXE | NSITEXE,Inc. | ||

| 6 | June 20 (Tue) 12:00 – 19:00 | VeriSIlicon RISC-V hardware platform | VeriSilicon Microelectronics Co., Ltd. | ||

| 7 | June 20 (Tue) 12:00 – 19:00 | RISC-V: New innovation opens the door to the future | Future Corporation | ||

| 8 | June 20 (Tue) 12:00 – 19:00 | DTS Insight | DTS Insight | ||

| 9 | June 20 (Tue) 12:00 – 19:00 | Tenstorrent Data Center AI Accelerator Products | Tenstorrent Japan | ||

| 10 | June 20 (Tue) 12:00 – 19:00 | Kyoto Microcomputer | Kyoto Microcomputer |

Online RISC-V Booth

The Online Booth provides opportunities for visitors to “see” demos and ask questions through RISC-V a live streaming.

Clicking on the content / title of the Booth will take you to the online RISC-V Booth website.

Schedule in Japan Standard Time (UTC+9) Subject to change

Please note that the speakers and contents are tentative and subject to change, and the schedule may change on the day of the event due to various reasons.

| Lang | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|

| J | IAR Systems Online Booth page | IAR Systems K.K. | |

| J | Siemens EDA Online Booth page | Siemens EDA |

Go to RISC-V Related Publication page