The Road Ahead Mark Himelstein CTO, RISC-V International

RISC-V Day Japan 2023 June 2023

#### **Overview**

- RISC-V Overview

- Why People Use RISC-V

- Embedded

- Portability

- Embedded & Real Time ISA Extensions

- SW ecosystem

# The definition of open computing is **RISC-V**

RISC-V°

RISC-V is the most prolific and open Instruction Set Architecture in history

- RISC-V is inevitable

- RISC-V enables the best processors

- RISC-V is rapidly building the strongest ecosystem

# 10s of Billions of RISC-V cores deployed for profit!

### **Open Source HW or Open Standard?**

- We are officially an Open Standard HW ISA Architecture

- We are an Open Standard that works heavily with Open Source upstream projects (LINUX, GCC, LLVM, etc.)

- We don't do reference implementations

- Our work product are specifications with support from Golden Models and Basic Tests

#### Unlike Open Source Software ...

- Proprietary Custom Extensions are Encouraged and Welcome

- Products don't just include the ISA, they can do custom implementations/extensions of/to the ISA

- Copyleft is a non-sequitur

- No restrictions on how the specification can be used

Only restrictions on branding

## Why RISC-V?

- Flexibility

- Cost

- Ecosystem

- Our position in History

- EDA Renaissance

- Pride of Ownership

### Portability

- Unified common standard and a robust Software Ecosystem

- A robust economy around systems and software is reliant on portability

- Application & Runtime Software

- Profiles

- API (e.g. POSIX)

- Operation Systems

- Platforms

- Supervisor Execution Environment (SEE)

- Profiles

# **Profiles**

| Bases                                                            | Public Name 1                                                                                                                      |                                                                                                        |                                                                                 | Name 2                                                              | Future              |                                                                                                                       |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| RV32I<br>RV64I                                                   | RVI[20]<br><sup>RVI20U32</sup><br>RVI20U64<br>RV32I<br>RV64I                                                                       | RVA20<br><sup>RVA20U64</sup><br>RVA20S64<br>RV64I                                                      | RVA22<br><sup>RVA22U64</sup><br>RVA22S64<br>RV64I                               | RVA23<br>RV64I                                                      |                     |                                                                                                                       |

| Load<br>Store<br>Jumps<br>Branches<br>Add<br>Subtract<br>Logical | On years<br>released, this<br>only has a<br>Mandatory<br>Base<br>All other<br>compatible<br>ratified<br>extensions are<br>optional | Mul/Div<br>Atomics<br>Compressed<br>Float<br>Double<br>Priv 1.11<br>MemRegions<br>Fences<br>VirtualMem | Vector<br>Bitmanip<br>Scalar Crypto<br>FP16<br>Priv 1.12<br>Hypervisor<br>Cache | Vector Crypto<br>PtrMasking<br>BFloat16<br>Zcompressed<br>Priv 1.13 | Android<br>Features | More profile types:<br>RVB, RVM<br>RV128<br>Matrix Ops<br>SPMP/IOPMP<br>CFI<br>CHERI<br>GPU<br>48/64 bit instructions |

| MAJOR                                                            |                                                                                                                                    |                                                                                                        |                                                                                 |                                                                     | <br>MAJOR           |                                                                                                                       |

- Only a subset of extensions are listed above and it is not an exhaustive list

- Some extensions may be optional or non-profile in one profile and be mandatory in another

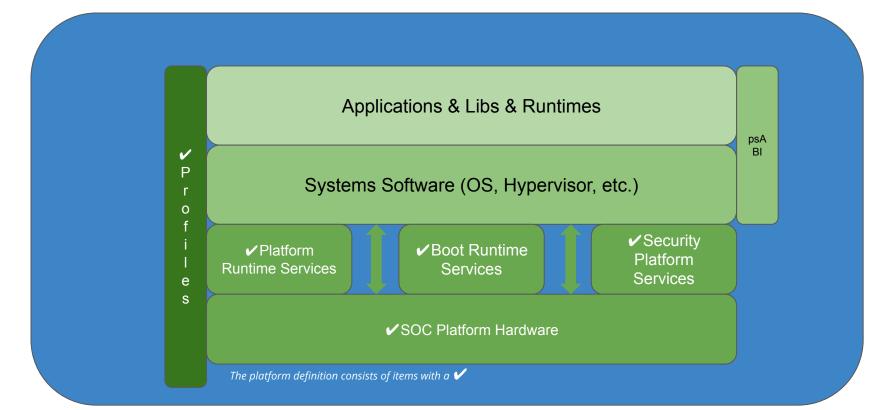

#### Platforms

#### ISA Extensions Targeted at Embedded and Real Time

- Extensions: Fast Interrupts, Compressed Instructions (plus Zc\*), FP in integer registers, Multiply without divide, Vector for embedded, S mode timer access, S mode w/o MMU, Wait on reservation set, Pause Hint, Physical Memory Protection, Scalar Crypto

- Profile Families: RVI, RVB, RVM

- Bases: RV32I, RV32E, RV64E

#### What We Have Done This Year

- Ratified ISA Specifications

- Profiles, Code Size Reduction

- Ratified Fast Tracks

- Counters, Total Store Ordering, RV32E/RV64E, Non Temporal Hints

- Documentation

- Unpriv in Asciidoc, Asciidoc Priv draft

- New Task Groups & Special Interest Groups

- Debug, Trace, and Performance Monitoring (DTPM) TG , Graphics SIG, RISC-V Common Software Interface (RVM-CSI) SIG, Vector (SIMD) SIG, Control Transfer Records TG

## What's Coming Soon?

- Profiles

- RVA23, RVI23, RVB23, RVM23, BOD committee on comprehensive ACTs & Certification

- Platforms

- Portability for Systems Software (PRS, BRS, Platform Security, SOC HW, Profiles)

- ISA

- Advanced Interrupts, QOS Register Interface, Control Transfer Records, Debug, Fast Interrupts, I/D Synch, Priv 1.13, Shadow Stacks/Landing Pads, Vector Crypto, Vector FP16

- ISA Fast Tracks

- CAS, BFloat16, Conditional Ops, Counter Mode FIltering, HW PTE A/D, Maybe Ops, Additional Scalar FP, Counter Delegation,

- Non-ISA

- IOMMU, Confidential VM extension, IOPMP, Nexus Trace,

- Documentation

- Full time RVI DOC Architect/Writer approved

- BOD committee on dev experience (content & UX)

- Glossary, Navigation

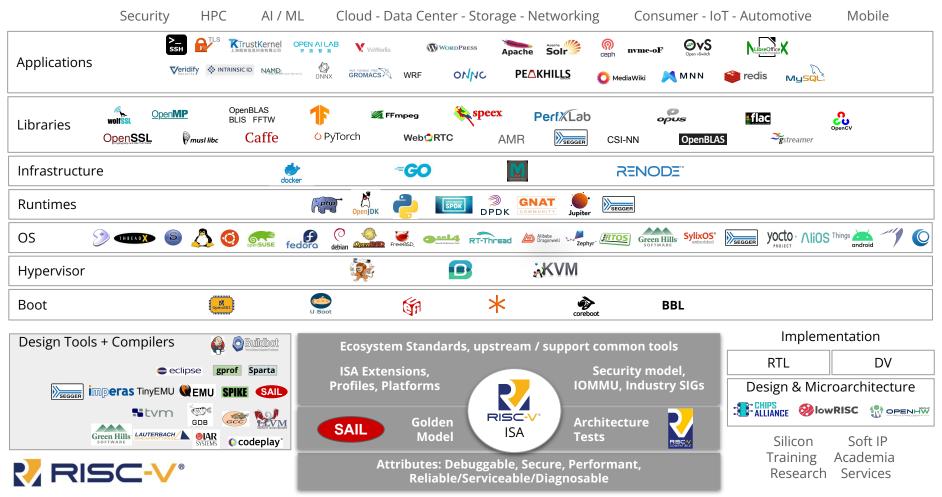

#### Software Ecosystem

## This is our number one priority

#### Accelerating the Rich RISC-V Ecosystem

#### Android

- Google Support

- Tier 1

- Google Requirements

- Engagement with RISC-V

- Likely in 2024

- Much is underway

- Lifetime can be 10 years

#### **RT-Thread on RISC-V**

#### RV32

- HiFive1

- RV32M1\_VEG

A

- HPM6750

- GD32VF103

- AB32VG1

- CH32V103

- CH32V208

- CH32V307

- CH569

- BL808

- ESP32C3

#### RV64

- K210

- Allwinner D1

- Allwinner D1S

- QEUME/RISCV64

VIRT

#### **RV-Core**

- bumblebee

- QingKeV3

- QingKeV4

- E310

- cv32e40p

- Andes D45

- SMART-EVB for T-Head CPU E9xx Series

- PicoRV32

#### Software Ecosystem Resources

- Foundational Software Status for each extensions

- Draft <u>spreadsheet</u> of software on RISC-V status (140+ being tracked)

- Hired RVI Software Ecosystem Director. First task is a comprehensive one stop clearinghouse of RISC-V commercial and open source software status

- RISC-V Ecosystem Landscape

- RISC-V <u>Exchange</u> (100s)

- A new Linux Foundation Project named RISE to accelerate open source software development on RISC-V

# Join RISC-V

Change the World!

## Questions