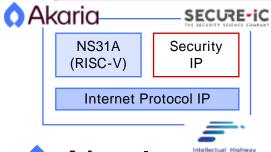

## "Akaria" による RISC-V応用事例

## NSITEXE(エヌエスアイテクス)紹介

- 半導体IP、半導体ソリューションカンパニー

- 2017年 (株)デンソーの出資により設立

- 世界各地から集まった60名以上のエンジニアが在籍

- 組込みシステム向け高効率半導体IPを開発

- 2020年1月 最初のDFP製品DR1000Cをリリース

- 2021年7月 RISC-V汎用CPU NS31Aをリリース

- AIエンジン、セキュリティサブシステム等のIP開発

#### • エコシステム

- 自動運転等の自動車向けシステム、ロボティクス、FA、IoT等、 次世代を担う様々な分野のアプリケーションをサポート

- HW/SW、デザインメソドロジ、ソリューション各社との幅広 いパートナーシップ

## 組込システムの背景

#### 制御方式のトレンド遷移

Open Loop Cont. Controlled by mechanism & Analog

Feedback Cont. Compensation control by parameters

Adaptive Cont. **Model Predictive** Control

$\mathscr{D}$

Connected

Full Model Cont. Distributed parallel **Processing**

#### プロセッサ要求の高度化・多様化:

Edge-Al, MPC\*, Security

\*MPC: Model Predictive Control

#### 組込みシステムのジレンマ

プロセッサ要求の多様化により個別最適 が追い付かない、一方で個別の強みは確 保したい

共通化と個別最適のバランス確保

#### Computing requirement:

Flexible Processing Flexible = Scalability + Versatility

**Power Efficiency**

**Real-time Computing**

**Functional Safety**

Conventional Individual operation Preventive safety/

Hearing

自動車システムの遷移

Composite decision-making algorithm Hands-on

Hands-off Eyes-off

Mind-off

Automation

スマートファクトリーの遷移

**Automation**

IoT

**CPS**

Akaria

2023 NSITEXE. All rights reserved

# © 2023 NSITEXE. All rights reserved

### **Akaria Overview**

**Power Efficiency**

MPC: Model Predictive Control

Optimized accelerators for MCU and own

solvers realize high accuracy control

systems

#### **Akaria Security Solution**

**Functional Safety**

- Software Security Platform

- · Root of Trust Platform

- · Network Security Platform

#### Akaria Software

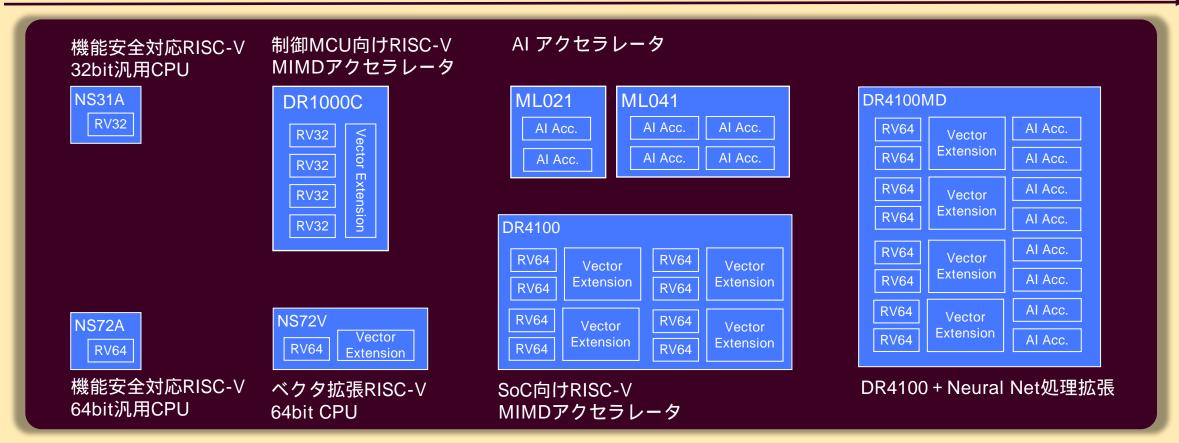

### Akaria Processor Products

#### Performance/Size

用途毎に柔軟な構成をサポート

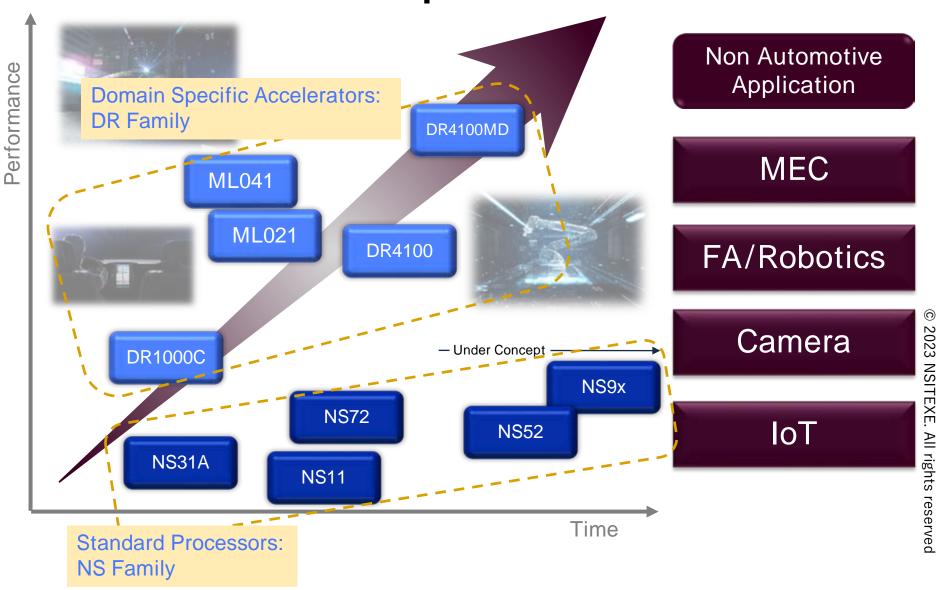

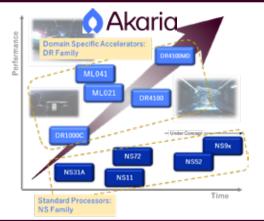

## Akaria Processor Roadmap

Automotive Application

MaaS

AD/ADAS

IVI

Control

- 64-bit performance embedded core

- For Mid-high Rich-OS capable range

- 10+-stage, Out-of-Order Superscalar multi-core

NS

- 32-bit performance embedded core

- For Mid-high controller and rich-OS capable range

- 10-stage, Superscalar multi-core

NS

- 32-bit efficient embedded core

- For Mid-range micro controller

- 4-stage single issue, FPU optional

- 32-bit PPA optimized embedded core

- For Low-end micro controller

- 2 4-stage short pipeline

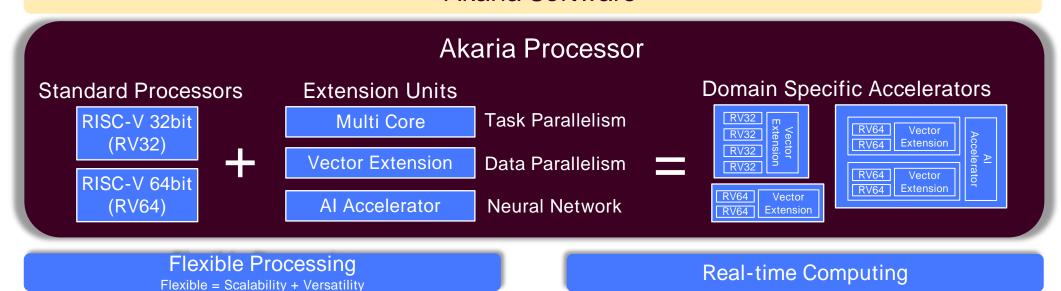

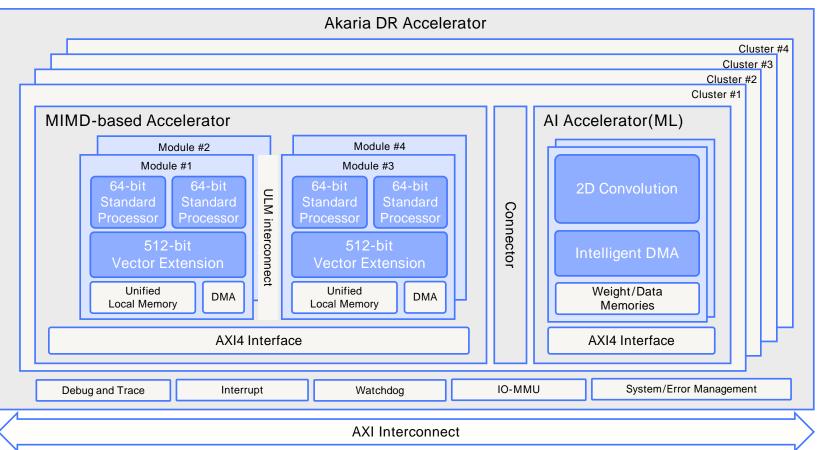

## Akaria Domain Specific Accelerator: DR Family

Standard Processors

RISC-V 32bit (RV32)

RISC-V 64bit (RV64)

**Extension Units** Multi Core Task Parallelism **Vector Extension** Data Parallelism **Neural Network** Al Accelerator

制御MCU向け MIMDアクセラレータ : DR1000 Series

SoC向け MIMDアクセラレータ : DR4000 Series

AIアクセラレータ : ML Series

### 組込みシステム界に広がるAkariaワールド

#### **Automotive**

#### ゾーン/ドメインECU向け車両制御用MCU RH850 U2BにDR1000C搭載

https://www.renesas.com/jp/ja/products/microcon trollers-microprocessors/rh850-automotivemcus/rh850u2b-zonedomain-and-vehicle-motionmicrocontroller

#### 世界初ベクトルプロセッサ搭載RISC-Vプロセッ サとしてASIL-D Readyの認証取得

#### モビリティサービスを支えるセキュリティ技術

Akaria

#### SDVを支える次世代ソフト開発環境

世界初、次世代プロ セッサIP向けの包括 的なソフト開発環境 の実現に成功

#### 誰でもどこでもRISC-V!

無償評価環境を提供

https://www.nsitexe.com/en/akaria /processor/ns/akaria-ns-bsp/

#### Non Automotive

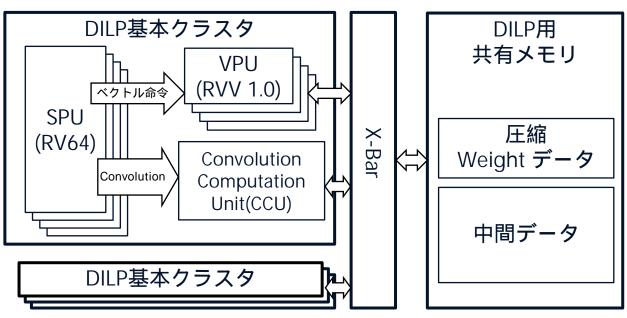

#### 日本代表!世界最高峰のAI電力効率を実現

NEDO事業において、次世代組 ~ み込みシステム向けAIプロセッ サー(DILP)を開発し、世界最高 クラスとなる15TOPS/Wを達成

#### モデル予測制御で産業機器のデファクトへ

#### 北米・欧州・アジア世界各地で導入評価中

車載通信機器、AIチップ、 HPC向け、宇宙産業等各 地・各分野へ展開

Power Efficiency

**Functional Safety**

Real-time Computing

## Akaria NS BSP(Board Support Package)の公開

### Akaria NS Familyの評価環境を無償公開

- FPGA bitstream

- ・評価ソフトウェア

- Toolchain(gcc, libc, openocd, etc)

https://www.nsitexe.com/en/akaria/processor/ns/akaria-ns-bsp/

FPGA開発ボード(Arty-A7)とJTAGデバッガ(Flyswatter2等)があれば誰でもNS Familyを評価できる

## NS31A評価キット

#### 萩原エレクトロニクス社製 Akaria NS31A評価キット

#### Entry Kitの特徴【発売中】

- 手軽に安価に評価を開始したいお客様へのけの評価キット

- 評価ボード(FPGAにNS31A書き込み済)、JTAGエミュレータ、ケーブル一式、開発ツール、サンプルソフト、ドキュメントなど評価に必要な一式をバンドル(NS31A基本パッケージPlus)

- 動作環境 (Windows PC(メモリ 8GB以上)上のVirtualBoxでubuntu環境で操作)

#### Appli Kitの特徴【発売予定】

- 株式会社ロッキー製キャリアボード上に、Akaria NS31Aおよび独自にインテグレートした周辺IP搭載

- モータ制御を想定したモータドライバボード

- 開発ツール、サンプルプログラム、ドキュメント類付属

- 動作環境 Windows PC(メモリ 8GB以上) 上のVirtualBox上のUbuntu環境で操作

- FPGA、IOボード、ソフトウエアのカスタマイズ可(オプションサービスとして提供)

#### イメージをカタチに!

#### NSITEXE NS31A (32bit RISC-V) 評価キット

Akaria NS31Aは、NSITEXE社が開発・販売する32bit RISC-V IP製品です。 萩原エレクトロニクスは、このIPを評価するための評価キット2種類を販売します

#### SITEXE 社製 RISC V IP 製品

- RISC-V 32bit General Purpose Tiny Core

申報用金をなりの各種産業用金に確立く対応

- ISO26262:2018 ASIL D compliant SEcoC IP

- ユーザの機能安全対応を幅広くサポパートナー企業と連携した

- バートナー企業と連携した RISC-V ソリューション ・ツールチェーン、デバッグ環境、 ソフトウェア各社と連携

#### NS31A Core

- NSJ TA COPE - ABJULTOP イン構造とTIGO V会介セットを採用した 32 ピットプロセッセ - Dranch Terget Dafer (DTD) とよる引致予測機構 - 2 回転の特殊リード (M-mode)

- Single-Precision Floating

- Instruction Cooke (C)

- Instruction Local Memory(LM) / Carta Local Memory (DLM) **思り込み信息ユニット** (CU) / システル(MIXニートト (DMJ) / Denic **Sel** Link (DRG

- Functional Sefety

アドン2000 Holle Telephone Organization

RAM アータを保護する RAM ECC

パスを保護する Ram Detection and Correction

パスを保護する Data Core Lock Stop

ア語音を指する Data Core Lock Stop

#### 灰原エレクトロニクス株式会社 新事業開発本

nttps://hagiwera-ele.com/ 〒461 - 0008 名古屋市東区東桜 2-3-1 高荷パークビ/

HASVANA DÍU ERFEN-AFAD FREGRESSERFE, EA PRENIMERARIDONARIA BUDGOSTA GERMENTA

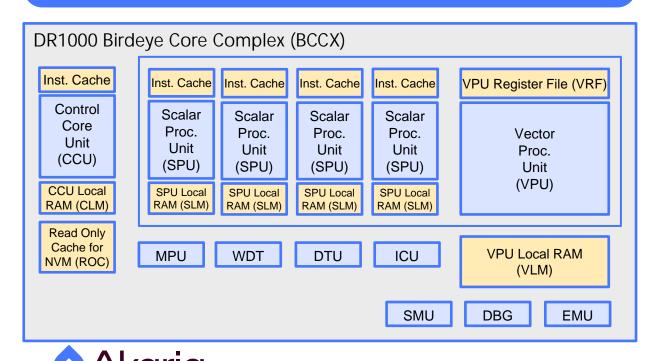

## 制御MCU向けアクセラレータ: DR1000C

### ベクトル演算器搭載MIMD型プロセッサ

ベクトル演算器とマルチスレッド実行にて、 実装面積あたりの高い演算処理効率を達成 車載制御マイコンの高負荷処理をオフロード

#### 主要機能

- 大規模レジスタファイル付 低遅延型 512bit ベクトル演算パイプライン

- 高効率ベクトル演算用 マルチスレッド スカラユニット + ベクトルユニット

- 将来の高負荷アプリケーションに備えた コアクラスタリングに対応

- "RISC-V Vector extension" 拡張命令セット

- バンク分割式 ベクトルレジスタファイル (VRF)

- ◆2階層 命令キャッシュ (L1 命令キャッシュ + ROC)

- 高バンド幅 ベクトル演算用 ローカルメモリ (VLM)

- ●低レイテンシ NVM ROM インタフェース (ROM バスマスタ)

- •システムバスインタフェース(システムバスマスタ)

- ●DMA機能付きデータ転送ユニット (DTU)

- ハードウェアスレッド制御用コントロールコア (CCU)

- 複数ソースからの割り込み制御対応

- ●内部・外部割込み制御用コントローラ(ICU)

- ●システムクロック・リセット制御 (SMU)

- エラー制御・挿入・記録 (EMU)

- JTAG デバッグ / トレース インタフェース (DBG)

- ASIL D レベル対応のハードウェア機能安全メカニズム

SGS-TÜV社のASIL D Ready認証を取得

© 2023 NSITEXE. All rights reserve

# © 2023 NSITEXE. All rights reserved

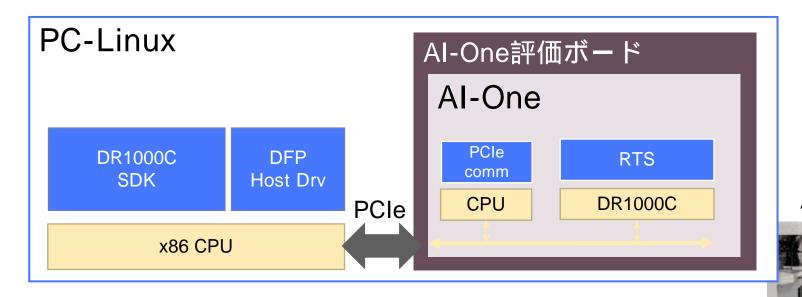

## DR1000C評価環境

AI-One評価ボード搭載PCに開発環境を構築した状態で用意

AiOne Board搭載PC

AI-One: NEDO主体で取組む「AIチップ開発加速のためのイノベー ション推進事業」での実証チップ

https://www.aist.go.jp/aist\_j/press\_release/pr2022/pr20220322/pr20220322.html

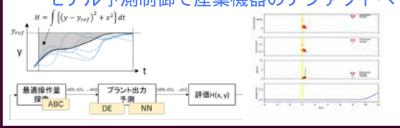

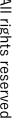

## Akaria MPC (Model Predictive Control) Solution

プラントモデル(差分方程式/NN)とメタヒューリスティックソルバを利用し、 最適制御を実現、演算負荷に対してはDR1000Cでアクセラレート

#### モデル予測制御(MPC):

制御対象(プラント)の出力を予測、予測された出力が制御目的をどの程度満たすかを評価関数Hで記述し、Hが最適となる操作量をリアルタイムで探索する制御手法

#### MPCの従来課題:

モデル、ソルバの演算負荷が高く、

マイコンへの実装が困難

C model

評価関数

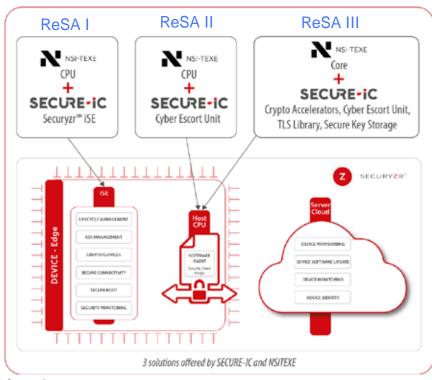

## Akaria Security Solution: ReSA

- 耐タンパ

- 異常検知

- セキュアブート

- 鍵管理 真贋判定・ライフサイクル管理

- 高速暗号化 FIPS140-2 CAVP Level2

- OTA

- ネットワークセキュリティ

- 車載グレード ISO26262 ASIL-D

(Revolutional Security Architecture)

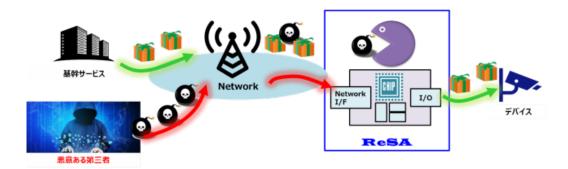

#### 製品名"ReSA"

- DDoS攻撃や不正パケットを「捕食」し安全な通信のみを通過させる

- 不正利用や攻撃を、**ネットワーク層で防御**する

【課題】PC・スマートフォンだけでなく、IoTセンサーや監視カメラ等の低スペックデバイスへの対策が必要

#### ネットワークセキュリティ関連処理の完全ハードウェア化

ネットワーク第5層までの高負荷処理を**完全ハードウェア化**を変ない・安全・堅牢な通信を、低消費電力で実現

# © 2023 NSITEXE. All rights reserved

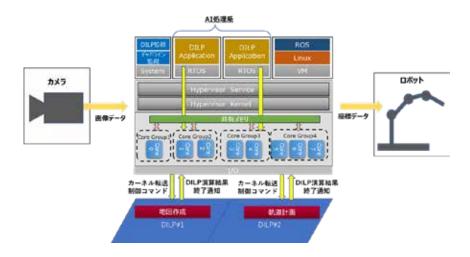

### 次世代組込みシステム向けAI処理プロセッサ

~ NN処理で世界最高クラスの電力効率15TOPS/Wを達成~

SPU: Scalar Processing Unit VPU: Vector Processing Unit

ロボット制御環境で実証実験

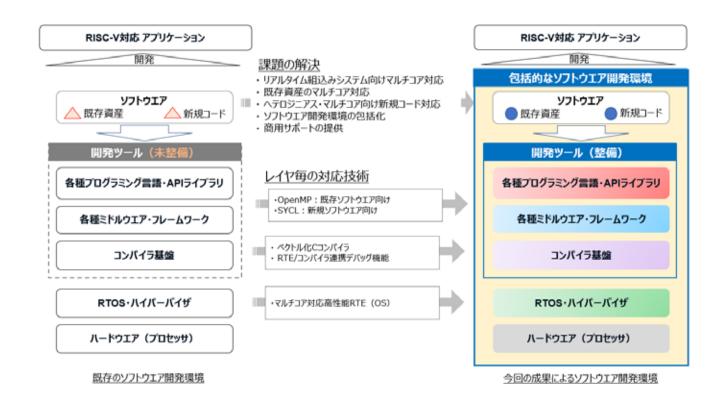

### RISC-V向けの包括的なソフト開発環境の実現

## ~マルチコア対応高性能ランタイム環境において処理時間を平均71%短縮~

eSOL × KMC × OTSL × NSITEXE

#### 世界初!

ヘテロジニアス環境下でのRISC-V向けOS、各種並列化フレームワーク、コンパイラ基盤、並列プログラム処理のための開発ツールを組み合わせた包括的なソフト開発環境を実現

#### 高い性能と開発支援機能を実現

ヘテロジニアスなマルチコア対応の高性能RTE で、POSIX標準のAPIにおける処理時間を従来 比平均71%短縮

## Summary

#### NSITEXE Akaria

- 組込システムを幅広く支えるプロセッサソリューション

- Flexible Processing, Power Efficiency, Real-time Computing, Functional Safetyの強み

#### Akaria Processor

- Standard Processors NS Family: RISC-V汎用CPU

- Domain Specific Accelerator DR Family: RISC-V V

ExtensionやAIアクセラレータを活用し用途毎に最適化

#### AkariaによるRISC-V応用事例

- 機能安全対応RISC-V、無償の評価環境も公開

- ソフト開発環境も充実させ、AI, Securityを活用したソリューション

Contact: https://www.nsitexe.com / support@nsitexe.co.jp

Embedded solutions. Fundamental Impact