Nov. 5 − 6, 2020 / 9:00 − 18:00 Japan Standard Time (GMT+9)

Supporters

Schedule

DAY 1 : November 5th (Thursday), 2020 / 9:00 〜 18:00 JST (GMT+9)

DAY 2 : November 6th (Friday), 2020 / 9:00 〜 18:00 JST (GMT+9)

How to accept questions and information on the Demo Booth

- Join the RISC-V Association’s Slack! This Slack is a place for exchanging information related to RISC-V, and a RISC-V Day Tokyo 2020 question reception channel is prepared for each session. By all means, Join us in Slack, RISC-V Association, deepen your interaction with the participants, and enjoy Day Tokyo even more!

- Questions for sessions are accepted at RISC-V Association Slack or on Twitter. If you have any questions on a presentation, please tweet with the hashtag below the presentation title of the program below. In addition to the session’s hashtag, adding tags #riscv_day and #risc_v will help those who are looking for RISC-V related information. Thank you for your cooperation.

- We are offering “ Virtual Demo Booth ” as a new attempt to hold online. Interactive demos and Q & A sessions through live streams, as well as individual “private talks (Emails)”, are possible. Please experience this new attempt at RISC-V Day Tokyo!

DAY 1 : November 5th (Thursday), 2020 / 9:00 〜 18:00 JST (GMT+9)

Schedule Japan Standard Time (GMT+9) Subject to change

| Time | Lang | Presentation Title | Speaker | Affiliation | Media |

|---|---|---|---|---|

| 9:30 | E/J | Program Guide (Presentation and Virtual Booth System) | Eiji Kasahara | Esperanto Technologies | |

| 10:10 | E | RISC-V Unconstrained: Technology, Opportunity, and Community | Calista Redmond | RISC-V International (Switzerland) | |

| 11:00 | J | Latest overview of SiFive RISC-V and user case study by ArchiTek | Atsushi Ishii, Yoshito Kondo, Shuichi Takada | SiFive (USA), DTS Insight (Japan), Architek (Japan) | PDF1 |

| 11:50 | J | AI Chip Design Center | Kunio Uchiyama | Chief Executive Officer, AI Chip Design Center, NEDO Project, AIST | |

| 12:20 | E | Linux and Firmware on RISC-V (RV64 status, RV32 Fedora bootstrap status, and Linux platform spec update) | Wei Fu | Senior Software Engineer, Platform Enablement, Red Hat Software (Beijing) Co.,Ltd. | |

| 12:50 | E | Vanguard – the first Open Source RISC-V SoC project in Vietnam | VLSI Technology Page, Quynh Do-ngoc* and Quan Nguyen-hung | |

| 13:20 | J | RISC-V Dedicated High-Performance Computers for Designing Medicine | Makoto Taiji*, RIKEN Center for Biosystems Dynamics Research | Video |

| 13:50 | J | ASIP Designer: RISC-V ISA Processor Implementation and Its Extensions | Mitsuru Tomono | Application Engineer, Solution Group, Nihon Synopsys G.K. (USA) | |

| 14:20 | J | Advanced SIMD architecture derived by applying RISC-V architecture | Yamaguchi Yoshiki*, Tan Yuxi, and Abdelhamid Riadh Ben | University of Tsukuba | Video |

| 14:50 | E | TEE Hardware for RISC-V Implementation | Ckristian Duran*, Trong-Thuc Hoang, Cong-Kha Pham | UEC, Akira Tsukamoto, Kuniyasu Suzaki | AIST, TRASIO | |

| 15:20 | J | About translation work of “digital circuit design starting with Chisel” | Seiji Muneto | IBM Japan, Chisel Study Group (Japan) | |

| 15:40 | E | Digital Design in Chisel | Martin Schoeberl*, Associate Professor, Technical University of Denmark | |

| 16:10 | J | Chisel & Diplomacy Deep Dive | @msyksphinz | Author of FPGA development diary | |

| 16:30 | E | Research and Development Activities on RISC-V and its Applications for IoTs | Duy-Hieu Bui* | SISLAB, University of Engineering and Technology, Vietnam National University, and Xuan-Tu Tran | Vietnam National University, Hanoi(Vietnam) | |

| 17:00 | J | Why Should We Use RISC-V as an Educational Model Processor? | Hideharu Amano* | Keio University | |

| 17:20 | E | RVfpga: the first complete Computer Architecture course based on RISC-V | Guanyang He | Imagination Technology (UK) | |

| 17:40 | E | ”University Programmes” – We Have all Heard the Phrase, but What Does it Actually Mean? | Robert Owen, etal. | Imagination Technologies | Video |

| 18:00 | E | Ending Remarks | RISC-V Association Japan | Video |

DAY 2 : November 6th (Friday), 2020 / 9:00 〜 18:00 JST (GMT+9)

Schedule Japan Standard Time (GMT+9) Subject to change

| Time | Lang | Presentation Title | Speaker | Affiliation | Media |

|---|---|---|---|---|

| 9:00 | E | Getting started with PolarFire SoC | Tim Morin | Technical Fellow Marketing, FPGA Business Unit, Microchips | |

| 9:30 | E | SiFive’s HiFive Unmatched RISC-V Linux PC mini-ITX Form Factor Board | Yunsup Lee | CTO SiFive (USA) | |

| 10:00 | E | ASA RISC-V Processor Optimized For Edge AI/ML, Security, Smart IoT Sensors | Islam Md Ashraful* | ASAMicros(USA) | |

| 10:30 | E | Esperanto’s Verification Methodology for a RISC-V Machine Learning SoC | Shankar Jayaratnam, Raymond Tang | Esperanto Technologies, Inc. (USA) | |

| 11:00 | J | Introducing the GD32VF103 RISC-V based MCU | Ken Kageyama / GigaDevice Japan Co., Ltd. (China) | |

| 11:30 | J | Activities on RISC-V at JASA and introduction of ET & IoT Digital 2020 | Shozo Takeoka | General Manager of Technology Headquarters and Chairman of Applied Technology Research Committee, Embedded Systems Technology Association (Japan) | |

| 12:00 | J | NVIDIA-ARM Merger, Renesas RISC-V Adoption, and Open Source Hardware Movement in Background | Shumpei Kawasaki | SH Consulting K.K. | |

| 12:30 | E | AI: Scale from Edge to Server with RISC-V and Linux | Florian Wohlrab*, Head of Sales for EMEA and Japan, Andes Technology | |

| 13:00 | E | Stay Ahead with the Latest Advances in RISC-V Development Tools | Shawn Prestridge | US FAE Team Leader, IAR Systems (Sweden) | |

| 13:30 | J | Real-time OS “VxWorks” RISC-V Support | Shiro Kiuchi | Sr. Engineer, Wind River KK | |

| 14:00 | J | AdaCore RISC-V Ada / C Language Software Development Tool: Model base, Formal Verification, Functional Safety Standards Support | Nobuo Fukutoku | IT Access Co., Ltd. for Adacore (France) | |

| 14:30 | E | Software Ecosystem for SCRx family of the RISC-V compatible CPU (tentative title) | Alexander Redkin | Syntacore (Russia) | |

| 15:00 | E | Enabling Fully Open Source And Continuous Integration-Driven Flows in ASIC and FPGA Development(tentative title) | Michael Gielda | CHIPS Alliance (USA) | |

| 15:30 | E | RISC-V processor IP product line | Alexander Kozlov | CloudBear (Russia) | |

| 16:00 | EJ | Imagination Technologies Presentation | Kristof Beets | Senior Director, Product Management Imagination Technologies Limited., Hiroyuki Uchimura | CEO, Imagination Technologies K.K. (UK) | |

| 16:50 | EJ | Preview of RISC-V Association Japan Projects in 2021 | RISC-V Association Japan |

Virtual Demo Booth

The virtual demo booth provides opportunities for visitors to “see” demos and ask questions through a live streaming.

Schedule Japan Standard Time (GMT+9) Subject to change

Picture: Scenes from RISC-V Day Tokyo 2019

Japanese Translation of Digital Design with Chisel

Chisel Study Group is working on publishing a Japanese translation of Martin Schoeberl’s Chisel book (http://www.imm.dtu.dk/~masca/chisel-book.html). The source released on Github (free, scheduled for https://github.com/chisel-jp/chisel-book). The PDF can be downloaded at the above URL. RISC-V Association is also planning to sell paper version in near future. Previously RISC-V Association arranged to have the following RISC-V publications into Japanese “RISC-V Reader” and “Computer Architecture: Quantitative Approach.”

2020 Backgrounds

The theme of RISC-V Day Tokyo Online 2020 is “RISC-V research, development, technology, and market next to 5G mobile, storage, wearable, and automotive applications.”

The University of California, Berkeley proposed a new innovation in computer architecture called RISC (Reduced Instruction Set Architecture) in the 1980s, which had a great influence on the computer trend. RISC-V (Risk Five) was asked by the University of California in 2015. RISC-V provides new models for (1) processor architecture, (2) implementation design, and (3) intellectual property distribution, and has a great impact on business styles such as IBM, ARM, and MIPS in the first year of the decree. I did.

When developing the first computer in 1945, one of the main inventors, John von Neumann, abandoned his patent application because he thought it was best to share an open instruction set and an open implementation. All competitors ran into their own computer architecture (instruction set architecture, ISA = Instruction Set Architecture. Since then, each company has developed, manufactured and used its own instruction set architecture (ISA = Instruction Set Architecture). Monopolizing rights, many of the antitrust cases on computers were related to ISA. Recently, one ISA devised by John von Neumann 75 years ago was shared throughout the industry, and software was shared in the industry. Attempts are being made to realize the shared ideal. This is RISC-V.

RISC-V is a new business model that supports (1) open instruction set, (2) open source processor, (3) open source software, (4) open source EDA tool, etc., and (5) user extension instructions. We presented a new intellectual property model. This new model will not only be adopted by many companies today, but will also affect companies adopting the exclusive models of IBM Power, MIPS and ARM, and in 2019, these companies will also have business models and knowledge. A series of changes were made to the financial model.

RISC-V is led by the RISC-V Foundation, which is based in Geneva, Switzerland. Domestic and overseas semiconductor companies have already begun trial production, mass production, and shipment of RISC-V. In the first year of Reiwa, the number of member companies in the world exceeded 360, the number of processor IPs developed according to the RISC-V standard reached 56, 21 types of SoC platform IPs, and 9 types of SoCs were produced. It was.

In the first year of Reiwa, RISC-V (Risk Five) has definitely evolved from R & D to the product distribution phase. Revitalized research at universities, research institutes and companies. Includes, open source EDA tools, open source IP, formal verification, security, and other areas.

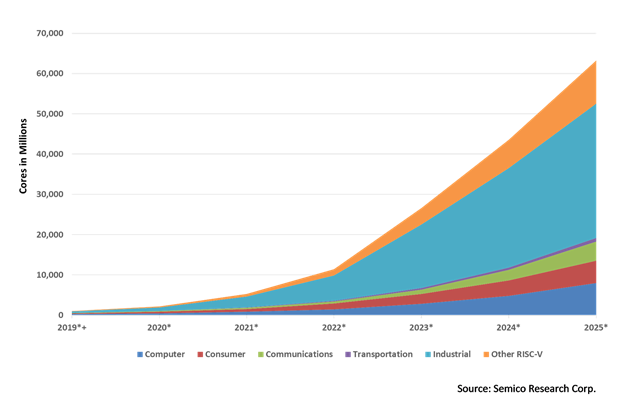

Was made at the end of last year. Semiconductor research firm Semico expects to ship 62.4 billion RISC-Vs by 2025. RISC-V adopted for Samsung “5G” mobile 2020 model. is.

2019 RISC-V Top 10 News

1. Semico Research Inc. expects to ship 62.4 billion RISC-Vs by 2025: On November 25, Semico Research Inc. announced a forecast of the future market size of RISC-V. Semico Research predicts that RISC-V can be expected to grow at a compound annual growth rate (CAGR) of 146.2% from 2018 to 2025. Semico predicts that 62.4 billion RISC-V CPU cores will be shipped by 2025. The largest segment is for industrial use, with 16.7 billion cores.

Semico analyzed data from 25 applications in five major end markets (computer, consumer, telecommunications, transportation, and industry) and estimated estimated shipment volumes for four application product categories. According to Semico’s calculations, the annual growth rate forecast based on shipment volume from 2018 to 2025 shows that the annual growth rate of RISC-V CPU core shipments is the highest for applied products that emerge from “5G” wireless. Therefore, we expect the telecommunications application sector to achieve the highest growth rate in RISC-V shipments.

There is a great deal of interest in computerization in the automotive industry, with increasing adoption of CPU-based systems for safety, in-car experience, driver assistance, and wireless communication, and RISC-V, which has the second highest annual growth rate in transportation equipment. It is a CPU core application segment. The figure below shows a graph of the annual shipment figures of RISC-V cores announced by Semico Research (exhibitor: Semico Research Inc. Japanese translation: RISC-V Association).

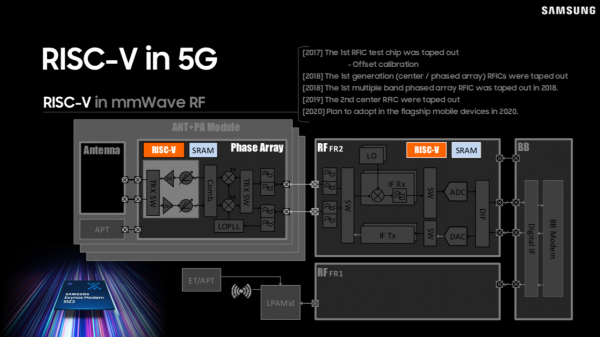

2. RISC-V installed in Samsung’s 2020 “5G” mobile device Shipping: On December 20, Samsung Electronics Korea announced that the “5G” communication module using RISC-V will be the 2020 model Samsung “5G” mobile. Announced that it will be installed in phones and future in-vehicle “5G” network devices.

Even in Japan, “5G” communication, which is scheduled to be put into practical use in 2020, is 100 times faster than current mobile communication. You can download a 2-hour movie in 3 seconds, and it is already being adopted in some overseas markets. Samsung Electronics Korea is actively developing smartphones compatible with the next-generation communication standard “5G”, and RISC-V is used in the core products of major companies by nVidia’s AI chipset Western. Following Digital’s storage chipset, “5G” communications are large in quantity and have a big impact.

Samsung Electronics prototyped a “5G” RF IC test chip with RISC-V in 2017. In 2018, we made a prototype of “5G” multi-band phased array RF IC for antenna + PA module with RISC-V, and in 2019, we made a prototype of central “5G” RF IC with RISC-V, and accumulated technological development for this announcement. It is said that it was done.

Below is a block diagram of the “5G” chipset on one of the slides Samsung Electronics announced at the RISC-V Summit on December 20th.

3. With the support of IBM (Redhat) and Google, RISC-V will be ported to RISC-V with languages for microservices and OS software.

On December 10th, IBM (Redhat) demonstrated in the United States “Kubanetes” for RISC-V, which facilitates system management and detection and improves service scalability. Porting work of the “Kubanetes” system written in Go language developed by Google to RISC-V is also underway.

In June, the president of SiFive, a RISC-V company that raised 12 billion yen, at the University of California Spinout, declared that “the RISC-V server will be put into commercial operation within five years.” With this declaration, the stakeholder open source community has begun to stand up and work together. RISC-V will be upgraded to a Devian portable architecture in 2019. Ports of container technology, microservices technology, etc. that guarantee resilience, operational rate, and scalability are being implemented in RISC-V one after another.

The foundation of the RISC-V instruction set (ISA) is language support. DARPA funding for LLVM / Clang, a new compiler for RISC-V, began in January, and the foundation for extensive language support across Clang, OpenCL, and Rust has begun. In May, the GNU Debugger (GDB) “GDB 8.3” implemented RISC-V support for the C, C ++, Ada, Go, and Rust languages. On September 3, Google announced that the server system language Go developed by Google will officially support RISC-V in the next release version 1.14.

Instead of traditional collocations and virtual machines, server applications are shifting to highly abstract services such as microservices. The movement to make RISC-V compatible with this is steadily progressing as a pre-commercial stage. Software such as system operation infrastructure service (IaaS), application execution environment service (PaaS), and micro function service (FaaS) are also being ported to RISC-V one after another. In the full-featured serverless RISC-V implementation of OpenFaaS, pull requests are being merged upstream.

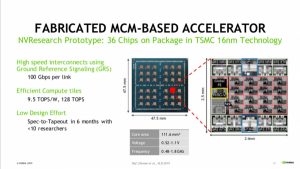

4. NVIDIA develops ultra-low power consumption deep learning inference accelerator with RISC-V, achieving 9.5T operation / watt

Since 2016, NVIDIA has adopted RISC-V as a control microcomputer for GPU products. On September 4, high-performance computing company NVIDIA disclosed future uses of RISC-V. NVIDIA prototyped an RC18 test chip with a high power inference engine using the TSMC standard 16 nanometer process and measured 9.5T operation / watt. We have developed a chip that can infer at about 13.5 watts using RISC-V as the input / output core of the inference accelerator component.

Hyperscalers and cloud builders that are actively built by Google and Amazon require the inference engine to have a comprehensive power performance that integrates a certain power profile and performance. NVIDIA’s RC18 is a high-performance accelerator for deep learning inference workloads with a high energy efficiency design and 128 trillion operations per second at 13.5W. It has an element (PE) with eight vector cross product (MAC) units on one chip, and input and output functions are performed by a single master core with a RISC-V instruction set architecture.

The RC18 Accelerator can replace the current generation “NVIDIA Deep Learning Accelerator” (NVDLA = Nvidia Deep Learning Accelerator). With a design very similar to NVDLA, we have developed a chip for software tool development such as vector width, number of vector units, buffer array size, and method of staging operations by loop parallelization. NVIDIA chose RISC-V because of its open ISA, scalability, flexibility, and no royalties.

To find a way to build an accelerator with good power performance, slow down the clock speed enough to allow the core that can use the lowest voltage on the chip to follow, and run all the clocks to provide power and timing margins. I investigated where to waste. Processing elements (Pes) consisting of minute regions of the chip are locally logically generated and calculated by individual clocks that track the power supply. In order to measure the margin, the frequency is raised to the limit where the calculation can be performed, and when it falls, it is decelerated again.

Because signals entering and exiting the small region need to be synchronized, NVIDIA has developed a fast synchronization circuit that synchronizes in half a clock cycle. In a conventional system, it takes 5 to 6 clock cycles to move from one clock domain to another. This synchronization technology won the Best Paper Award at the International Symposium on Asynchronous Circuits and Systems (ASYNC) in May.

The figure below shows NVIDIA’s RC18 deep learning inference accelerator using RISC-V. 36 chips (2.4mm x 2.5mm) are mounted on a multi-chip module (MCM = 47.5mm x 47.5mm). 16 high-speed interconnects with 100 Gbps communication speed and 16 high-power performance calculation tiles are manufactured by TSMC 16nm technology, and these 36 chips are mounted on MCM and driven from 0.52V to 1.1V, 0.48-1.8GHz. It works with. With a power efficiency of 9.5 tella operations / watt, one unit delivers 128 tella operations per second.

Below is one of the slides that NVIDIA unveiled at Hot Chips at Stanford University on August 18th.

5. RISC-V Chips and IPs are available from flash microcomputers to server applications RISC-V

(1) Chinese-owned GigaDevice company starts selling RISC-V flash microcomputer: On August 23, Chinese-owned GigaDevice company (GigaDevice), which supplies NOR flash memory, announced the RISC-V flash microcomputer. The company was known for its growing market share as a cheaper alternative to procuring the GD32 series of STM32 compatible ARM MCUs from ST. The newly added RISC-V-based flash microcontroller GD32V series is 15% faster than the company’s ARM M core. Power consumption is reduced by 50%. The GD32V series has its own unique expansion of peripheral functions, regardless of compatibility with STM, and has more peripheral functions than the GD32 series.

(2) Expansion of SiFive’s RISC-V IP lineup: In addition to the 32-bit microcomputer core E3 and 64-bit Linux executable core U5 shipped from 2017, SiFive has a lineup in the first year of Reiwa. Has been greatly expanded. E2 / E3 / E7: Microcomputer, edge computing, AI, IoT application 32-bit embedded application, S2 / S5 / S7: Storage, AR / VR, machine learning application 64-bit embedded application, U5 / U7 / U8: Linux, data We have expanded the three series of center and 64-bit application processor series for network baseband. In addition to the above, SiFive has also developed an out-of-order U8 core with a 7nm process, which means that processor cores compatible with all ARM classes are available.

(3) Expansion of RISC-V IP lineup by Andes Technology: Compared to the ARM M series, the N22 “Bumblebee” IP core of the RISC-V architecture has (1) CoreMark / MHz, (2) DMIPS / MHz, (3). Andes has announced that it outperforms the CSiBe Code Size benchmark. Andes has (1) A series: application processor (compatible with ARM A) (2) N series: embedded processor class (compatible with ARM M) (3) network processor D series (compatible with ARM R) and 3 We have two lineups. (1) and (2) support both 32-bit and 64-bit. The A series covers not only edge applications but also server applications.

(4) Birth of an organization that standardizes RISC-V system profiles such as “Chips Alliance” and FOSSi:

From March, activities to integrate IP of peripheral functions such as “CHIPS Alliance” (CHIPS Alliance), FOSS, FOSSi, etc. created in the Linux Foundation under the auspices of Google etc. to make it easier to make systems with RISC-V started. You can easily create an 8-core high-performance system with open source. It is now possible to make chip products with high added value using open source technology.

6. Globalization of the organization to globally provide regional-neutral and open RISC-V technology: In the field of Chinese smartphones, we announced that Huawei Ascend 910 was developed by ARM with 7nm process as the world’s strongest AI processor. , Has announced a two-CPU strategy that the chip is also designed for RISC-V. With the background of trade blocking, RISC-V may be on par with ARM (currently 99% of the world market share) even in smartphone systems.

In March, the RISC-V Foundation merged with the Linux Foundation so that blocking trade would not hinder the development of RISC-V. In collaboration with European Free and Open Source Software (FOSS), Free and Open Source Silicon (FOSSi), and other organizations, it was transforming from a mere US organization to a global organization. FOSS and FOSSi, like Yin and Yang, appear to be developed as bloody monolithic activities that are rooted and integrated through ISA. RISC-V provided one of the central factors in FOSS / FOSSi activity originating in Europe. FOSS and FOSSi activities will make a big difference to the industry in the coming years.

7. Promote digital semiconductor research with RISC-V

(1) Carbon nanotube RISC-V manufacturing process: MIT last week used a RISC-V CPU made of carbon nanotube (CNT) MOSFETs using standard CMOS manufacturing equipment and materials and processes in a commercial CMOS manufacturing plant. Was announced. It’s a RISC-V processor that uses carbon nanotube FETs. It is said to be 10 times more energy efficient.

(2) Open source EDA tools are rapidly expanding from RISC-V to vehicles: A new generation of open source EDA tools is being developed with RISC-V as a vehicle. The new book “Digital Design with Chisel” has been officially published, and a new design flow is being established. EDA tools such as the traditional Verilator have become widely used, and their reliability, performance, and functionality have improved dramatically. Open source EDA tools have been acorns for the past 20 years, but this year a strong contender has emerged. Methodology such as co-simulation can now be realized with open source.

Due to its simplicity, the FPGA tool Yosys + nexpnr runs tremendously faster than commercial FPGA tools. The FPGA automatic placement and routing tool nextpnr consists of a device-dependent part and a general processing part, and can be mapped to any FPGA by rewriting the device-dependent part. Currently, Lattice ICE40 and ECP5 and Xilinx FPGAs are supported. Open source tools enable a wide variety of use cases. You can take advantage of the “partial configuration feature” to try test vectors faster during the validation phase. Formal verification is also becoming more important. Unintended logic, such as hardware Trojans, can be inserted at multiple points in the development process, which can be detected by formal verification.

(3) NVIDIA’s efforts to open source: nvidia is leading NVDLA, an initiative to develop an open source machine learning ecosystem. Both NVDLA Deep Learning Inference Compiler and NVDLA RTL have been opened.

(4) IBM’s efforts to open source: The world of servers and CPUs is steadily changing. IBM has made the Power architecture free. I got used to RISC-V and made the Power CPU instruction set free. Open sourced RTL. An OpenPower softcore called Microwatt was also announced. A small Open POWER ISA softcore written in VHDL 2008, aimed at being simple and easy to understand. IBM has open sourced the Power Instruction Set Architecture (ISA), “Definition used by developers to ensure that hardware and software work together on Power,” as well as the Power ISA softcore. The reference implementation of OpenCAPI interconnect technology and OMI memory interface technology will also be open sourced.

(5) Efforts to open source MIPS: RISC-V is also a model for the movement of Wave Computing to develop MIPS Open.

8. Increase in RISC-V Foundation members and event attendance

As of the end of 2019, the number of RISC-V Foundation member companies reached 460. 1650 people registered for the RISC-V Summit 2019 held in California on December 10-12. RISC-V Day Tokyo 2019 held in Tokyo on September 30th was held by Hitachi, Ltd., Toyota Motor Corporation, AdaCore (USA), Andes Technology (Taiwan), Codasip (Czech Republic), and FUJISOFT. , IAR Systems (Sweden), NSI-TEXE (Denso Co., Ltd. subsidiary), Rambus (US), SiFive (US), Syntacore (Russia), Ubiquitous AI Corporation, ultraSoC (UK), SH Consulting 360 people registered and held the event at the Hitachi Baba Memorial Hall in the Kokubunji Central Research Institute of Hitachi, Ltd.

9. The outline of RISC-V “Shield” and “World ID” that surpasses the security of ARM Trust Zones is announced

(1) RISC-V in the US DARPA Security Research Project: The RISC-V architecture is obligatory for security chip projects that use US DARPA grants. Due to this effect, RISC-V is often used in security architecture research. It is estimated that more than 20 types of security IPs using RISC-V have been developed all over the world.

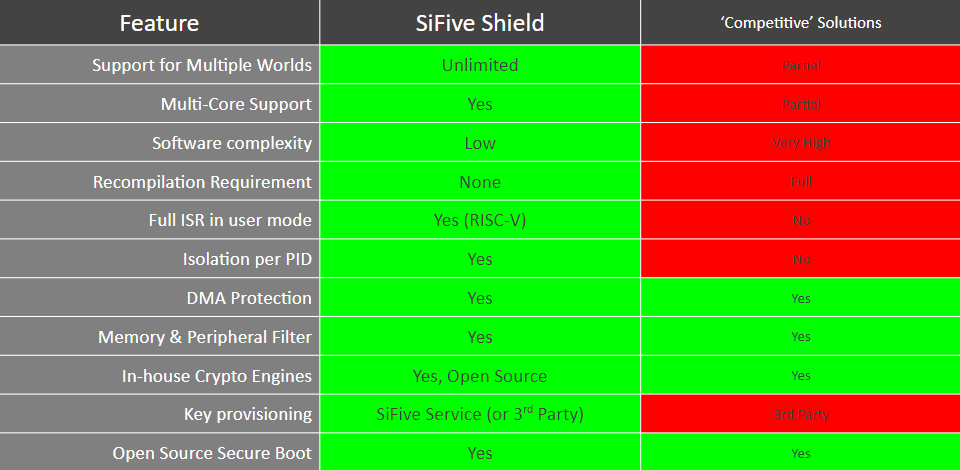

(3) SiFive “Shield” “World ID”: On October 23, SiFive of the United States released the mechanism of “Shield” and “World ID” to counter ARM “Trust Zone”. In addition, he declared that he would release an open standard and open source implementation so that anyone could use them. ARM “Trust Zone” is a processor security method announced by ARM Limited in 2003. “World ID” has organized the functions of the “Trust Zone” of the ARM A series into a system that surpasses the “Trust Zone” on all scales. It also implements trust execution environment (TEE) support, root of trust support, and key management support.

The figure below shows a functional comparison of “Shield” and “World ID” with competitors from the materials released by SiFive. Exhibitor: SiFive website, Japanese translation: RISC-V Association

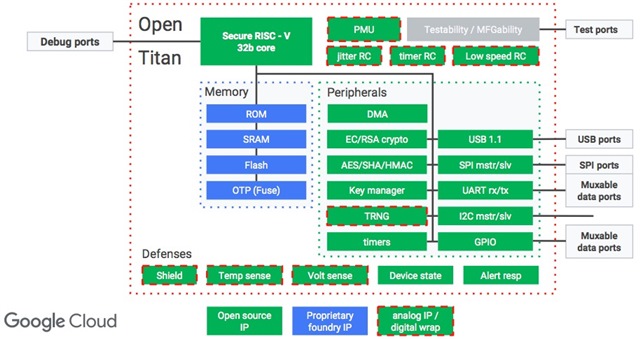

10. “Open Titan” by Google to open source its route of trust technology: On October 14, Google will open source to develop a secure chip design for use in data centers and infrastructure. We have launched an initiative called, and announced that we are partnering with several companies and nonprofits. Open source security can provide stronger security by independently validating, enhancing, and building designs. Apps running on your computer can be infected with a virus. The most important counter-cyber security is at the firmware and chip level. “Open Titan” allows many people to improve their initial design and enhance the security of their implementation.

The project is named after Google’s own Titan chip, which checks boots with known roots of trust used in data centers and Pixel Phones to ensure that the firmware hasn’t been tampered with. The cryptographic element used for validation is called the Root of Trust (RoT) and is the heart of the “Open Titan” project. The figure below shows the block diagram of “Open Titan”. Exhibitor: Google announced, Japanese translation: RISC-V Association

Cloud References

RISC-V Association website: http://riscv.or.jp/

Facebook: https://www.facebook.com/Risc-V-Association-102528267773380/

Twitter: @riscv_a

RISC-V Tokyo Meetup site: https://www.meetup.com/RISC-V-Group-Tokyo/