Nov. 16 (Wed.) – 18 (Fri.), 2022

Supporter

Supporter : EdgeTech+ 2022

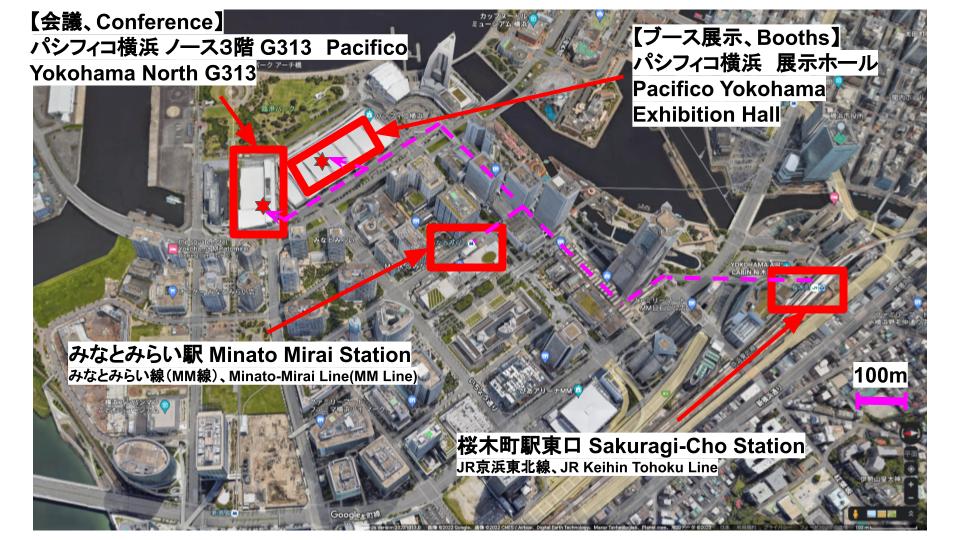

EdgeTech+ 2022 Registration : RISC-V Days Tokyo 2022 Autumn On the first day, November 16 (Wed), the second day, November 17 (Thu) , and the third day, November 18 (Fri) presentations will be held at Pacifico Yokohama NORTH HALL (BUILDING NEXT TO the EXHIBITION HALL of EdgeTech+ 2022). PLEASE ALSO CHECK EdgeTech+ 2022 and YOU MAY Register for EdgeTech+ 2022. We look forward to your participation in this opportunity!

THE RISC-V Days Tokyo 2022 Autumn CONFERENCE WILL BE AT PACIFICO YOKOHAMA NORTH HALL 3RD FLOOR G313

THE RISC-V PAVILION WILL BE AT PACIFICO YOKOHAMA EXHIBITION HALL 1F

Nov. 16 (Wed.) – 18 (Fri.), 2022 10:00 – 17:00 (Until 18:00 on Thu, 17) JST(UTC+9)

RISC-V Days Tokyo2022 Autumn Conference

RISC-V Days Tokyo is Japan’s largest physical and online RISC-V event. On the first day, November 16 (Wed), the second day, November 17 (Thu) , and the third day, November 18 (Fri) presentations will be held at Pacifico Yokohama North 3rd Floor G313 Meeting Room , and the presentation will be broadcast live. There will be a “RISC-V Pavilion” at Pacifico Yokohama (inside the EdgeTech+ 2022 Exhibition) for three days. There will also be a “Online RISC-V Pavilion” for three days. RISC-V Days Tokyo aims to bring together leading RISC-V technologies and products, key persons and engineers, and to provide business opportunities for product recognition, collaboration among companies, technology exchange and information gathering. We look forward to your participation in this opportunity!

RISC-V Days Tokyo2022 Autumn Schedule

DAY 1 Conference : Nov 16 (Wed), 2022 / 10:30 〜 17:00 JST (UTC+9)

Pacifico Yokohama North 3rd Floor G313 Meeting Room with live online broadcasting

DAY 2 Conference : Nov 17 (Thu), 2022 / 10:30 〜 17:00 JST (UTC+9)

Pacifico Yokohama North 3rd Floor G313 Meeting Room with live online broadcasting

DAY 3 Conference : Nov 18 (Fri), 2022 / 10:30 〜 17:00 JST (UTC+9)

Pacifico Yokohama North 3rd Floor G313 Meeting Room with live online broadcasting

Online RISC-V Pavilion Information

- We are offering “ Online RISC-V Pavilion ” as a new attempt to hold online. Interactive demos and Q & A sessions through live streams, as well as individual “private talks (Emails)”, are possible. Please experience this new attempt at RISC-V Day Tokyo!

Asking Questions and Making Comments

- We are fortunate that this is an online live conference. Our interaction is limited by the 15 second delay in mass transmission to the audience. So questions are raised via chat system of one form or another.

- If you have any questions or comments about each lecture, please join RISC-V Association Slack enter the slack on #days-tokyo-2022-autumn channel !

- The reason why we recommend slack is due to the time constraints our presenters will not answer all questions or our Q&A staff sometimes miss your question. We do not like to see your brilliant question to be wasted.

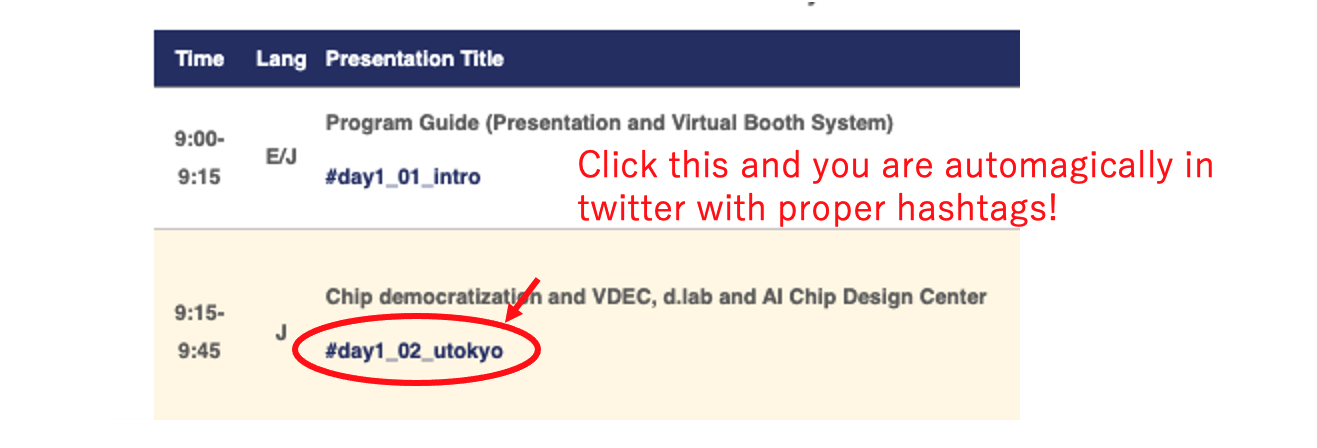

- Ideally please cut and paste presentation hashtag in the timetable below in your Slack entry. This way the presenter will be able to positively identify that your question is for him to answer and likely provide answer via Slack.

- If you still want to ask questions on Twitter, please tweet with the hashtag attached under the presentation title of the program below. Actually programmer set up a magic. Note question via Twitter will not LAST like Slack but last for some time. Presenter is likely to answer your question here too.

- You can also enter comments on Vimeo if you have logged in as a registered Vimeo user. Beware questions via Vimeo are very very ephemeral and often forgotten after the even tis over.

DAY 1 Conference : Nov 16 (Wed), 2022 / 10:30 〜 17:00 JST (UTC+9)

Pacifico Yokohama North 3rd Floor G313 Conference Room with live broadcasting

Schedule in Japan Standard Time (UTC+9)

Please note that the speakers and contents are tentative and subject to change, and the schedule may change on the day of the event due to various reasons.

| Time | Lang | Presentation Title | Speaker | Affiliation | Media |

|---|---|---|---|---|

| 10:30-10:40 | E/J | Day 1 Welcome speech Overall explanation of RISC-V Days EdgeTech+ Venue, RISC-V Pavilion, Online RISC-V Pavilion Introduction | RISC-V Alliance Japan | |

| 10:40-11:10 | J | This lecture will be held on November 17th (Thursday) 13:00-13:30. 3D object detection from image and point cloud data when driving a car using RISC-V | ||

| 11:10-12:00 | E | Keynote: Open-source silicon ecosystem: New Shuttles, PDK releases and tools | Aaron Cunningham | Google, Open Source Hardware Program Manager Tim (mithro) Ansel | Software Engineer, Google LLC, Mountain View, California USA | Video |

| 12:00-12:50 | Lunch Break: Online RISC-V Pavilion Introduction | |||

| 12:50-13:20 | E | Lowering Barriers to chip design using OpenFASoC | Mehdi Saligane | University of Michigan / Michigan Engineering, Electrical Engineering and Computer Science Department (EECS) | Video |

| 13:20-14:30 | J | Panel discussion: A new era of chip design, prototyping, manufacturing, and design human resource education aimed at open source semiconductors led by DARPA and Google | Hideharu Amano (Moderator) | Keio University, Makoto Ikeda | University of Tokyo, Jun-ichi Okamura | Invited Senior Researcher, National Institute of Advanced Industrial Science and Technology(AIST) Johan Euphrosine | Google, Takahiro Kitayama | KAMAKE no SUSUME Corp., CEO Shumpei Kawasaki | RISC-V Alliance Japan | Video |

| 14:30-15:20 | J | Current Status and Future Direction of Semiconductor and Digital Industry Strategy | Hisashi Saito | Deputy Director, IT industry division, Commerce and Information Policy Bureau, Ministry Economy, Trade and Industry | Video |

| 15:20-15:40 | JE | Intermission: RISC-V pavilion, online RISC-V pavilion introduction | ||

| 15:40-16:00 | J | Google for Academics | Ryo Shigeta | Google, University Relations Program Manager | Video |

| 16:00-16:40 | E/J | Google Open Source Silicon Ecosystem (Demonstration of RISC-V implementation by OpenLane development environment using high-level description language) | Johan Euphrosine | Google Japan, Hardware Toolchains team, Developer Relations Engineer | Video |

| 16:40-16:50 | E/J | DAY 1 Closing Remarks | RISC-V Alliance Japan |

DAY 2 Conference : Nov 17 (Thu), 2022 / 10:30 〜 17:00 JST (UTC+9) JST (UTC + 9)

Pacifico Yokohama North 3rd Floor G313 Conference Room with live broadcasting

Schedule in Japan Standard Time (UTC+9)

Please note that the speakers and contents are tentative and subject to change, and the schedule may change on the day of the event due to various reasons.

| Time | Lang | Presentation Title | Speaker | Affiliation | Media |

|---|---|---|---|---|

| 10:30-10:40 | E/J | Conference Q&A and Online RISC-V Pavilion Guide | RISC-V Alliance Japan

| |

| 10:40-11:30 | E | RISC-V is truly everywhere: from Automotive to Enterprise | Calista Redmond | CEO RISC-V International | Video |

| 11:30-12:00 | J | Heterogeneous edge AI processor “AiOnIc™” | Goki Kuroda | ArchiTek Corporation・Director, CMO | Video |

| 12:00-13:00 | E/J | Lunch Break Onsite and Online RISC-V Pavilions | RISC-V Alliance Japan | |

| 13:00-13:30 | J | 3D object detection from image and point cloud data when driving a car using RISC-V | Kyu Yamamoto | SIGNATE Inc. | Video |

| 13:30-14:00 | J | RISC-V Processor development & its extension by ASIP Designer using User RTL | Mitsuru Tomono | Synopsys Japan G.K. Solutions Group, Processor, Wireless & Security IP solutions Staff Application Engineer | Video |

| 14:00-14:50 | J | RISC-V high quality verification with new open standard RVVI and ImperasDV. | Shuzo Tanaka | Imperas Software Ltd. / eSOL Trinity Co., Ltd. , VP & Director, Engineering Department | Video |

| 14:50-15:20 | J | NSITEXE Akaria NS72 — RISC-V 64-bit Processor with Vector Extension —#day2_05_nsitexe | Koji Adachi | NSITEXE , Semiconductor IP R&D Unit, Processor Development Dept, Processor Development, Section Manager of Processor Development | Video |

| 15:20-15:50 | J | MAKE YOUR OWN RISC‑V STORY – DESIGN FOR DIFFERENTIATION | Takaaki Akashi | Country Manager – Japan , Codasip | Video |

| 15:50-16:20 | J | Introducing MIPS eVocore Automotive Solutions | Michio Abe | MIPS LLC, Director, Sales & Solution, Japan | Video |

| 16:20-16:50 | J | Green Hills Software for Safe and Secure RISC-V Systems | Ryan Kojima | Embedded Software Consultant, Green Hills Software | Video |

| 16:50-17:00 | E/J | Day 2 Closing Declaration | RISC-V Association |

DAY 3 Conference : Nov 18 (Fri), 2022 / 10:30 〜 17:00 JST (UTC+9)

Pacifico Yokohama North 3rd Floor G313 Conference Room with live broadcasting

Schedule in Japan Standard Time (UTC+9)

Please note that the speakers and contents are tentative and subject to change, and the schedule may change on the day of the event due to various reasons.

| Time | Lang | Presentation Title | Speaker | Affiliation | Media |

|---|---|---|---|---|

| 10:30-10:40 | E/J | Introduction – Conference and Pavilion | RISC-V Alliance Japan | |

| 10:40-11:30 | E/J | SiFive Automotive, X280 AI & Use Case | Sam Rogan | Vice President, SiFive Japan & Korea and President, SiFive Japan | Video |

| 11:30-12:00 | E | Linux on RISC-V — software ecosystem update | Wei Fu | Red Hat Software (Beijing) Co.,Ltd. , Senior Software Engineer | Video |

| 12:30-13:15 | E/J | RISC-V JAPAN 2022 Product Award / Product Enabler Award Ceremony Live Broadcast from Pacifico Yokohama Exhibition Hall 3 Product Awards and 3 Product Enabler Awards are Currently PlannedEnglish URL for Awards: http://riscv.or.jp/en/2022/11/award-en/ | Calista Redmond | RISC-V International Association | Video |

| 13:15-13:45 | J | Open source RISC-V core IP “mmRISC series” | Munetomo Maruyama | Video |

| 13:45-14:15 | J | VisionFive 2 — World’s first high-performance RISC-V SBC with integrated 3D GPU | Masayuki Kimura | Associate Principal Engineer, StarFive Technology Co., Ltd. | Video |

| 14:15-14:45 | J | Porting RISC-V Soft Processor “RV-PC” Executing Linux OS to FiC FPGA Board | Mitaro Namiki | Tokyo University of Agriculture and Technology Professor, Takefumi Miyoshi | WasaLab LLC, Hideharu Amano | Keio University | Video |

| 14:45-15:00 | E/J | Intermission | ||

| 15:00-15:30 | E | GreenRio: A modern RISC-V microprocessor designed entirely in an agile open source EDA flow | Yifei Zhu | RIOS Lab, Students of TsingHua University // Guohua Yin | RIOS Lab, Students of TsingHua University // Xinze Wang | RIOS Lab, Students of TsingHua University // Zhangxi Tan | RIOS Lab | Video |

| 15:30- | E/J | Day 3 Closing Declaration | RISC-V Alliance Japan |

RISC-V Pavilion / EdgeTech+ 2022

@PACIFICO YOKOHAMA Exhibition Hall

Nov. 16 (Wed.) – 18 (Fri.), 2022 10:00 – 17:00 (Until 18:00 on Thu, 17)

The Pavilion a provides opportunities for visitors to “see” demos and ask questions

| Time | Lang | Title | Company / Organization | Media |

|---|---|---|---|---|

| 11/16-18 | J | Booth Demonstration | Imperas / eSol Trinity | |

| 11/16-18 | J | Booth Demonstration | NSITEXE | |

| 11/16-18 | J | Booth Demonstration | Codasip | |

| 11/16-18 | E | Booth Demonstration |

Online RISC-V Pavilion

The Online Pavilion provides opportunities for visitors to “see” demos and ask questions through RISC-V a live streaming.

Clicking on the content / title of the pavilion will take you to the online RISC-V pavilion website.

Schedule in Japan Standard Time (UTC+9) Subject to change

RISC-V Related Publication

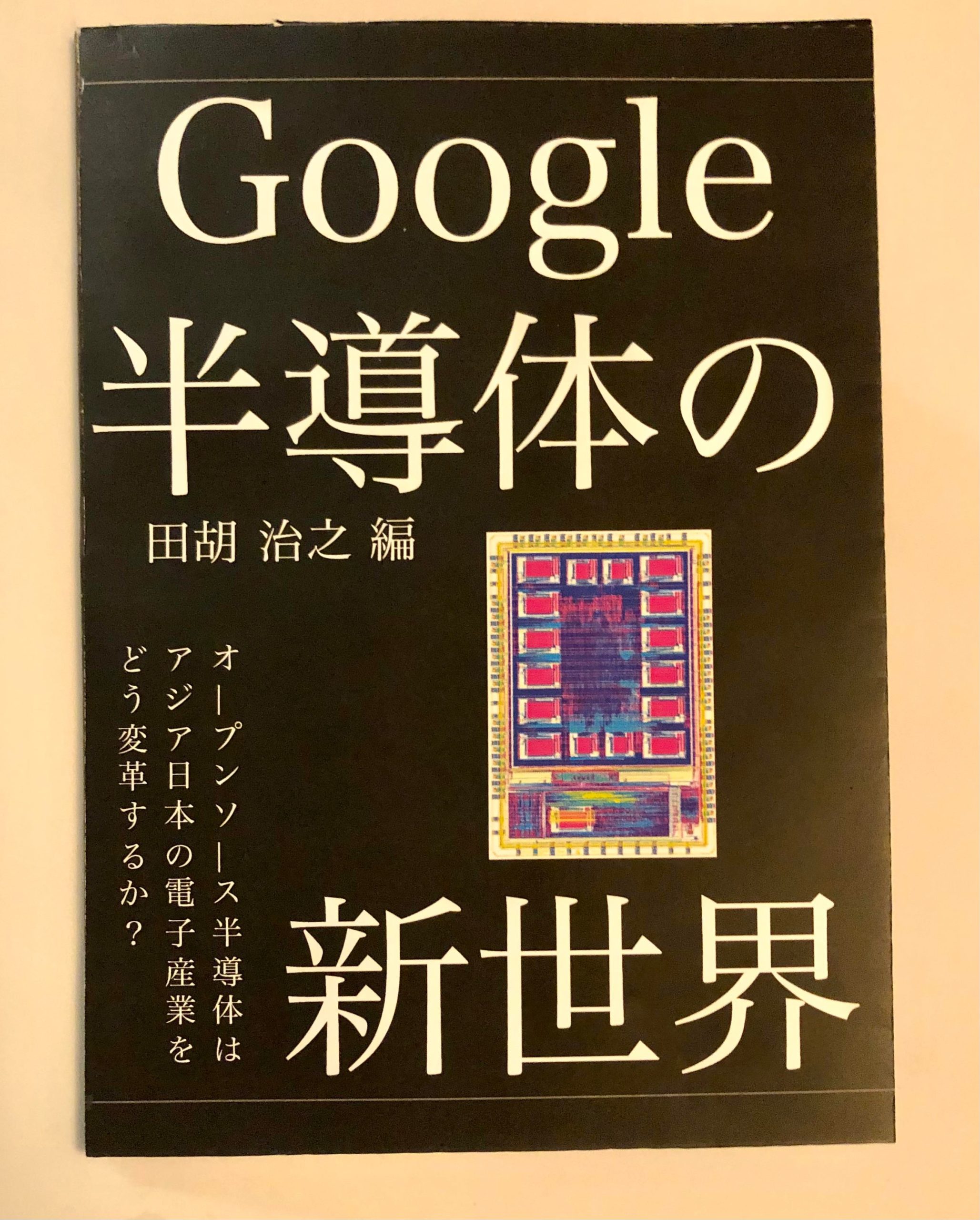

In November 2022 we plan to publish a pilot version of a book about open source trends in semiconductor design, prototyping and manufacturing.

Prof. Amano Hideharu of Keio University and his team is planning to translate “Digital Design and Computer Architecture: RISC-V Edition” by Sarah L. Harris, and David Harris We look forward to the completion in 2022.

In 2021, Chisel study group translated “Digital circuit design starting with Chisel” into Japanese. This will be published by the RISC-V Association.

The RISC-V Association has campaigned to translate RISC-V publications such as “RISC-V Original” (2018) and “Computer Architecture: Quantitative Approach” (2019).