Calista Redmond CEO, RISC-V International

November 2022

## **Open standards and collaboration** are strategic to hardware and software across industries and geographies.

# The definition of open computing is **RISC-V**

RISC-V is the most prolific and open Instruction Set Architecture in history

- RISC-V is inevitable

- RISC-V enables the best processors

- RISC-V is rapidly building the strongest ecosystem

# RISC-V is inevitable

#### RISC-V Mission: RISC-V is the industry standard ISA across computing

#### >10 Billion RISC-V cores already shipped.

- Innovation and adoption moving rapidly across all domains

- Demand at every performance level (low to ludicrous)

- Shared investment is driving the fastest growing ecosystem

Leverage a community ISA spec development model

# **Current ISA Business Models**

| Business Model              | Chips?                      | Architecture<br>License                 | Commercial<br>Core IP       | Add Own<br>Instructions | Open-Source<br>Core IP |

|-----------------------------|-----------------------------|-----------------------------------------|-----------------------------|-------------------------|------------------------|

| Microprocessor              | Yes, <b>two</b><br>vendors  | Νο                                      | Yes, <b>one</b><br>vendor   | Νο                      | Νο                     |

| Proprietary ISA             | Yes, <b>many</b><br>vendors | Yes, <i>expensive</i><br>and restricted | Yes, <b>one</b><br>vendor   | <b>No</b> , (Mostly)    | Νο                     |

| RISC-V Open<br>standard ISA | Yes, <b>many</b><br>vendors | Yes, ISA is an<br><b>open standard</b>  | Yes, <b>many</b><br>vendors | Yes                     | Yes, many<br>available |

**RISC-V** enables design freedom

# Accelerated shared investment in RISC-V

- Numerous roadmaps declared across community incl SiFive, MIPS, Alibaba,....

- \$1B investment by Intel.

- Billions in government investment around the world

- >\$2B in reported Venture Capital investment in start-ups

- \$ Billions more in collective RISC-V community investment

#### intel.

Intel Creates \$1B Innovation Fund To Grow RISC-V Market (And Attract New Foundry Customers) ... Joins RISC-V Board

February 7, 2022

EU <u>announced a new European Chips Act of €15 billion</u> This adds to €30 billion of current public investments

February 8 2022

India Ministry for Electronics & Information Technology launched Digital India RISC-V (DIR-V) program for commercial SHAKTI & VEGA silicon.

April 27, 2022

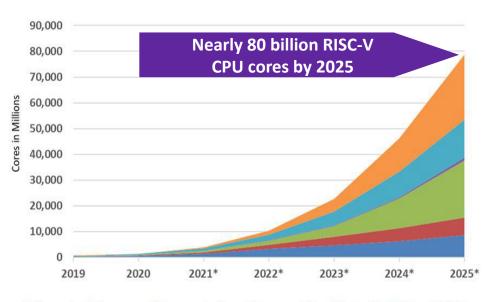

RISC-V CPU core market grows 114.9% CAGR, capturing >14% of all CPU cores by 2025

Computer Consumer Communications Transportation Industrial Other RISC-V

**RISC-V Penetration Rate by 2025**

"The rise of RISC-V cannot be ignored... RISC-V will shake up the \$8.6 Billion semiconductor IP market." -- William Li, Counterpoint Research

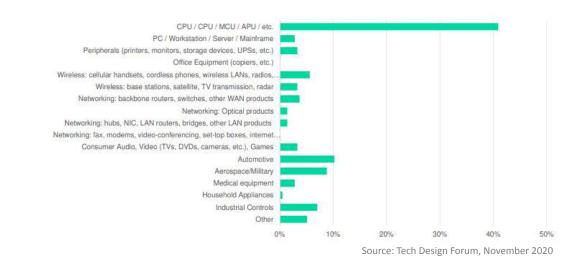

# Nearly a quarter of designs already incorporate RISC-V

#### Projects Incorporating RISC-V by Market Segment

23% of ASIC and FPGA projects incorporated RISC-V in at least one processor in a 2020 study.

"Deloitte Global predicts that

the market for RISC-V processing cores will double in 2022 from what it was in 2021, and that it will double again in 2023,

as the served addressable market available for RISC-V processing cores continues to expand."

December 2021

## RISC-V enables the best processors

**RISC-V enables profound innovation** from low end to high end applications

Inherent and sustainable performance and efficiency advantage, Extensions designed simply, for easy implementation. Modular build from a clean base ISA does not carry legacy baggage.

**Design flexibility and freedom** afford increased innovation potential across multiple variables.

**Supported by massive community**, including major EDA tools as well as optimizing hardware and software co-design to provide most efficient designs scalable to the full spectrum of applications.

#### - Disruptive **Technology** – Barriers Proprietary

Standard

Complexity

Controlled by single entity Limited innovation

1500+ base instructions Incremental ISA

Design freedom

Complex and limited, deep investment

#### **RISC-V**

**Open Hardware + Software Standard** driven by hardware and software community

Modular + Scalable

47 base instructions, No legacy complexity

#### Innovation and Design freedom

Extensible design on frozen base, collective investment

#### **Opportunity**

Diversity of solutions

Collective Investment

Competition

#### **Proprietary**

Single vendor controlled

All Software work benefits single vendor

Vendor lock in, forced to accept next gen solution

#### **RISC-V**

**Massive choice** Competition brings best solutions

#### **Shared Investment**

Software investment benefits all

**Domain Specific** Targeted solution for each market

#### Unconstrained **Opportunity**

# Inherent and sustainable performance and efficiency advantage

- Extensions designed simply, for easy implementation.

- Clean base ISA does not carry legacy baggage.

- Modular design allows implementers to include only appropriate extensions for their solution.

- Reserved encoding space for alternative extensions without disrupting the base ISA / requiring a new ISA

## **Open interfaces are accepted practice**

| Field      | Proprietary<br>predecessor | Open Standard    | Open<br>Implementation          | Commercial<br>implementation on<br>open standard |

|------------|----------------------------|------------------|---------------------------------|--------------------------------------------------|

| Networking | Now obsolete               | Ethernet, TCP/IP | Many                            | Cisco, Juniper                                   |

| OS         | Windows                    | Posix            | Linux, FreeBSD                  | Red Hat, Canonical, Suse,<br>AIX, Zephyr         |

| Compilers  | Intel icc, ARMcc, Xcode    | С                | gcc, LLVM                       | Greenhills, IAR                                  |

| Databases  | Oracle 12C, DB2            | SQL              | MySQL, PostgresSQL              | Oracle, SQLServer, DB2                           |

| Graphics   | DirectX                    | OpenGL           | Mesa3D                          | NVIDIA, AMD, Intel                               |

| ISA        | x86, ARM, IBM360           | RISC-V           | LowRISC, other<br>community led | Numerous RISC-V<br>implementations               |

Successful open standards, enabling multiple implementations

#### RISC-V Innovation Roadmap Al Socs, Application

| Test Chips<br>Software<br>tests<br>Linux port | Proof of Concept<br>SoCs<br>Minion<br>processors for<br>power<br>management &<br>communications<br>Bare metal<br>software | loT SoCs<br>Microcontrollers<br>RTOS, Firmware<br>Development tools<br>Technical Steering<br>HPC SIG, GlobalPlat<br>partnership                                                                                             | Committee,                                          | processors, Linux<br>Drivers, Al Compilers<br><b>SIGS</b> : Security<br>Response, Al, Graphics,<br>Android, Embedded,<br>Datacenter/Cloud,<br>Blockchain, Simulators,<br>Managed Runtimes,<br>Android, Functional<br>Safety<br><b>Programs</b> : Dev Board<br>Seed, Development<br>Partners, RISC-V Labs | SIGS: Vector, Perf Modeling, Perf A<br>Computing, Control Flow Integrity,<br>Microarchitecture Side Channel, Q<br>Error Handling, Automotive, Comr<br>Vector<br>Security specs; RISC-V Security M<br>Platform specs: Platforms, SEE, S<br>ABI, Discovery,Watchdog, ACPI, UE<br>SOC specs: E-Trace, Nexus, IOMM | , Memory Protection,<br>OS, E2E Data Integrity,<br>nunications, Floating Point,<br>odel, AP-TEE, IOPMP<br>BI,<br>EFI |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 2010-2016                                     | 2018                                                                                                                      | 2019                                                                                                                                                                                                                        | 2020                                                | 2021                                                                                                                                                                                                                                                                                                     | 2022                                                                                                                                                                                                                                                                                                           | 2023 →                                                                                                               |

| ISA<br>Definition<br>RISC-V<br>Foundation     | RV32                                                                                                                      | RV32I and RV64I<br>Base<br>instructions:<br>Integer,<br>float,double,<br>quad, atomic,<br>and compressed<br>instructions<br>Priv modes,<br>Interrupts,<br>exceptions,<br>memory model,<br>protection, and<br>virtual memory | Architecture<br>Compatibility<br>Framework<br>Trace | Vector<br>Crypto Scalar<br>Bitmanip<br>Hypervisor<br>ePMP<br>Cache Mgt<br>Virtual Memory<br>Zfh<br>Zfinx<br>Zihintpause                                                                                                                                                                                  | Profiles<br>Packed SIMD<br>Advanced Interrupts<br>Java: ptr masking, I/D synch<br>RV32E & RV64E<br>Bfloat16<br>Vector Half-Precision Floating Poir<br>Code Size<br>Crypto Vector<br>Fast Interrupts<br>SMPU<br>Zmmul<br>Ztso                                                                                   | Matrix Ops<br>Crypto Gost<br>nt<br><b>ISA Extensions</b>                                                             |

|                                               |                                                                                                                           |                                                                                                                                                                                                                             |                                                     |                                                                                                                                                                                                                                                                                                          | Zihintntl                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

# In performance benchmarks, RISC-V is gaining ground really fast

- <u>Researchers Benchmark Experimental RISC-V Supercomputer</u>

- XuanTie C906 Tops MLPerf Tiny v0.7 Benchmark

- <u>MIPS Claims "Best-In-Class Performance" With New RISC-V eVocore CPUs</u>

- Andes Technology RISC-V Processors Reveal Outstanding Performance and Efficiency in MLPerf Tiny

- <u>RISC-V Powered Mango Pi Takes on Raspberry Pi Zero at Its Own Game</u>

- <u>SiFive RISC-V Sees Some Performance Improvements On Ubuntu 22.04</u>

- <u>Greenwaves top results in MLPerf Tiny for hardware acceleration</u>

RISC-V°

Processors in development slated to overtake current proprietary alternatives.

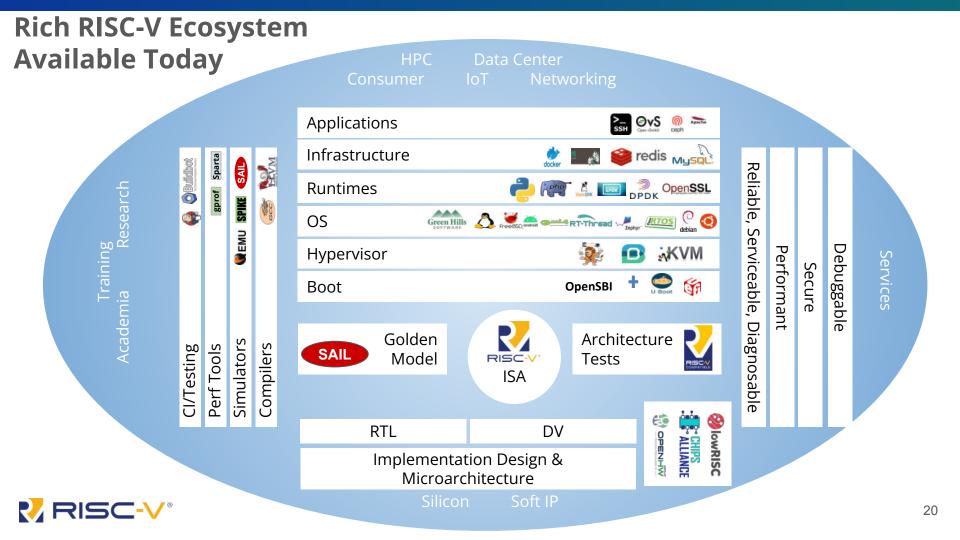

RISC-V is rapidly building the strongest ecosystem

# RISC-V instrumented with software top of mind

- **Open standards enable software** choice. Applications keen to run on RISC-V.

- **Toolchain and OS support** required for Extension ratification

- **Single hypervisor standard** to simplify and unify application support

- Thousands of software developers bringing workloads to RISC-V

- **Strategic imperative and investment** by commercial sector and geographies

- Modern design approaches leveraged for fewer instructions

# Powerful forces fuel a unified RISC-V approach

**Users:** No one wants a repeat of vendor lock-in, avoid fragmentation of legacy ISAs.

**Software:** No one, not even a nation, can afford their own software stack. Upstream open-source projects generally only accept frozen/ratified RISC-V standards.

**Fragmented Alternatives:** Other architectures that enable an architecture license then do not have consistency on those implementations. In addition, there are multiple ISAs from other architectures such as A ISA, M ISA, as well as numerous versions.

- Trust zone and secure boot operate differently on different payment processing systems (credit card, Samsung/Google/Apple pay) for example depending on the manufacturer rather than a uniform approach.

- In IoT, the platform security architecture defines certification mechanisms that are implemented by third parties. Paypal is an example where the security mechanism moved to the cloud rather than the device.

#### RISC-V

#### Fragmentation: Same thing done different ways

# Managing Diversity for RISC-V

#### **Raw extensions**

- Base + standard extensions + custom extensions

- Full suite of options available for experimentation and specialized uses

- Massive combinatorial space of options

#### **ISA Profiles**

- Packages of ISA extensions for given domain

- Initial set: RVI20 (basic), RVA20/22/23 (application processor)

- Factor out common ISA combinations for use in platform standards

#### **Platform standards**

- Hardware/software standards for platforms (much more than just ISA)

- Initial focus OS-A platform for Unix-like OS (includes IOMMU, AIA, etc)

#### Diversity: Solving different problems

# **RISC-V Technical Programs**

#### RISC-V Developer Boards

Available to spur innovation, provide hands-on education, and engage early adopters to test and develop.

Recognizes the investment and dedication of organizations making significant technical contributions to RISC-V.

RISC-V Lab

Institutions that host a lab with RISC-V hardware for CI/testing and general availability sandboxing.

**RISC-V Compatible** Architectural Tests created to help ensure that software written will run on implementations that comply with that profile. Branding available for compatibility.

#### **RISC-V Platform**

A common, reusable runtime environment that operating systems and applications can target to improve portability and reuse. Provides interoperability assurance.

#### **RISC-V Profiles**

Refers to a base ISA and one or more extensions that are specified as a group so that applications can be compiled once, run on different implementations, and get the same results.

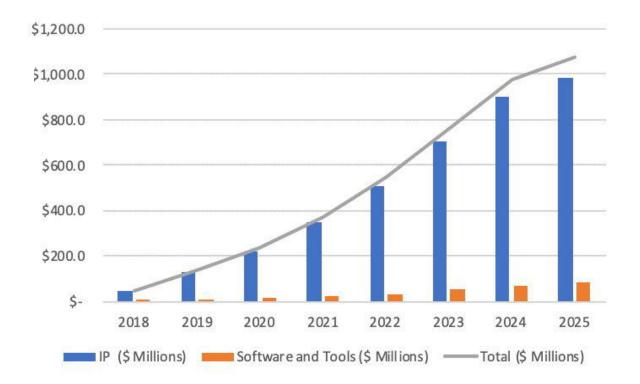

#### **RISC-V IP, SW, and Tools build momentum**

The total market for RISC-V IP and Software is expected to grow to \$1.07 billion by 2025 at a CAGR of 54.1%

#### Investment and traction accelerate in 2022

PULP Platform HEROv2: Full-Stack Open-Source Research FPGA Platform for Heterogeneous Computing

HEROv2 for heterogeneous computing based on clusters of 32-bit RISC-V cores and an application-class 64-bit ARMv8 or RV64 host processor for sharing data between 64-bit hosts and 32-bit accelerators.

January 16, 2022

#### intel.

Intel Corporation Makes Deep Investment in RISC-V Community to Accelerate Innovation in Open Computing

RISC-V welcomes Intel to the Board of Directors to collaborate on RISC-V IP and contribute to RISC-V software development

#### Intel Creates \$1B Innovation Fund To Grow RISC-V Market (And Attract New Foundry Customers)

February 7, 2022

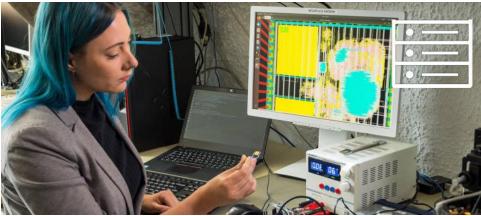

Automotive RISC-V processor functional design verification

NSITEXE selected ImperasDV for RISC-V design verification, expanding Imperas' simulation technology, models, verification IP and tools by NSITEXE for next gen 64bit RISC-V vector accelerators in AI automotive with verification for level needed to attain ISO 26262 ASIL D.

The European Commission <u>announced a</u> <u>new European Chips Act of €15 billion in</u> <u>additional public and private investments</u> <u>until 2030</u>. This adds to €30 billion of public investments previously earmarked.

February 8 2022

intel.

Intel to spend €17bn on chip mega-factory in Germany... expands manufacturing in Ireland, plus R&D and packaging across Europe

March 15, 2022

#### Hot off the press 2022!

...

SiFive @SiFive

We're thrilled to be featured on the @Nasdag video wall this morning to celebrate our historic moment: a \$2.5B valuation from our Series F round! #RISCV **#NoLimits**

10:02 am · 16 Mar 2022 · HubSpot

Clockwork Pi announced availability of DevTerm R-01, the first 64-bit RISC-V portable computer with retro styling and modern computing power.

March 15, 2022

The government of India Ministry for Electronics & Information Technology launched Digital India RISC-V (DIR-V) program with aggressive milestones for commercial silicon of SHAKTI & VEGA

April 27, 2022

#### MIPS

#### MIPS Pivots to RISC-V with Best-In-Class Performance and Scalability

eVocore P8700 high performance for deep pipeline with multi-issue Out-of-Order (OOO) execution and multi-threading. Scales to 64 clusters, 512 cores and 1.024 harts/threads. Available in Q4 2022.

eVocore 18500 – power efficiency: in-order multiprocessing with best-in-class power efficiency for SoC applications.

RISC-V

May 10, 2022

#### Momentum headlines in 2022

#### Spain Approves €12.25b Semiconductor Investment Plan

President Sanchez met CEOs of MicronTech Intel & Qualcomm at WEF22 on Spain's €12 billion strategy in global semiconductor industry with RISC-V lab at BSC, and Investment in Spain

#### May 25, 2022

Università di Bologna, CINECA and E4 "Monte Cimone" Cluster, a **RISC-V** platform using SiFive **RISC-V SoCs demonstrated** remarkable software and hardware readiness and maturity - first gen RISC-V HPC machines June 11, 2022 coming soon.

Microchip RISC-V based PolarFire FPGAs enter mass production: Microchip is writing a new chapter in the history of RISC-V with the availability of production-gualified SoC PolarFire devices. lune 8, 2022

Accelerating ML Recommendation With Over 1,000 RISC-V/Tensor Processors on Esperanto's ET-SoC-1 Chip lune 17, 2022

#### C-J Alibaba Cloud

XuanTie C906 Tops MLPerf Tiny v0.7 Benchmark June 13, 2022

Antmicro Renode 1.13 for improved machine learning and pre-silicon development lune 17, 2022

#### Imagination

Imagination Technologies announces RTXM-2200 real-time embedded RISC-V CPU, a highly scalable 32-bit embedded solution with a flexible design for networking solutions, packet management, storage controllers, and sensor management for AI cameras and smart metering. lune 21, 2022

- **Esperanto** 1,000-Core RISC-V AI accelerator.

- Alibaba RISC-V Xuantie processors with 4 open cloud and edge processors

- **Imagination** RISC-V CPU family, for discrete and heterogeneous computing

- **Seagate** hard disk drive controller with high-performance RISC-V CPU.

- **Ventana** performance chiplet approach to data center SoC design

- **Intel** Nios processor based on RISC-V, designed for performance.

RISC-V CPU core market will grow 115% CAGR, capturing >14% of all CPU cores by 2025

– Semico Research, December 2021

#### Communication AI SoC RISC-V designs will grow 21.2% CAGR from 2019-27 - Semico Research, December 2021

- Andes RISC-V processor adopted by SK Telecom for AI products.

- Alibaba supporting Android 12 on their 64-bit RISC-V core emulated in QEMU

- Sipeed RISC-V chip runs Android 10, RV64 phone coming next

- Alibaba ported TensorFlow Lite for AI image, audio, and optical in smart devices.

- Google Pixel 6 Titan M2 RISC-V processor, with extra speed and memory, more resilient to advanced attacks.

#

- **Huawei** Hi3861 RISC-V board for Harmony OS developers for IoT

- Zepp Health / Huami wearable manufacturer OS supporting RISC-V Reference Models for RISC-V P extension

- **GreenWaves** ultra-low power GAP9 hearables platform for scene-aware and neural network-based noise reduction.

- **RIOS Lab** announced PicoRio, an affordable RISC-V small-board computer.

- **SiFive** world's fastest development board for RISC-V Personal Computers.

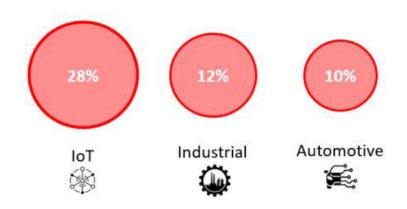

RISC-V will command 28% of the IoT market by 2025

- Counterpoint Technology Market Research, September 2021

#### RISC-V-based AI SoCs will grow **73.6% CAGR to 25B units and \$291B in revenue by 2027** – Semico Research, December 2021

- Alibaba Cloud tops MLPerf Tiny v0.7 Benchmark with its IOT processor

- **Esperanto** accelerating ML Recommendation With Over 1,000 RISC-V/Tensor Processors on ET-SoC-1 Chip

- **StarFive** released the world's first RISC-V AI visual processing platform

- Andes released superscalar multicore and L2 cache controller processors.

- **NVIDIA CUDA** support on Vortex RISC-V GPGPU enables scaling from 1-core to 32-core GPU based on RV32IMF ISA

- **Fraunhofer** ported Tensorflow lite to their RISC-V processor core for Edge AI applications incl sensor data evaluation, gesture control, or vibration analysis.

- **Seeed Studio**'s new Sipeed MAIX, a RISC-V 64 AI board for Edge Computing makes it possible to embed AI to any IoT device.

- **Micro Magic** announced an incredibly fast 64-bit RISC-V core achieving 5GHz and 13,000 CoreMarks at 1.1V.

- Western Digital SweRV Core enables spectrum of compute at the edge

- **Microchip** released the first SoC FPGA development kit based on the RISC-V ISA.

- **E4** Monte Cimone Cluster along with DEI-UNIBO contributing to architecture, software, and integration.

- **European Processor Initiative** RISC-V accelerator with first chip Sep 2021

- **Technical University of Munich** (TUM) quantum cryptography chip for quantum computing security demands

- **Tactical Computing Labs** HPC-centric software test suite for GCC and LLVM

- **Cortus** is developing a high-performance RISC-V Out-of-Order processor core for the European eProcessor project.

- **De-RISC** HW-SW platform for multi-core RISC-V SoC for safety critical aerospace

NRISC-V®

# High Performance Computing

Johanna Baehr of TUM heads a team that has hidden four hardware Trojans on this chip - malicious functions that are integrated directly into the circuits.

#### RISC-V will capture 10% of the Automotive market by 2025 - Counterpoint, September 2021

**SiFive** high-end applications and real-time processors for leading performance, with lowest area and power consumption in vehicles for safety, security, and performance

**Andes** launched safety-enhanced 32bit RISC-V CPU IP, first to be fully compliant with ISO 26262 functional safety.

**IAR** RISC-V Embedded Workbench for **SiFive** infotainment, connectivity, and ADAS products.

2020 RISC-V automotive opportunity 4M cores; growing to 150M cores in 2022 and 2.9B cores by 2025. – Deloitte, December 2021

RISC-V Automotive Value Multicore SoC revenue to be \$5.7B in 2022. Advanced RISC-V AI SoCs for High-End Passenger Cars to Reach \$819M by 2027 - Semico Research, June 2022 **MobileEye** EyeQ Ultra vision advanced driver assist systems chips for 176 trillion ops per second with 12 RISC-V CPU cores.

**Andes** ISO 26262 Functional Safety ASIL D Dev Process Certification for RISC-V embedded safety with Andes processors

**Renesas and SiFive** partner on next-gen, high-end RISC-V automotive applications. SiFive licenses RISC-V core IP to Renesas.

**Imagination Technologies** GPU linked by a RISC-V core for ASIL-B level designs with ISO 26262 safety critical certification.

**Green Hills** support RISC-V RTOS targeting ISO-26262 ASIL D applications

**MIPS** RISC-V eVocore processors for high-performance, real-time compute in datacenter and automotive

**Fraunhofer** RISC-V Processor cores for functional safety and cyber security, and engaging in GaNext program.

**IAR Systems** functional safety of Embedded Workbench sw tool chain for **NSI-TEXE** RISC-V core.

**NSI-TEXE** 64bit RISC-V vector accelerators with **ImperasDV** design verification for automotive AI with ISO 26262 ASIL D.

**Europe GaNext** power converters with GaN power processors with better efficiency and compactness for EV chargers.

**Kneron** RISC-V based AI edge chip for Automotive

## **Dedicated Community**

33

#### Japan RISC-V Members

Cyber Physical Security Research Center of AIST **DTS INSIGHT Corporation** Hitachi, Ltd. NSITEXE OTSL, Inc PEZY Computing, K.K. **Renesas Electronics Corporation** Software Hardware & Consulting Sony Semiconductor Solutions Corporation The University of Electro-Communications The University of Tokyo UNO Laboratories, Ltd.

# **RISC-V** collaboration in apan

"RISC-V continues to gain momentum around the world, and we plan to leverage SiFive's portfolio of automotive RISC-V products in our future automotive SoC solutions to meet the exacting demands of these global customers."

- Takeshi Kataoka, Senior VP and GM of Automotive Solution Business Unit at Renesas

#### More than 3,100 RISC-V Members across 70 Countries

| 3200                               | 111 Chip                                                                                  | 3 Systems                                                                                               |

|------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 2800                               | SoC, IP, FPGA                                                                             | ODM, OEM                                                                                                |

|                                    |                                                                                           |                                                                                                         |

| 2400                               | 3 1/0                                                                                     | 14 Industry                                                                                             |

| 2000                               | Memory, network, storage                                                                  | Cloud, mobile, HPC, ML, automotive                                                                      |

| 1600                               |                                                                                           | and the second second                                                                                   |

| 1200                               | 19 Services                                                                               | 139 Research                                                                                            |

| 10001                              | Fab, design services                                                                      | Universities, Labs, other alliances                                                                     |

| 800                                |                                                                                           | 2k+ Individuals                                                                                         |

| 400                                | 56 Software                                                                               |                                                                                                         |

| 0                                  | Dev tools, firmware, OS                                                                   | RISC-V engineers and advocates                                                                          |

| Q3 Q4 Q1 Q2<br>2015 2015 2016 2016 | Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 G<br>5 2016 2016 2017 2017 2017 2017 2018 2018 2018 2018 20 | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4<br>019 2019 2019 2019 2020 2020 2020 2020 2 |

| Oct 2022                           |                                                                                           |                                                                                                         |

**RISC-V** membership rapid growth of 134% in 2021

Technical Deliverables

Technical **governance** Build technical deliverables Guide strategic technical Work groups

Profiles & Platforms & Architecture Compatibility Tests (ACT) & Platform Compatibility Tests (PCT)

#### Marketing

Create brand value around RISC-V **Amplify** member news, content, and success with press & analysts **Original content** programs RISC-V, industry, and regional Events

Learning & Talent

Multi-level online learning Connecting **universities** with labs, tests, and curricula **RISC-V Training Partners** Jobs and internships

**Advocacy + Alliances**

Geo and industry **alliances Local** developer groups and events

**RISC-V Exchange**

**Online directory** of providers, products, services, and learning resources

Technical developer forums

# **RISC-V** delivers incredible member support

**Benefits** engaging in **RISC-V**

#### Accelerate technical traction and insight

- Contribute technical priorities, approaches, and code

- Gain strategic and technical advantage

- Increase visibility, leadership, and market insight

- Fill and increase engineering skills, retain and attract talent

- Build **innovation partner** network and customer pipeline

- Deepen, engage, and lead in local and industry developer network

- Showcase RISC-V products, services, training, and resources

RISC-V is a community of passionate, dedicated, and invested stakeholders

As individuals As companies As universities As public institutions and non-profits As nations

As one Global, connected movement

Build RISC-V into your company strategy, and your personal mission

# **Thank You**

Scan for Calista Contact info

risc-v-international calistaredmond

# **Membership Options**

#### **Premier Member Benefits**

- Board seat and Technical Steering Committee seat included at \$250k level

- Technical Steering Committee seat included at \$100k level

- Board level includes seat on RISC-V Legal Committee

- Eligible to lead workgroup and/or committee

- Use of RISC-V Trademark for commercialization

- Member logo / name listing on RISC-V website, alphabetical with Premier members

- Solution / Product listing highlighted on RISC-V Exchange, noted with member level

- 4 case studies a year

- 2 blogs per month

- 2 social media spotlights per month

- Spotlight member profile

- Event sponsorship discount

#### **Premier Requirements**

- Membership open to any type of legal entity

- \$250k Annual membership fee that includes Board seat and TSC seat

- \$100k Annual membership fee that includes TSC seat

#### **Strategic Member Benefits**

- 3 Board reps elected for the Strategic tier, including Premier members that do not otherwise have a board seat

- Eligible to lead workgroup and/or committee

- Use of RISC-V Trademark for commercialization

- Member logo / name listing on RISC-V website, alphabetical with Strategic members

- Solution / Product listing highlighted on the RISC-V Exchange, noted with member level

- 1 case study a year

- 1 blog per month

- 1 social media spotlight per month

- Event sponsorship discount

#### **Community Member Benefits**

- Two Board representatives

- 1 Community Board representative, elected

- 1 Individual Board representative, elected

- Member logo / name listing on RISC-V website, by member level

- 1 case study a year

- 1 blog per quarter

- 1 social media spotlight per quarter

- Event sponsorship discount

#### **Strategic Member Requirements**

- Membership open to any type of legal entity

- · Annual membership fee based on employee size

- 5,000+ employees: \$35k

- 500-5,000 employees: \$15k

- <500 employees: \$5k</li>

- <10 employees & company <2 yrs old: \$2k</li>

#### **Community Requirements**

- Membership open to

- academic institutions,

- non-profits,

- individuals not representing a legal entity

- No annual membership fee

## **RISC-V Learn**

Learning RISC-V is a challenging, highly rewarding activity. There are many resources available to help you on this technical journey, and we welcome new additions to these resources – please contact us at <u>info@riscv.org</u> with any questions or comments.

#### Learn Online

Online learning at beginner, intermediate, and advanced levels to increase engineering expertise and career opportunity on RISC-V across the industry.

#### **Training Partners**

Provide RISC-V training in a professional setting to extend the breadth and reach of RISC-V knowledge

#### **University Resources**

Universities that support RISC-V curriculum and other programing as well as books and other learning resources.

# **Profiles and Platforms**

#### **ISA Profiles**

- A set of **extensions** that are compatible

- **Extension types**: required, optional, unsupported, or incompatible

- Two profile types:

- **Application (RVA[yy]):** Linux-class and other embedded designs with more sophisticated ISA needs

- Microcontroller (RVM[yy]): Cost-sensitive application-optimized embedded designs running bare-metal or simple RTOS environments

- Running the same sequence of instruction between implementations are **RISC-V** compatible

#### System Platforms

- A set of **features** that are compatible

- Includes ISA Profiles, software and hardware system components, standardized hardware/software interfaces, etc

- **Two Platform types**: OS/A and M (naming TBD)

- Ability to move an executable from one implementation to another and get the same results are **RISC-V Compatible**

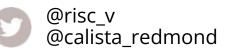

# **Technical Organization**

| Board of Directors (BoD)                                                                                        |                                                                 |                                       |                            |            |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|----------------------------|------------|--|

|                                                                                                                 | Technical Steering Committee (TSC) Architecture Profiles        |                                       | CTO, Staff                 | CTO, Staff |  |

|                                                                                                                 |                                                                 | Unpriv IC                             | Priv IC                    |            |  |

|                                                                                                                 |                                                                 | Architectu<br>Architecture Review (IC |                            |            |  |

| Industry Verticals SIG                                                                                          | Software HC<br>(Platforms, Toolchains, Runtimes)                | IMAFDQC                               |                            |            |  |

|                                                                                                                 | Security HC                                                     | Zb[abcs]<br>Memory Model              | <u>еРМР</u><br>1.12 (Priv) |            |  |

|                                                                                                                 | RAS HC                                                          | Crypto Scalar<br>Zfinx                | Н                          |            |  |

|                                                                                                                 | Technology Sector HC                                            | Vector SIG                            |                            |            |  |

|                                                                                                                 | Technology Sector HC<br>OZI<br>SoC Infra. HC<br>(Trace & Debug) | FP SIG                                |                            |            |  |

| ω                                                                                                               | Implementation HC                                               |                                       |                            |            |  |

| Consumer<br>Automotive<br>Data Center<br>Finance<br>Communications<br>Oil & Gas<br>Oil & Gas<br>Defense/MilAero | ISA Infrastructure HC                                           | V phase 2<br>Crypto GOST-R TG         |                            |            |  |

| ume<br>Cent<br>Cent<br>Gas<br>Gas                                                                               |                                                                 | Packed SIMD TG                        |                            |            |  |

| Consumer<br>Automotive<br>Data Center<br>Finance<br>Communica<br>Oil & Gas<br>Defense/Mi                        |                                                                 | J TG                                  |                            |            |  |

| Consum<br>Automo<br>Data Cei<br>Finance<br>Commui<br>Oil & Ga<br>Defense                                        |                                                                 | Code Size TG                          | AIA TG                     |            |  |

|                                                                                                                 |                                                                 | Crypto Vector TG                      | SMPU TG                    | Done       |  |

| _                                                                                                               |                                                                 | Alt FP TG<br>FT: Zmmul, Zihintntl,    | FastInt TG                 | TODO       |  |

| NRISC-V°                                                                                                        |                                                                 | WRF                                   | CMO 2 TG                   | Active     |  |

Dotted line

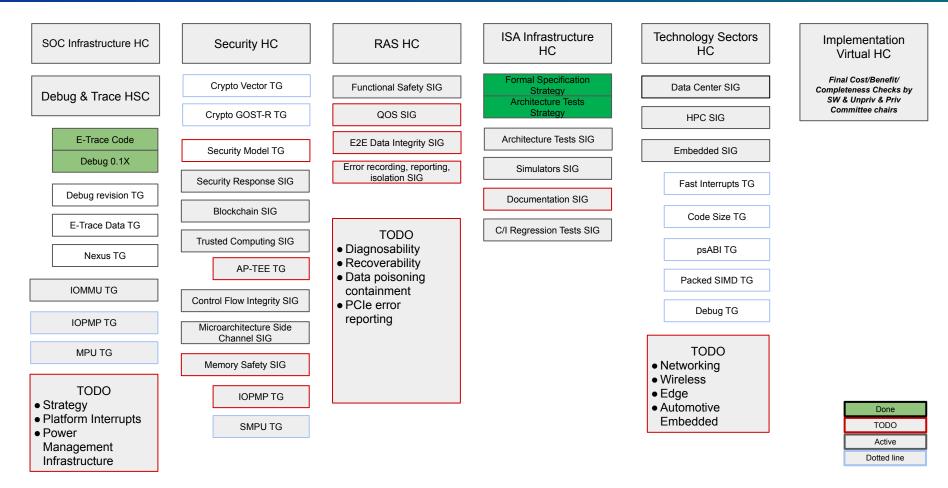

# Software Horizontal Committee

| AI/ML/NLP/Graphics<br>SIG | Platform HSC<br>(includes platform specs) |                     | Toolchain & Runtimes HSC                                                             |                       |

|---------------------------|-------------------------------------------|---------------------|--------------------------------------------------------------------------------------|-----------------------|

| Android SIG               | Config TG                                 | Hypervisors SIG     | psABI TG                                                                             |                       |

| Perf Modeling SIG         | AIA TG                                    | IOPMP TG            | Topics TODO:                                                                         | Code Size TG          |

| Perf Analysis SIG         | Topics TODO:                              | OS-A Platform SIG   | Benchmarks     Regression test strategy                                              | HPC SIG               |

| IOMMU TG                  |                                           | RVM-CSI Platform TG |                                                                                      |                       |

|                           |                                           | OS-A SEE TG         | <ul> <li>DSP</li> <li>DB &amp; Hadoop et al</li> <li>Performance analysis</li> </ul> | Managed Runtimes SIG  |

|                           |                                           | OS-A PlatformTG     | Native code     GCC     LLVM     Optimizer                                           |                       |

|                           | TGs for specs underway                    | OS-A PCT TG         | o Profiler<br>o gdb                                                                  |                       |

|                           |                                           |                     |                                                                                      | Done<br>TODO          |

| NRISC-V°                  |                                           |                     |                                                                                      | Active<br>Dotted line |

RISC-V°