2025年2月27日木曜日

9:00-18:00 日本標準時 (UTC+9)

2025春のポスターセッションCFPに申し込みたい方はここをクリック

(アブストラクト提出期限:2025年2月17日 ポスター提出期限:2月19日)

| 内容別カラー分類 |

| ① RISC-V ソリューション |

| ② 特別企画:日本の半導体戦略2025: NVIDIAの偉業に挑むAIチップ企業群 |

| ③ RISC-V 昼食交歓会 |

| ④ RISC-V 技術展示 |

| ⑤ RISC-V研究とオープン半導体 |

| ⑥ AI、RISC-V研究ポスター発表 |

RISC-V Day Tokyo カンファレンスは、日本最大の RISC-V イベントです。 RISC-V Day Tokyo 2025 Spring カンファレンスは、2025 年2月27日木曜日 9:00 ~ 18:00 JST (UTC+9) に東京大学伊藤国際学術研究センター(予定)で開催されます。 RISC-V関連の優れた技術や製品、キーマンやエンジニアを集め、製品の認知度向上、企業間連携の実現、技術交流、情報収集などのビジネスチャンスを提供します。 ぜひこの機会に皆様のご参加をお待ちしております! 発表の動画や資料情報を後日ホームページに掲載いたします。

① RISC-V ソリューション ② 特別企画:日本の半導体戦略2025: RISC-V AIチップ

2025年2月27日 時間 9:00-18:00

| 時間 | 発表時間 | 言語 | プレゼンテーション題名 | 発表者 | 所属機関 (詳細はクリック) | 講演資料 |

|---|---|---|---|---|---|

9:00- | 50分 | – | 参加者は地下2階とホールに入場できます。受付スタッフが名札を配布します。 | スタッフが録音機器、オーディオ・ビデオシステム、展示ブースを設置します。 | |

| 9:50- 10:00 | 10分 | 日英 | 開会の挨拶 | 天野英晴 | 東京大学 | |

| 10:00- 10:35 | 30分 | 英 | イノベーションを超えて: 成熟した IP による RISC-V の大量導入への道 概要: AIハードウェア市場においてTenstorrentは、低コストRISC-Vベースの開発システムとオープンソースのAIコンパイラスタックを提供することで、開発エンジニアや開発の早期フェーズにある顧客をターゲットとして、チームの拡充、製品出荷を進めています。同社は最近、6億9300万ドルのシリーズDの資金調達を完了し、AI業界のトップ10企業の1つに選ばれました。高帯域幅メモリなどの高価な部品を避け、テンソルプロセッサアーキテクチャを採用することでメモリ帯域幅の必要性を低減し、コストパフォーマンスを実現している点です。既に1億5000万ドルの収益を確保し、差別化された技術を求める小規模な顧客に注力して有機的な成長を目指しています。CEOのジム・ケラー氏は、今後10年間でAIにより計算技術が大きく変革される可能性を指摘しており。ハードウェアやソフトウェア、オープンソースの協調動作が重要な役割を果たすとしています。スティーブ・ジョブズのようにユースケースを中心に考えた卓越した製品を作ることが成功の鍵だと考えています。緊迫する米中関係の中で、同社は貿易規制のルールを順守しつつ、地政学的変化にも柔軟に対応する姿勢を示しています。 (タイトルとアブストラクトは主催者の解説です 発表者によるAbstractの準備が出来次第変更します。) | ウエイ・ハン・リエン | シニアフェロー, テンストレント(米国) | |

10:35– | 30分 | 日 | SiFive の AI コンピュート時代のRISC-Vにおけるリーダーシップ 概要:SiFive のモメンタムは継続しています。同社は最近、組み込みソリューションから最先端のスカラーとベクターを処理する高性能プロセッサまで、幅広い製品ポートフォリオを追加しました。最新製品を紹介し、ロードマップが AI、データセンター、自動車、モノのインターネットなどの分野で顧客の急速なイノベーションをどのように推進しているかについて説明します。 | 近藤 芳人 | CEO, サイファイブ ジャパン(米国) | |

11:10-11:35 | 20分 | MIPSのマルチスレッド対応、安全性で高効率なRISC-Vコンピュートソリューションが駆動する 自律システム向けプラットフォーム 概要: 生成AIが自動車および産業用途への実装を加速する中、ソフトウェア定義型プラットフォームは『ゾーン型アーキテクチャ(Zonal Architecture)』へと移行しつつあります。ゾーン型アーキテクチャとは、従来の機能別ECUを配置する方式から、車両内の物理的なゾーンごとにECUを統合し・分散配置する構造へと進化させたものです。これにより、配線の簡素化、データ処理の高速化、制御の最適化、OTAが可能となります。 電動化、自動運転、産業オートメーションといった次世代システムの課題に対応するためには、高速データ処理、超低レイテンシ、高効率なリアルタイム制御を実現する新しいコンピュートサブシステムが必須です。本講演では、マルチスレッド対応で安全性を備えたRISC-Vプロセッサコアが、決定論的アクセス、RISC-Vプロファイルとの互換性、データ転送やメモリ操作向けの応用に特化した性能強化を実装し、次世代の産業用ロボット、自律システム向けプラットフォーム、電動車両の高度な制御と最適化を実現する最適な選択肢となる理由を解説します。 | チョル・キム | マーケティング ディレクター | ミップス テクノロジー インク(米国) | ||

11:35-11:45 | 10分 | {休憩} |

| ||

11:45-12:10 | 20分 | 英 | AI/ML アプリケーション向け RISC-V SoC のデータ転送アーキテクチャの最適化 概要: このプレゼンテーションでは、組み込みビジョン アーキテクチャのコンテキストにおける人工知能/機械学習 (AI/ML) のデータ転送アーキテクチャの課題とソリューションを示し、RISC-V ベースのシステム オン チップ (SoC) のネットワーク オン チップ (NoC) の実装について説明します。AI/ML および組み込みビジョン アーキテクチャでは、データ転送アーキテクチャにおいて、オフチップ DRAM からすべての関連データを取得し、キャッシュに効率的に保存して転送し、SoC およびチップレット システムでの効率的なコンピューティングを可能にするという技術課題があります。これらの課題を解決するために、NoC (Network on Chip)実装の要件が生じ、NoCは、業界で「メモリ ウォール」と呼ばれる、パフォーマンス、消費電力、コストに影響を与える、プロセッサと DRAM のメモリ アクセス速度の格差によってもたらされる課題に対処します。NoCにおいても、自動車および産業用アプリケーションの分野では、ISO26262 および関連認証を取得するために、安全性と回復力に関する特別な考慮が必要です。 解説: Arteris, Inc. は、特に自動車用電子機器、人工知能/機械学習、消費者市場などのデバイスで利用されているネットワーク オン チップ (NoC) 相互接続 IP とシステム オン チップ (SoC) 統合自動化ソフトウェアの開発を専門としています。主力製品である FlexNoC は、2022 年現在、30 億を超えるデバイスに統合されています。Arteris は、キャッシュ コヒーレント相互接続 IP である Ncore や、ラスト レベル キャッシュ IP である CodaCache などの製品を提供しています。 (タイトルとアブストラクトは主催者が作成 発表者によるAbstractの準備が出来次第変更します。)

| ミハル・シウィンスキー | アルテリス(米国) | |

12:10-12:45 | 30分 | ARC-V プロセッサ IP の紹介、RISC-V ISA の最適化された実装 概要: Synopsys ARC-V プロセッサ IP は、RISC-V ISA に基づいています。ARC-V プロセッサ ファミリには、組み込みアプリケーション向けの超低消費電力、制御および信号処理に最適化されたプロセッサである ARC-V RMX、コヒーレント ハードウェア アクセラレータと仮想化サポートを備えた 32 ビット リアルタイム マルチコア プロセッサである ARC-V RHX、および SoC ホスト アプリケーション向けの 64 ビット「ARC-V RPX」が含まれます。RPX ファミリには、L3 キャッシュと RISC-V 準拠の MMU が含まれており、Linux などの豊富なオペレーティング システムをサポートしています。Synopsys の ARC-V FS プロセッサは、ISO 26262 (機能安全規格) の ASIL-D レベルを満たし、ISO 9001 認定の品質管理システムに基づいて開発されています。これらのプロセッサには、システム エラーを検出して安全性を確保するためのハードウェア安全機能が統合されています。さらに、ISO 21434(自動車サイバーセキュリティ規格)に準拠しています。プログラム開発、デバッグ、最適化を支援するために、Synopsys の「MetaWare 開発ツールキット」が提供されています。ARC-V ライセンシーは、Synopsys の「ARC Access」パートナーと、成長を続ける RISC-V エコシステムのツールとソフトウェアを活用して、開発スケジュールを短縮し、製品をより早く市場に投入することができます。 | 田辺 聡、IP グループ スタッフ アプリケーション エンジニア | シノプシス(米国) | ビデオ | |

12:45-13:00 | 15分 | ポスターセッション紹介:ポスターセッションの参加者を紹介します。発表者は、ホールに登壇していただきます。 | 中條 拓伯 | 教授, 国立大学法人 東京農工大学 知能情報システム工学専攻(日本) | ビデオ | |

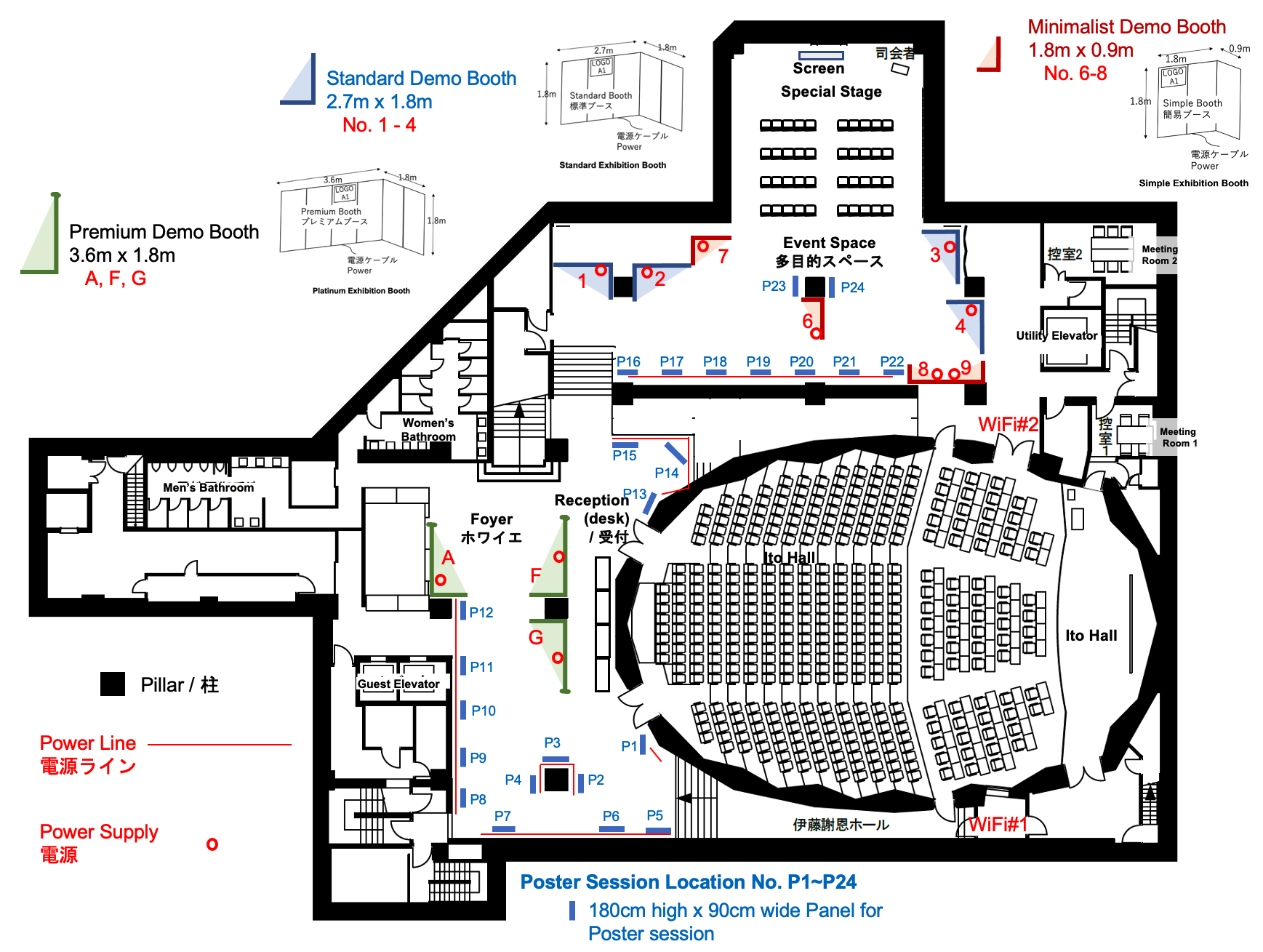

13:00-15:30 | 150分 | ポスター発表: 伊藤ホール B2 の南ホワイエで行われます。フロアプランマップを参照して、ポスターパネルの位置 P1 から P15 を探してください。 | ポスター発表者 | ||

13:00-14:00 | 60分 | – | {ランチタイム}: RISC-V ランチネットワーキングセッション | ||

14:00-14:35 | 30分 | RISC-V による現代のコンピューティングの変革 概要: RISC-V は、幅広いアプリケーションで急速に普及しています。たとえば、Andes の顧客は、クラウドとエッジの AI/ML、自動車、5G/ネットワーキング、MCU/MPU、マルチメディア、ストレージ、センサー処理、ウェアラブル、ワイヤレス接続などの分野にまたがっており、エッジからクラウドまでの AI/ML が特に顕著です。RISC-V エコシステムが Linux と Android 向けに成熟するにつれて、RISC-V コアをパーソナル コンピューティング デバイスやサーバーのプライマリ CPU として使用する需要が高まっています。これらの進歩により、RISC-V は今後数年間でコンピューティング業界での市場プレゼンスを大幅に高めることができます。 | Charlie Hong-Men Su 蘇泓萌 | CTO 兼社長, Andes Technology(台湾) | ||

14:35-15:00 | 20分 | RISC-V CPUコア、22nm超低リーク・プロセス、およびReRAM不揮発メモリ技術を使用したパワエレ制御向けMCU MD6605の開発 概要: | 山崎尊永 | サンケン電気, 技術開発本部 パワーデバイス開発統括部 シニアマイスター(日本) | ||

15:00-15:30 | 30分 | {休憩} | |||

15:30-16:00 | 30分 | 英 | Kubudsが切り開くRISC-V開発の未来:クロスツールチェーンと最適化技術:Kubudsは、RISC-Vエコシステムの発展を支援するために、組み込みシステムやPC向けの包括的なソフトウェアツールチェーンとフルスタックソリューションを提供しています。同社の強みは、オープンソースのリアルタイムOS(RTOS)やLinux向けの最適化に加え、最新のクロスコンパイルツール(GCC、LLVM)を活用した高効率な開発環境の構築にあります。クロスコンパイルツールチェーンの提供においては、開発者が異なるプラットフォーム間でシームレスにアプリケーションをビルド・実行できる環境を整備しており、エンベデッドシステムからPCまで幅広い適用が可能です。さらに、デバッグ環境の整備にも注力し、GDBやOpenOCDなどのツールを活用した高度なデバッグ機能を提供し、開発の生産性を向上させています。統合開発環境(IDE)のサポートとしては、VS CodeやEclipseなどの主流IDEへのスムーズな統合を実現し、開発者が既存のワークフローを維持しながら、RISC-Vベースのアプリケーションを開発・最適化できる環境を整えています。これにより、初心者から熟練のエンジニアまで、幅広い開発者層に対応可能です。RISC-Vベースの組み込み機器向けのパフォーマンス最適化では、特定用途向けのチューニングや、電力効率を重視した設計を提供し、IoTデバイスや産業機器向けの高度な開発環境の整備を進めています。(タイトルとアブストラクトは主催者が作成 発表者によるAbstractの準備が出来次第変更します。) |

Wei Wu | 上海苦芽科技有限公司(Shanghai Kubuds Technology Co., Ltd.) | |

16:00-16:20 | 20分 | E | ポスターセッションの講評と入賞者発表:ポスターセッションの参加者には表彰があります。優秀な発表に対する入賞者の選定が行われ、表彰されます。 | 中條 拓伯 | 教授, 国立大学法人 東京農工大学 知能情報システム工学専攻(日本) | |

16:20-16:50 | 20分 | – | 我が国の半導体・デジタル産業戦略について: 半導体は、デジタルトランスフォーメーション(DX)およびグリーントランスフォーメーション(GX)の観点から、我が国の将来にとって鍵となるテクノロジーです。経済産業省では、2021年に策定した「半導体・デジタル産業戦略」を基軸に、国内外の技術革新や市場動向に対応してきました。2023年6月では、地政学的リスクの増大や経済安全保障の重要性が高まる中、半導体サプライチェーンの強靭化、国内製造基盤の拡充、人材育成に重点が置いた戦略の改定を実施しました。本講演では、昨年12月に開催した半導体・デジタル産業戦略検討会議の内容を踏まえたアップデートについてご説明いたします。 |

齋藤 尚史 | 経済産業省 商務情報政策局 情報産業課・課長補佐 | ビデオ |

16:50-17:00 | 10分 | 東京大学d.labとTenstorrentの連携による次世代半導体技術者育成プログラム:東京大学のシステムデザイン研究センター(d.lab)は、半導体技術者の育成を目的として、米国のAIチップスタートアップ企業であるTenstorrent社との連携を進めています。この取り組みは、技術研究組合最先端半導体技術センター(LSTC)の一環として、2024年内にも日本の技術者をTenstorrent社に派遣し、AI向け半導体の設計業務に従事させる予定です。派遣期間は1~2年を想定しており、帰国後は日本国内の通信や自動車関連企業、研究機関での活躍が期待されています。このプログラムは、5年間で200人の技術者育成を目指しています。d.labは2024年4月から東京大学の学部横断型教育プログラム「半導体教育プログラム(SPIRIT)」を主導し、幅広く半導体の素養を身につけた人材の輩出に取り組んでいます。これにより、先端デバイスを用いた設計を担える人材の育成を目指しています(タイトルとアブストラクトは主催者が作成 発表者によるAbstractの準備が出来次第変更します。) | 池田 誠 | 東京大学(日本) | ビデオ | |

17:00-17:10 | 10分 | – | テンストレント最先端デジタルSoC設計人材育成/上級コースのご紹介:NEDO 「ポスト5G情報通信システム基盤強化研究開発事業/ 人材育成/最先端デジタルSoC設計人材育成」プロジェクトにてTenstorrent USA, Inc.が技術研究組合 最先 端半導体技術センター(LSTC)と共に採択され、Tenstorrentはその上級コースとしてシングルナノ半導体の設計人材育成コースとして先端半導体設計を実践しているシリコンバレーでのOJT (On the Job Training)を中心に実施することとなりました。本セッションでは会社概要、RISC-V CPU,AIアクセラレータなどの製品の概要に加え、人材育成プロジェクトの概要をご説明します。 | 中野 守 | 代表取締役社長 テンストレントジャパン株式会社(米国) | |

17:10-17:20 | 10分 | – | ISO26262認定チップを実現する RISC-V の価値 概要: SHD Group 2024の調査レポートでは、RISC-VベースのSoCの出荷数量は2030年に160億個を超えると予測されており、同じ調査でAndesは30%以上の市場シェアを持つ主要なRISC-V IPベンダーとしてランク付けされています。Andes独自の統計分析を確認すると、自動車アプリケーションはここ3年間で急成長しており、その重要性が高まっています。Andesは、堅牢な機能安全RISC-VプロセッサIP開発と品質保証フローにより、2020年に会社全体でISO26262 ASIL-D認証を取得するために長い準備期間を過ごしました。この講演では、プレゼンターがISO26262 ASIL-BおよびASIL-D認証を取得したAndesの機能安全RISC-Vプロセッサ、顧客の成功事例、今後数年間のロードマップを紹介します。自動車アプリケーションは現在急成長段階にあるため、新世代車両、新エネルギー車両向けのさまざまな自動車標準仕様の検証にRISC-Vを適用することも自動車業界のトレンドです。 ISO26262 認定の RISC-V プロセッサ IP は、SoC 設計の価値提案を実現するための鍵として考えられます。 | フランクウエル・リン | CEO and Chairman, アンデス テクノロジー (台湾) | |

| 17:20-17:30 | 10分 | 日英 | 終わりの言葉とRISC-V Day Tokyo 2025 Autumnの案内 | 河崎俊平 | RiSC-V協会 理事長(日本) | ビデオ |

| 17:30-18:00 | 30分 | – | 撤収 | TBD | – |

③ RISC-V 昼食交歓会

お弁当業者さんが本年2月末で廃業します。好きな弁当があれば、4桁の番号をメモしてきてください。箱をみれば、中味がわかるようにしておきます。

2376 山吹「やまぶき」 鶏の照り焼きと季節の煮物を盛り込んだお弁当です。

2377 稲荷詰合せ お稲荷さんと煮物のおかずを盛り込んだ軽食弁当です。

2375 高森「たかもり」 高森産の舞茸ご飯と鶏の唐揚げ。素材を活かした人気のお弁当です。

2374 トマトバーグと野菜デリ トマトハンバーグと野菜デリを彩りよく盛り込みました。

2237 鮭塩焼きと竹輪磯辺揚げ 人気の焼き魚と揚げ物を組み合わせたお弁当です。

2373 円山「まるやま」 脂ののった焼き魚と季節の煮物を盛り込んだお弁当です。

2371 2色そぼろ弁当 そぼろご飯に鶏そぼろと春雨サラダの相性抜群弁当です。

お弁当屋さん永らくありがとうございました。2025夏にどうなるかは、まだ、決まっていません。

④ RISC-V 技術展示

2025年2月27日 10:30-16:30

地下2階 ホワイエ、多目的スペース

展示者・内容は変更になる可能性がありますことをご了承ください

| ブース番号 | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| A | 11:00-16:30 | 新CPUコアの発表やアップデート、既存のNX27V、NX45 MPVなどのベクトルプロセッサの強化版や、新たなアウトオブオーダー型のアプリケーションプロセッサ(X66/X67)の詳細が紹介。ベクトル拡張(RVV)対応の最新技術を活かしたAI/ML、HPC、5G/6G通信向けの事例が示されるかもしれません。 車載向けソリューションやセキュリティ強化も重要なテーマとなるでしょう。AndesはISO 26262認証を取得したプロセッサを提供しており、機能安全(FuSa)対応の強化や、オートモーティブ市場向けの新しいIPが展示される可能性があります。また、AndroidやLinux環境でのRISC-Vサポートの進展にも言及し、エコシステムの強化をアピールするでしょう。さらに、カスタム命令(ACE: Andes Custom Extension)を活用した独自のAI/ML最適化事例や、セキュアブートやTEE(Trusted Execution Environment)に関する展示も予想されます。 開発ツールやエコシステムの充実も強調されるでしょう。SiFiveと同様に、開発者向けのIDE(統合開発環境)、コンパイラ最適化、シミュレータの強化が発表される可能性があります。また、新しい評価ボードや、パートナー企業との共同開発事例の展示が行われ、AndesのRISC-Vソリューションがさまざまな分野で実用化されていることを示すでしょう。 (以上は主催者説明) | アンデステクノロジー(台湾) | |

F | 11:00-16:30 | SiFiveは、RISC-VベースのプロセッサIPを中心に多彩な製品ラインアップを展開しており、3月の展示では新たなCPUコアや今後のロードマップが紹介される可能性があります。特に高性能コアのアップデートや、AI・DSP向けのベクトル拡張対応の最新動向が注目されるでしょう。また、車載向けの機能安全対応やサーバー/HPC向けマルチコア構成など、大規模システム分野への取り組みが示されることも考えられます。 あわせて、開発ツールやソフトウェアスタックの進化も重要なトピックとなりそうです。統合開発環境(IDE)やLinux/Androidサポート、セキュリティ機能などを強化した事例の紹介や、新しい評価用開発ボードの展示が期待されます。SiFiveはこれらの分野でエコシステムを強化し、RISC-Vアーキテクチャの普及促進をアピールすると予想されます。(以上は主催者説明) | サイファイブ(米国) | |

| G | 11:00-16:30 | Tenstorrent 最新AIハードウェア展示のご案内 概要:Tenstorrentの展示ブースでは、最新のAIハードウェアおよびソリューションを紹介いたします。ブース内には説明用PCとしてMacBook Airと27インチディスプレイを設置し、来場者に向けた製品説明やデモンストレーションを実施します。展示製品として、AI製品「QuietBox」およびPCIカード「N300」を展示し、Tenstorrentの技術力を直接ご覧いただけます。また、製品カタログとして「Ascalon IP」「Galaxy」「Workstation」「Wormhole」を用意し、各製品の詳細情報を提供します。さらに、ブース内には「CPU」に関するバナーおよび「Tensix」に関するバナーを掲示し、Tenstorrentの最新技術と取り組みについてご紹介します。デモンストレーションでは、「TT-Studio」を用いたAIモデル「Llama」または「DeepSeek 3.1-70B」を実行し、実際の動作を通じてTenstorrentの強力なAI推論性能を体感いただけます。ぜひTenstorrentのブースにお立ち寄りいただき、最先端のAI技術を直接ご覧ください。 | テンストレント(米国) |

| ブース番号 | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| 1 | 11:00-16:30 | JTAGデバッガ、コンパイラ、リアルタイムOS(RTOS)開発プラットフォームなどの組込みソフトウェア開発エンジニア向け開発環境 | 京都マイクロコンピュータ株式会社(Kyoto Microcomputer Co., Ltd.)(日本) | |

| 2 | 11:00-16:30 | エミュレータなどの組込みソフトウェア開発エンジニア向け開発環境 | DTSインサイト(日本) | |

| 4 | 11:00-16:30 | JASAチップ事前評価デモ、Chisel学習用VGA表示 | 一般社団法人 組込みシステム技術協会 (JASA) 技術本部 ハードウェア委員会 RISC-V WG(日本) | |

6 | 11:00-16:30 | オープン半導体 | ISHI会(日本) | |

7 | 11:00-16:30 | RISC-V CPU IP製品とソリューション: Nuclei Studio IDE、AIアプリケーション向けのNI900シリーズなど | Nuclei System Technology(芯来科技)(中国) | |

8 | 11:00-16:30 | RISC-VオープンソースIPデモ | 電気通信大学(日本) |

⑤ RISC-V研究とオープン半導体

2025年2月27日 13:00-

| 時間 | 発表時間 | 言語 | プレゼンテーション題名 | 発表者 | 所属機関 (with URL) | 講演資料 |

|---|---|---|---|---|---|

| 13:00- 13:10 | 10分 | – | 司会者の歓迎の言葉 {RISC-V研究とオープン半導体} | 天野 英晴 | 東京大学大学院情報理工学研究科 | – |

| 13:10- 13:40 | 20分 | – | RISC-V ソフトウェア エコシステム上の Linux: 概要: プレゼンターは、(1) RISC-V 上の Fedora/CentOS のステータス (リポジトリ ステータスとソフトウェア サポート RISC-V 開発ボードを含む) (10 分) について説明します。 | Wei Fu (傅 煒)| Red Hat Software (Beijing) Co.,Ltd. プラットフォーム イネーブルメント担当主席ソフトウェア エンジニア | RISC-V Foundation の RISC-V アンバサダー | ビデオ |

| 13:45- 14:05 | 20分 | – | RV64ILP32 Linux V3 パッチの革新的な機能 概要: RISC-V プロファイルのガイドにより、市場では、TCM、キャッシュ、メモリが制限されたリソース制約のある環境に導入される RVA(B) プロファイル ベースの SoC と CPU IP が急増しています。従来の LP64 ABI を採用すると、リアルタイム応答性、パフォーマンス、コスト管理に大きな課題が生じます。 そのため、これらのチップの製品化を支援するために、RV64ILP32 Linux を実装しました。これまでの実装と比較して、このバージョンでは Linux の完全な移植機能を提供します。たとえば、64lp64 アプリケーションのサポートや、rv64 固有の多くの機能などです。プレゼンテーション中にデモを配布し、プロジェクトへの参加を歓迎します。 | Guo Ren | スタッフエンジニア、Linux CPU サブシステム、Alibaba | Linux csky メンテナー (中国) | ビデオ |

| 14:10-14:30 | 20分 | – | Kubuds が切り拓く RISC-V 開発の未来: クロス ツールチェーンと最適化テクノロジー 概要: このプレゼンテーションでは、PLCT Lab の共同設立者兼プロジェクト ディレクターであり、RISC-V Foundation の専任 RISC-V アンバサダーでもある Wei Wu が、Kubuds のテクノロジーを通じて RISC-V 開発の未来を推進する実用的なイノベーションについて詳しく説明します。最先端のプラットフォームであり、その背後にある組織でもある Kubuds は、RISC-V 開発プロセスを合理化するためにカスタマイズされたいくつかの重要な機能を提供します。

Wei は、技術デモンストレーションとケース スタディを通じて、これらの機能によって、組み込みシステムから高性能コンピューティングまで、さまざまなアプリケーションで堅牢な最適化と効率性の向上が実現される仕組みを説明します。参加者は、Kubuds のツールと方法論が、進化する RISC-V エコシステムで測定可能なベンチマークを確立し、パフォーマンスの向上を促進する方法について、実践的な洞察を得ることができます。 | JingWei Wang | PLCT Lab の共同設立者兼プロジェクト ディレクター | RISC-V Foundation の RISC-V アンバサダー | ビデオ |

| 14:35-14:55 | 20分 | – | PulpプロジェクトのRISC-Vコア向けインターフェース 概要:SLMLET は、エッジ コンピューティングに有望なデバイスである低電力システム オン チップ (SoC) です。これは、RISC-V コアと、スケーラブル ロジック モジュール (SLM) と呼ばれる省面積の組み込みフィールド プログラマブル ゲート アレイ (eFPGA) ブロックで構成されています。この論文では、製造された SLMLET チップと開発された HW/SW 共同設計フローを紹介します。実験結果では、RISC-V コアが最大 300MHz で動作し、SLM ブロックのハードウェア設計が最大 100MHz で動作できることが実証されています。SLM ブロックに実装された専用回路に計算集約型のプロセスをオフロードすることで、RISC-V コアや他の市販のマイクロコントローラでのソフトウェア処理と比較して、最大 77% のエネルギー削減を実現できます。 | 天野 英晴、小島 拓也 | 東京大学大学院情報理工学研究科、久我 守弘 | 熊本大学情報工学部、奥原 颯 | シンガポール国立大学電気情報工学部、飯田 全広 | 熊本大学情報工学部(日本) | |

| 15:00– 15:30 | 30分 | – | 30 分間の休憩 | Bio Break |

| |

| 15:30- 15:40 | 10分 | 日 | CHERI ALLIANCE 101 | 明石 貴昭 | Country Manager – Japan, Codasip GmbH(ドイツ) | ビデオ |

| 15:40- 16:00 | 20分 | – | CHERIアライアンス:電子システムに改善されたセキュリティを組み込む 概要: CHERIアライアンスは、CHERI技術の採用と普及を通じて、メモリ安全性の問題を軽減することを目的としている。サイバーセキュリティのコストが増大し続ける現代社会において、メモリ安全性に起因する脆弱性は、全脆弱性の3分の2以上を占めている。CHERIは、メモリ・ポインタに境界と許可のメタデータを追加することでこれを解決します。CHERIアライアンスは、メンバーがCHERIの採用を促進、調整、サポートするために協力できる中立的な組織です。 Bio: Marno van der Maas 博士は、2022年にケンブリッジ大学でサイドチャネル攻撃から信頼された実行環境を保護する研究で博士号を取得した。この間、Capability Enhanced RISC Instructions (CHERI)と名付けられた技術を使用し、メモリポインタの境界とパーミッションを強制するプロセッサの実装とテストにも取り組んだ。LowRISC CICでは、Sonata CHERIoT開発プラットフォームおよびOpenTitanとSunburst全体の主要ハードウェアエンジニアを務める。検証やセキュリティに関する経験を活かし、オープンシリコンの実現というビジョンに貢献している。 | Presentor: Dr Marno van der Maas, Principal Hardware Engineer, lowRISC C.I.C. | |

| 16:05- 16:25 | 20分 | 英 | CHERI – メモリ安全アーキテクチャとコンパートメント化が実用化に向けて本格始動 Abstract: CHERIプロジェクトは、約14年前、ブレイク不可能なケイパビリティ・トークンを最新のRISCアーキテクチャと融合させる方法を検討することから始まった。最初のMIPSベースのプロトタイプは、C/C++のポインターをケイパビリティにコンパイルできること、効率的な共有でプログラム・コンポーネントを分離できること、さらにバウンズメタデータを効率的に圧縮する方法を教えてくれた。Armとのコラボレーションは、Morelloチップへと発展し、現在では、空間的にも時間的にも安全で、すべてのライブラリの自動コンパートメント化を可能にする大規模なデスクトップおよびサーバーも実行できている。ハードウェアでもソフトウェアでも、多くの教訓が得られた。 マイクロソフト社のCHERIoTやCodasip社の700ファミリーを含む、最初の商用CHERI実装と平行して、我々は現在CHERI-RISC-Vの批准に近づいている。本講演では、CHERI のコンセプトと保証の基本、CHERI 実装ファミリーの興味深いマイクロアーキテクチャの特徴、および現在の CHERI-RISC-V の批准に向けた取り組みの詳細について説明します。 Bio: Jonathan Woodruff博士は、プロセッサアーキテクチャとマイクロアーキテクチャ、および低レベルソフトウェアの最適化を専門とするシニアリサーチアソシエイトです。ケイパビリティ・プロセッサ設計を専門とし、キャッシュ階層、コアタイミング、マルチコア設計を含むフルシステム最適化、制御フローインテグリティやプライベート実行を含む主要なセキュリティアプローチの探求に取り組んでいます。 | Dr Jonathan Woodruff, Senior Research Associate | 英ケンブリッジ大学(英国) | |

| 16:30- 16:50 | 20分 | 英 | CHERI_RISC-Vの標準化 Abstract: CHERIタスク・グループは、RISC-V ISAでCHERIをサポートする拡張機能を提案するために、RISC-V International内に組織された。これらの拡張の動機は、Microsoft’s Security Response Center (MSRC)がレポートした、ソフトウェアの脆弱性の70%以上を占めるメモリ安全性の問題に対処して、RISC-Vを強化することである。本プレゼンテーションでは、CHERI TGの現在および将来の作業の概要と、CHERI拡張機能の仕様策定状況について説明する。 Bio: Tariq Kurdは、主に組み込み分野で20年以上にわたってCPUアーキテクチャ、設計、検証に携わってきた。VLIW、マルチスレッド、アウトオブオーダーコア、セキュリティ、DSPスタイルのコアに携わった。Codasipには3年以上在籍しており、以前はHuawei UK、Broadcom、Nvidiaに在籍した。これまでTariqは、RISC-V InternationalのZfinx、およびコードサイズ削減タスクグループの議長を歴任した。 | Tariq Kurd | Distinguished Engineer and Lead IP Architect, Codasip英国デザインセンター 所属(ドイツ) | ビデオ |

| 16:55- 17:15 | 20分 | 日 | CHERI – どのように機能するのか? 概要: このプレゼンテーションでは、CHERIがCodasip X730 RISC-V Core FPGA評価キットでどのように動作するかストーリーボード形式で紹介します。 Bio: 1990年代前半にケイデンス社で日本最初のVerilog-XL FAEとして、Verilog (IEEE std. 1364-1995)標準化、そして2000年代前半にシノプシス社でSystemVerilog (IEEE std. 1800-2005)標準化、UVMの前進であるVMMのエバンジェリスト、JEITA(旧EIAJ)標準化委員として活動し、約30年以上日本の半導体設計に関わってきました。Codasipの日本カントリー・マネージャーとして4年目となる。 | 明石 貴昭 | Country Manager – Japan, Codasip GmbH(ドイツ) | ビデオ |

| 17:15- 18:00 | 45分 | ー | 撤収 | スタッフ |

⑥ AI、RISC-V研究ポスター発表

2025年2月27日 11:35-15:00

技術展示場所 :Location No. RISC-V ポスター 展示 (ホワイエ)の配置図を参照ください。

| 枠 | 発表時間 | 言語 | 出展テーマ | 発表者 | 所属機関 | ポスター | |

|---|---|---|---|---|---|---|

| P1 | 11:35- 15:00 | 英 | SAIL-RISCV メモリモデルのリファクタリング 概要:Sail-RISCV は RISC-V ISA の最適なモデリング手法として広く認識されています。しかし、Sail-RISCV のメモリモデルには、以下の 2 つの主要な制約が存在します。①RV32 における 34 ビット物理アドレスの未対応 ②物理メモリと仮想メモリの曖昧さ これらの課題を解決するために、Sail-RISCV のメモリモデルの再構築を行いました。具体的には、『新しい型構造(type constructs)』を導入し、物理メモリと仮想メモリを明確に区別します。 |

Mingzhu Yan, Shuo Huang, Jian Guan, Yunxiang Luo | プログラミング言語およびコンパイラ技術研究所、ISCAS (中国) | – | |

| P2 | 11:35- 15:00 | 英 | RuyiSDK – RISC-V ソフトウェア開発のための統合・カスタマイズ可能なツールキット 概要:RISC-V ISA の設計は、多様なエコシステムの発展を促進してきました。しかし、ベンダー独自の拡張の導入により、ツールチェーンの管理やソフトウェアの適応が困難になる可能性があり、開発者にとっての課題となっています。本論文では、これらの課題を解決するために開発された RuyiSDK を紹介します。RuyiSDK は RISC-V 開発者向けの包括的なソリューションであり、以下の特徴を備えています。①既存の基盤ソフトウェアを統合し、サポートされていないアプリケーションの適応を促進 ②ツールチェーン、エミュレータなどを統合した パッケージインデックス を提供 ③クロスプラットフォームビルドや RISC-V ソフトウェアとボードの共同開発を支援するプロファイルファイルの管理。 RuyiSDK の意義と効果:柔軟で効率的な クロスプラットフォーム開発環境 を提供。RISC-V ハードウェアの可能性を最大限に引き出す ことに貢献。エコシステムの断片化(フラグメンテーション)を抑え、開発者がイノベーションに集中できる環境を構築。RuyiSDK により、RISC-V ソフトウェア開発の生産性と利便性が向上し、より強力な開発者コミュニティの形成が促進されると期待しています。 |

Weilin Cai, Yilin Chen, Yunxiang Luo | 中国科学院ソフトウェア研究所プログラミング言語およびコンパイラ技術研究室 (ISCAS) (中国) | – | |

| P3 | 11:35- 15:00 | 英 | 次世代の関心を引き付ける: ショートビデオによる ISCAS の RISC-V 教育 アブストラクト:中国科学院ソフトウェア研究所のインターンシップ プログラムは、革新的なショートビデオ コンテンツを通じて RISC-V テクノロジの教育とプロモーションを強化することに専念しています。「RISC-V を理解する」シリーズなどのプロジェクトでは、複雑な概念を簡素化してわかりやすくする一方、MilkV Duo や LicheePi などのプラットフォームでのハンズオン デモンストレーションでは、学生、教育者、エンジニア志望者など、幅広い視聴者の関心を引きます。このプロセスは、インターンが徹底的な調査を実施して既存の RISC-V コンテンツのギャップを特定することから始まります。この基礎は、スクリプト作成と制作の段階に反映され、インターンは技術情報と実践的なデモンストレーションを融合します。これらのビデオは、理論的な側面を説明するだけでなく、RISC-V テクノロジの実際のアプリケーションを強調し、初心者にとって威圧的な可能性のある主題をわかりやすくするのに役立ちます。視聴者のフィードバックは、ビデオの改善に重要な役割を果たし、視聴者の学習ニーズに効果的に対応できるようにします。この反復的なプロセスは、有益で魅力的なコンテンツの作成に役立ちます。これらのビデオは、学習者を基本原理から複雑なアプリケーションに導き、RISC-V の深い理解を促すための足がかりとなります。この進歩により、学習者は自分のペースで進み、自信が深まるにつれて詳細なトピックを探求することができます。この取り組みは、RISC-V などの最先端技術をコア教育カリキュラムに統合し、これらの技術への積極的な関与を促進するという ISCAS の使命をサポートしています。複雑なエンジニアリングの概念をアクセス可能な教育コンテンツに変換することにより、PLCT Lab は急速に進化する技術環境で活躍できるエンジニアの世代を育成し、RISC-V の世界的な採用を促進しています。 |

Fuyuan Zhang, Tianwei Jiang, Yunxiang Luo | 中国科学院ソフトウェア研究所プログラミング言語およびコンパイラ技術研究室 (ISCAS) (中国) | – | |

| P4 | 11:35- 15:00 | 英 | BOSC での UnityChip 検証オープンソース RISC-V 検証 Abstract: オープンソース ハードウェア エコシステムの拡大により、より幅広い検証参加者を巻き込むことでハードウェア検証の効率を高める新たな機会が生まれています。ソフトウェア テスト エコシステムは、大規模なコミュニティによって開発されたさまざまなツールや方法の恩恵を受けてきたため、この成功は、ソフトウェア テスト開発者を組み込むことでハードウェア検証をスケールアウトできる将来性を示しています。ハードウェア検証においてソフトウェア開発者をサポートするために、この統合を容易にする 3 つの手法を提案します。(1) 状態マシン抽象化 (サイクル精度および緩やかなタイミング) の提供、(2) ハードウェア設計を複数のプログラミング言語のソフトウェア パッケージにカプセル化、(3) ソケット データ転送と双方向直接関数呼び出しの導入です。これらの手法は CollabChip Verification (CCV) プラットフォームに実装されており、ソフトウェア開発者とツールがハードウェア検証ワークフローに参加し、ハードウェア フレームワークを使用してハードウェア エンジニアと共同作業を行うことができます。XiangShan プロセッサで手法を評価し、ケース スタディを通じて CCV の有効性を実証しました。ハードウェアの経験がないソフトウェア開発者が 2 か月で 11 個のバグを発見しました。経験ゼロの開発者が 20 時間で有効な検証ケースを提出し、平均開始時間を 77% 削減し、Python で既存の検証環境を強化してプロセスを 16.6% 加速し、コード行数を 12% 削減しました。 | Xu An | Beijing Institute of Open Source Chip, Yunlong Xie, Zhicheng Yao | Institute of Computing Technology (ICT), Chinese Academy of Sciences (CAS) | ||

| P5 | 11:35- 15:00 | 英 | RISC-V ボードおよび OS サポート マトリックス: RISC-V 開発者向けの包括的なリソース 概要: 現在、市場には RISC-V ボードが数多く存在し、ボードの製造元とコミュニティの両方から多数のオペレーティング システム (OS) が提供されています。しかし、RISC-V を初めて使用する人は、RISC-V ボードとその OS サポート状況に関する最新情報にアクセスするのが難しい場合があります。このニーズに対応するため、このホワイト ペーパーでは、RISC-V 開発者と愛好家を支援するためのサポート マトリックス プロジェクトを開始しました。RISC-V ボードおよび OS サポート マトリックスは、RISC-V 開発ボードとオペレーティング システム間の互換性をカタログ化するオープン ソースの取り組みであり、RISC-V ハードウェア プラットフォームと互換性のあるソフトウェアを選択する際に開発者をガイドする、整理された簡単にアクセスできるデータベースに対する高まる要求に応えています。このイニシアチブでは、「ヘルプの要請」(CFH)、「テストの要請」(CFT)、「進行中の作業」(WIP)としてマークされた構成など、コミュニティの支援が必要な領域を強調しています。さらに、メタデータ解析および SVG 生成用のツールが含まれており、互換性データの維持と視覚化に役立ちます。このイニシアチブは、RISC-V のフルスタック開発環境を提供することを目的とした、より広範な RuyiSDK プロジェクトの一部です。このイニシアチブでは、パッケージ マネージャーやグラフィカル統合開発環境(IDE)などのツールが統合されています。最新のハードウェアとソフトウェアの互換性データを提供することで、このイニシアチブは RISC-V エコシステムの開発者と研究者の意思決定を簡素化します。RISC-V ボードおよび OS サポート マトリックスは、RISC-V ボードへのオペレーティング システムとソフトウェアのインストールを容易にするために開発されており、初心者にとってプロセスの複雑さを軽減し、RISC-V ソフトウェア エコシステムの開発を促進します。 | Jingkun Zheng, Yunxiang Luo | 中国科学院ソフトウェア研究所プログラミング言語およびコンパイラ技術研究室 (ISCAS) (中国) | – | |

| P6 | 11:35- 15:00 | 英 | RISC-Vの魅力:学生からエンジニアへの成長の道 Abstract: さまざまな大規模 AI モデルの実装に伴い、AI モデルのトレーニングと推論の最適化はますます重要なタスクになっています。アセンブリ命令セットは、高レベルプログラムと低レベルチップ実行のインターフェイスとして、最適化において重要な役割を果たし、プロセスのボトルネックとブレークスルーポイントの両方になることがよくあります。RISC-V はこの分野で独自の利点を提供します。オープンソースの命令セットであり、スケーラビリティが高く、ベクトル計算を特別にサポートしています。したがって、AI モデルの展開環境を活用することで、RISC-V エコシステムの開発を加速できます。現在、RISC-V 命令セットの独自の利点についての認識を高めることが不可欠です。まず、さまざまなチャネルを通じて RISC-V の特徴を学生コミュニティに宣伝します。トレンドを追う学生の熱意を利用して、最新のオンライン要素をビデオ制作に統合し、学習の敷居を下げ、エンゲージメントを高めます。これらのビデオはソーシャルプラットフォームやオンライン教育チャンネルを通じて広く配信され、すぐに学生の注目を集めます。次に、RISC-V命令セットに対する学生の関心が高まるにつれて、学生は関連する技術ビデオを積極的に検索します。このプロセス中に、PLCTが提供する詳細な技術コンテンツは、学生とエンジニアがRISC-Vの詳細とアプリケーションをさらに理解するのに役立ちます。特に、RISC-Vシミュレーターを開発することで、学習者はコンピューターアーキテクチャの基本原理を直感的に把握し、ハードウェア命令実行のプロセスを理解できます。より多くの学生が実際の開発に参加するように導くことで、RISC-Vに対する理解を深め、技術コミュニティの活動を効果的に促進し、より多くの若いエンジニアがRISC-Vエコシステムに参加するという**好循環**を生み出すことができます。最終的には、RISC-Vに情熱を注ぐ若くて活気のあるエンジニアのコミュニティが育まれるでしょう。 RISC-Vのオープンソース性とスケーラビリティを活用することで、大規模なAIモデルの導入はRISC-Vエコシステムとコミュニティの発展にとって貴重な機会となり、より多くの学生やエンジニアを引き付け、その成長に貢献することになります。 |

| ||

| P7 | 11:35- 15:00 | 英 | RISCOF を通じた ACT に対する FCVT のサポート 概要:RISC-Vプロセッサモデルの数が増え続けるにつれて、RISC-VプロセッサがISA仕様に準拠しているかどうかを確認することが重要な課題になっています。ACTテストに使用される公式テストツールとして、RISCOFはSail-RISCVモデルをリファレンスとして活用し、テスト対象モデルが仕様に準拠しているかどうかを確認できます。ただし、RISCOFが使用するACTテストリポジトリには、`fcvt.d.h`などのzfh拡張機能のいくつかのテストケースを含む、多くのテスト命令と拡張機能のサポートがありません。したがって、この問題に対処するために、RISCOFに新しいテスト命令のサポートを追加します。RISCOFは、テスト開発に複数のテストツールに依存しています。これには、テストケースを生成するためのRISCV-CTGと、カバレッジテスト用のRISCV-ISACが含まれます。新しいテスト命令をサポートするには、RISC-V CTGにテスト命令のYAMLノードを追加して定義し、命令に対応するCGFファイルを作成する必要があります。次に、新しい命令のカバレッジ検出をサポートするために、ISAC のデコーダーに関連命令チェックを追加します。その後、生成されたテスト ケースで RISCOF を実行すると、テスト結果が正確であることが示されます。RISCOF を介して ACT にテスト命令のサポートを追加することで、テストの柔軟性が向上し、ACT テストの包括性と精度がさらに向上します。 | Zhu Xuchang, Luo Yunxiang | 中国科学院ソフトウェア研究所プログラミング言語およびコンパイラ技術研究室 (ISCAS) (中国) | ||

| P8 | 11:35- 15:00 | 英 | 教育におけるRISC-V:オープンソース学習プラットフォームを通じて次世代のエンジニアを育成 概要:コンピュータ技術の急速な発展に伴い、新世代のエンジニアの育成は教育分野における重要な課題となっています。従来の教育モデルでは、ハードウェアとソフトウェアの相互作用を包括的に理解することができません。そのため、RISC-Vのオープンソースアーキテクチャを導入することで、学生にコンピュータアーキテクチャのコア知識を迅速に把握するためのより実用的で革新的な学習プラットフォームを提供できます。この論文では、RISC-Vオープンソースアーキテクチャを教育ツールとして採用し、コンピュータアーキテクチャとハードウェア設計の教育に適用します。RISC-Vのオープンソースの性質により、学生はコンピュータハードウェアの設計に直接関わり、下位層と上位層の間の相互作用と通信のメカニズムを迅速に理解できます。その結果、クロスコンパイル、オペレーティングシステム、および関連知識の研究を通じて、学生はコンパイラやその他の関連コンテンツをより深く理解することができます。RISC-Vを教育分野に導入することで、エンジニアは学生に効率的でオープンな学習プラットフォームを提供し、コンピューターアーキテクチャとハードウェア設計の重要なスキルを迅速に習得できるようにします。この教育イニシアチブは、学生の技術力の向上だけでなく、次世代のエンジニアの育成を強力にサポートし、将来の技術革新と産業の発展のための強固な基盤を築きます。 | Zhi Li, Fuyuan Zhang, Yunxiang Luo | プログラミング言語およびコンパイラ技術 (PLCT) ラボ、中国科学院ソフトウェア研究所 (中国) | ||

| P9 | 11:35- 15:00 | 英 | オープンソースハードウェアとRISC-V:コスト削減とイノベーションを通じてデジタルデバイドを解消し、社会的平等を推進 概要:コンピュータ技術の急速な発展に伴い、新世代のエンジニアの育成は教育分野で重要な課題となっています。従来の教育モデルでは、ハードウェアとソフトウェアの相互作用を学生に包括的に理解させることができないことがよくあります。そのため、RISC-Vのオープンソースアーキテクチャを導入することで、学生にコンピュータアーキテクチャのコア知識を迅速に把握するためのより実用的で革新的な学習プラットフォームを提供できます。この論文では、RISC-Vオープンソースアーキテクチャを教育ツールとして採用し、コンピュータアーキテクチャとハードウェア設計の教育に適用します。RISC-Vのオープンソースの性質により、学生はコンピュータハードウェアの設計に直接関与し、下位層と上位層の間の相互作用と通信のメカニズムを迅速に理解できます。その結果、クロスコンパイル、オペレーティングシステム、および関連知識の研究を通じて、学生はコンパイラやその他の関連コンテンツをより深く理解できます。RISC-Vを教育に導入することで、教育分野では、エンジニアは学生に効率的でオープンな学習プラットフォームを提供し、コンピューターアーキテクチャとハードウェア設計の重要なスキルを迅速に習得できるようにします。この教育イニシアチブは、学生の技術能力を向上させるだけでなく、新世代のエンジニアのトレーニングを強力にサポートし、将来の技術革新と産業の発展のための強固な基盤を築きます。 | Zhi Li、Fuyuan Zhang、Yunxiang Luo | 中国科学院ソフトウェア研究所プログラミング言語およびコンパイラ技術ラボ (ISCAS) (中国) | – | |

| P10 | 11:35- 15:00 | 英 | SPECCPU2017 における RISC-V のコンパイラ パフォーマンスの比較分析 要約: 命令数を基準として、SPEC CPU 2017 を使用して、RISC-V で GCC と LLVM でコンパイルされたプログラムのパフォーマンスを比較しました。特に RISC-V ベクトル拡張に重点を置きました。ベンチマークは QEMU を使用して並列実行され、大規模なテストが可能になりました。分析の結果、INT レートと FP レートの両方で、LLVM でコンパイルされたテストの方が GCC でコンパイルされたテストよりも多くの命令が実行されました。ベクトル拡張を有効にすると、FP レートの差が大幅に縮まり、特定のシナリオでは LLVM の自動ベクトル化のパフォーマンスが向上することが示唆されました。 | Yongtai Li、Chunyu Liao、Ji Qiu | 中国科学院ソフトウェア研究所プログラミング言語およびコンパイラ技術ラボ (中国) |

| |

| P11 | 11:35- 15:00 | 英 | 2024 年の RISC-V 向け V8: 新機能 概要: このポスターでは、2024 年の RISC-V アーキテクチャ向け Chromium V8 JavaScript エンジンの進捗状況をまとめています。V8 の RISC-V バックエンドのメンテナーである PLCT Lab は、合計 173 のパッチで 17,000 行を超えるコードを貢献しました。これは、すべての貢献チームの中で 5 位です。まず、新しい JavaScript および WebAssembly (Wasm) 言語機能が追加されました。これには、Wasm の管理対象オブジェクトとガベージ コレクション、API 呼び出しの強化、スタック管理の改善が含まれます。次に、ポインター圧縮、新しいジャストインタイム コンパイラー (Maglev)、Wasm での最適化された間接呼び出し、および構成可能なサンドボックスや制御フロー整合性 (CFI) などのセキュリティ機能によって、一般的なパフォーマンスが向上しました。最後に、RISC-V ISA 拡張機能を活用してジャンプと組み込みコード生成を改善し、コード サイズを削減する大幅な最適化が実装されました。最後に、I キャッシュ フラッシュを含む SV39/SV48 構成とマルチコア環境のサポートが追加されました。ベンチマーク結果では、パフォーマンスの顕著な向上が実証されています。今後の作業には、アップストリームの継続的な追跡と、LeapTiering や Maglev などの機能のサポートの拡張が含まれます。 | Yahan Lu、Ji Qiu | 中国科学院ソフトウェア研究所プログラミング言語およびコンパイラ技術 (PLCT) ラボ |

| |

| P12 | 11:35- 15:00 | 英 | AI/ML アプリケーション向け RISC-V SoC のデータ転送アーキテクチャの最適化 概要: このプレゼンテーションでは、組み込みビジョン アーキテクチャのコンテキストにおける人工知能/機械学習 (AI/ML) のデータ転送アーキテクチャの課題とソリューションを示し、RISC-V ベースのシステム オン チップ (SoC) のネットワーク オン チップ (NoC) の実装の側面について説明します。AI/ML および組み込みビジョン アーキテクチャでは、データ転送アーキテクチャにおいて、オフチップ DRAM からすべての関連データを取得し、キャッシュに効率的に保存して転送することで、SoC およびチップレット システムでの効率的なコンピューティングを可能にするという、独自の課題があります。これらの課題は、NoC 実装の特定の要件に直接つながり、パフォーマンス、消費電力、コストに影響を与え、業界で「メモリ ウォール」と呼ばれる、プロセッサと DRAM のメモリ アクセス速度の大幅な向上によってもたらされる課題に効率的に対処します。さらに、自動車および産業用アプリケーションの分野では、ISO26262 および関連認証を取得するために、安全性と回復力に関する特別な考慮が必要です。 | ミハル・シウィンスキー |アルテリス(アメリカ) |

| |

| P13 | 11:35- 15:00 | 英 | ハイパーバイザ技術を用いたRISC-V拡張機能の容易な利用システムの開発 概要: RISC-Vでは、拡張機能と呼ばれるモジュール仕様が次々と開発されていますが、ハードウェア実装が追いつかず、活用されずに放置されたままになっている拡張機能が多くあります。 | 高名憲正、大山善弘 |筑波大学 (日本) |

| |

| P14 | 11:35- 15:00 | 英 | RISC-V プラットフォーム向け統合 GPU ソリューションの選択とジレンマ 概要: 今回は、RISC-V プラットフォーム向け統合 GPU 分野の大手 IP プロバイダーである Imagination のビジネス展開、開発者とそのクライアントの動向、Linux ディストリビューションへの適応の難しさ、IMG の最も批判されている技術サポートに焦点を当てます。また、当社が主催する「虹ヶ咲学園イマジネーションクラブ」の情報もお届けします。 | Jingyu Pu | PLCT ラボ (プログラミング言語およびコンパイル技術ラボ) (中国) |

| |

| P15 | 11:35- 15:00 | 英 | RevyOS: XuanTie チップ エコシステム向けに Debian を最適化 – RISC-V 適応における課題と成果 概要: RevyOS は、XuanTie チップ エコシステム向けに特別に最適化したカスタマイズされた Debian ベースのディストリビューションで、RuyiSDK チーム内のサブグループである RevyOS チームによって開発および保守されています。このプレゼンテーションでは、Linux ディストリビューションをさまざまな RISC-V ハードウェア プラットフォームに適応させる際の課題と方法論について検討し、RevyOS の現在の成果を紹介します。 | Han Gao、Xuan Chen | PLCT ラボ (プログラミング言語およびコンパイル技術ラボ) (中国) |

| |

| P16 | 11:35- 15:00 | 英 | ベクトルからマトリックスへ: RISC-V マトリックス拡張の将来 概要: 人工知能と機械学習から生まれた新しいマトリックス ワークロードを加速するというアイデアは、x86-64 (AMX) や ARMv9.2 (SME) などの汎用 ISA、および NVIDIA Tensor Core などのアクセラレータに実装されています。RISC-V は、オープンソース ISA として、このトレンドに従い、複数のマトリックス拡張ドラフトと実装が利用可能になっています。このポスターでは、Spacemit の統合マトリックス拡張と、Xuantie、Stream Computing、および SiFive (Zvma) のアタッチド マトリックス拡張を紹介します。このポスターでは、「統合」と「アタッチ」のトレードオフ、既存の V 拡張とマトリックス拡張の関係、および RISC-V マトリックス アクセラレーションの潜在的なハードウェア実装に焦点を当てます。 | ヤン・ルー | 東京大学(日本) |

| |

| P17 | 11:35- 15:00 | 英 | カスタム RISC-V ベクトル拡張を使用した DNN トレーニングにおける効率的な転置行列乗算 概要: ディープ ニューラル ネットワーク (DNN) では、行列演算の最適化がパフォーマンスとエネルギー効率の向上に不可欠です。オープンソースの RISC-V 命令セット アーキテクチャ (ISA) は、データ並列アルゴリズムを高速化するベクトル拡張をサポートしています。この研究では、RISC-V の既存のベクトル乗算加算命令とともにドット積命令を導入することで、DNN トレーニングにおける効率的な転置行列乗算の新しいアプローチを提案します。 バックプロパゲーション中は、フォワード パスからの行列を転置する必要があります。メモリ内で実際にデータを移動せずに異なる順序でデータにアクセスすることで転置を実行することは可能ですが、これには通常、連続していないアドレスからのベクトル ロードが必要であり、連続したベクトル ロードと比較してレイテンシの隠蔽が難しくなります。したがって、ベクトル乗算加算およびドット積演算のレジスタ内で行列要素がどのように方向付けられるかに焦点を当て、これにより、連続アドレスのベクトル ロードのみを使用して、バックプロパゲーションで転置行列乗算を実行できるようになります。 提案された方法のハードウェア リソースは FPGA 実装によって評価され、ベクトル乗算加算とドット積演算の両方で同じ機能ユニットを共有できることが実証されました。実装されたコアを使用して行優先行列と列優先行列を乗算した結果、ドット積アプローチでは、ベクトル乗算とベクトル減算和命令を組み合わせた場合と比較して必要なサイクル数が削減され、ベクトル乗算加算アプローチと比較してメモリ アクセスも削減されました。これらの結果は、RISC-V ベクトル プロセッサで DNN ワークロードを最適化するためのドット積命令の可能性を強調しています。 | 安藤 陸 | 東京理科大学 電気工学科 河原研究室 (日本) |

| |

| P18 | 11:35- 15:00 | 英 | 近似演算処理要素を使用した RISC-V ベースの AI アクセラレータ設計 概要: 近年、人工知能 (AI) の研究開発 (R&D) が飛躍的に増加しています。これに伴い、AI タスクの電力需要も前例のない速度で増加しており、AI アプリケーション専用のハードウェアの R&D 作業が増加しています。このポスターとデモでは、近似演算処理要素 (PE) を使用した人工知能 (AI) アクセラレータ設計を、近似演算テクノロジとシストリック アレイ実装を備えた Cassia.ai と共同で紹介し、LeNet 畳み込みニューラル ネットワーク (CNN) を使用して手書き数字認識タスクを実行します。この設計では、シストリック アレイ内の PE に従来の絶対演算を使用する代わりに、これらの PE に近似演算を適用することを提案しました。この提案は、ほとんどの AI およびディープラーニング実装では、近似計算を使用して正規化、特徴選択、ドロップアウトなどのモデルの複雑さを軽減し、消費電力を削減しているという事実に基づいています。この設計では、近似演算技術を実証するための技術ベースとして、カリフォルニア大学バークレー校の Chipyard 設計フレームワークとカリフォルニア大学バークレー校の Gemmini シストリック アレイを採用しています。LeNet モデルを使用した予備テストでは、元の Gemmini シストリック アレイ設計と比較して、予測精度とパフォーマンスに大きな低下は見られませんでした。 | ゴック・ラム・グエン、チョン・トゥック・ホアン、範 公可 | 電気通信大学 |

| |

| P19 | 11:35- 15:00 | 英 | Ripes RISC-V シミュレータの拡張 概要: Ripes は、RISC-V 命令セット アーキテクチャ用のグラフィカル プロセッサ シミュレータです。各命令の実行におけるマイクロアーキテクチャ コンポーネント間のさまざまな操作を視覚化します。RISC-V をコンピュータ アーキテクチャの研究の基盤として使用する場合、spim などの他のプロセッサ シミュレータの優れた代替手段となるはずです。 このプロジェクトでは、RISC-V ベースのシステムにおけるソフトウェアとハードウェアの相互作用に焦点を当てています。特に、関数呼び出しがどのように実装されているかをよりよく理解できるように、スタック セグメントの視覚化が Ripes シミュレータに追加されています。 スタック セグメントは、関数呼び出し引数、関数呼び出し内のローカル変数、および呼び出し元関数への戻りアドレスを渡すために使用されます。 これらの情報を表示するために、Ripes にスタックのタブを追加しました。libdwarf からの情報を利用することで、ローカル変数名が取得され、スタック タブに含められます。 libdwarf からのこのデバッグ情報は、呼び出しフレームの戻りアドレスの横に呼び出し関数名を表示するためにも使用されます。関数呼び出しのフレームを表示するテーブルは、呼び出しごとに作成され、関数から戻ると削除されます。 Clock や Run などの元の実行制御ボタンに加えて、現在の C ソース コード行の RISC-V 命令の実行が完了するまで Ripes を実行し続ける C-Step ボタンを追加しました。このボタンを使用すると、関心のある命令にすばやく移動できます。 | 大井仁、東大地 |会津大学 (日本) |

| |

| P20 | 11:35- 15:00 | 英 | マルチスレッド用の RISC-V ベースのマルチコア プロセッサ: ハードウェアからソフトウェアへの設計観点 概要: この研究では、データ中心の時代に合わせて調整された RISC-V ベースのマルチコア プロセッサ システムの設計を検討し、汎用アーキテクチャと専用アーキテクチャの間のギャップを埋めます。ビッグ データの処理における従来のアプローチの限界を認識し、この研究ではハードウェアとソフトウェアの両方を含む共同設計アプローチを強調しています。 提案されたアーキテクチャは、スレッド キューを介して他のコアに分散されるスレッドを生成する高性能コアを備えています。プライベート作業スペースと双方向プライベート バスにより、共有リソースの競合とデータ移動のオーバーヘッドが最小限に抑えられます。重要な革新は、密結合アクセラレータのキャッシュとローカル/共有メモリの両方として機能するハイブリッド L1 キャッシュによるニア キャッシュ処理機能の統合です。これにより、データをメモリの近くで処理できるため、帯域幅の使用率が最大化されます。 行列乗算のベンチマーク結果では、4 コア構成で 4 ~ 6 倍、8 コア構成で 6 ~ 18 倍の高速化が達成されています。ハイブリッド L1 キャッシュを活用する密結合アクセラレータは、単一コアと比較して 24 倍から 177 倍を超える驚異的な高速化を実現します。 | ビン・キウ・ド・グエン、カイ・ズイ・グエン、範 公可、チョン・トゥク・ホアン | 電気通信大学 |

| |

| P21 | 11:35- 15:00 | 英 | マルチコアおよび V 拡張 RISC-V プロセッサの評価 概要: コンピューティング ワークロードが複雑になるにつれて、特に ARM または x86 ベースの確立されたシステムでは、マルチコア プロセッサ アーキテクチャが広く普及しています。サーバー、PC、さらにはモバイル デバイスでも、2000 年代初頭から、3D レンダリングやビデオ トランスコーディングなどのさまざまなワークロードのパフォーマンスを向上させるために、並列処理が採用されています。CPU プロセッサの並列処理には、マルチコアと SIMD (Single-Instruction-Multiple-Data) の 2 つのアプローチがあります。RISC-V は、V 拡張を介してマルチコアと SIMD の両方をサポートするオープン命令セット アーキテクチャです。ただし、RISC-V ベースのシステムでの並列処理アプローチを対象とするベンチマークの数が不足しているため、実装間の比較が困難です。そのため、RISC-V システムのスケーラビリティを評価する方法が重要です。この研究の目的は、マルチコアとV拡張対応RISC-Vベースシステムの両方でこれらに対する性能評価を行うことである。マルチコアシステムの場合、RV32IMAC(1〜16コア)およびRV64GC(1〜8コア)Rocket Coreは、Xilinx VC707 FPGAプラットフォーム上のChipyardフレームワークを使用して生成されます。Linuxソフトウェア環境では、合成ベンチマークは、コア数が増えるにつれて線形性能向上を達成することを示唆していますが、グラフの色付けなどのより具体的なワークロードの場合、シングルコアバリアントと比較して、16コアRV32IMAC構成では8.32倍、8コアRV64GC構成では5.84倍の高速化にすぎません。一方、VLEN 128のV拡張Zve32xを備えたRISC-Vコアの場合、初期ベンチマークでは、スカラーコアと比較して最大20倍の高速化で画像処理ワークロードのメリットが得られることが示されています。 | ザ・ビン・グエン、チョン・トゥク・ホアン、範 公可 | 電気通信大学 (UEC) (日本) |

| |

| P22 | 11:35- 15:00 | 英 | オープン半導体設計における自作セルライブラリ活用のためのライブラリキャラクタライザの開発 概要: オープン半導体設計とそれをサポートするオープン EDA および設計環境は数多く提案されているが、これらの環境は特定のファブが提供するセルライブラリを使用して回路設計を行うことを前提としている。これらの環境に自作セルライブラリをロードするには、セルライブラリの遅延特性や電力特性を抽出してライブラリを作成し、キャラクタライザとして機能させる EDA であるキャラクタライザが必要である。ここでは、我々が開発しているキャラクタライザのオープンソース実装の現状について報告する。 | 西沢 新一 |早稲田大学 / ISHI-KAI (日本) |

| |

RISC-V関連 日本語出版物

購入希望の方は書籍写真をクリック

[単行本] 日本の半導体戦略と電子地政学2024を読む: RISC-V と Googleオープン半導体の動向 2024/1/16 1500円(税込)・1364円(免税)¥1,364(免税)¥3,000

[単行本] Google半導体とRISC-Vと世界の電子地政学ー米国国防省がアジア地域で展開する柔らかい半導体戦略 2023/06/20 2000円(税込)・1818円(免税)¥1,818

[単行本] Google半導体とRISC-Vと世界の電子地政学ー米国国防省がアジア地域で展開する柔らかい半導体戦略 2023/06/20 2000円(税込)・1818円(免税)¥1,818

[カラー単行本] Googleオープン半導体とアジアの電子地政学 予告版 2022/11/14 500円 (税込) ・455円 (免税)

¥455

[単行本]RISC-V原典 オープンアーキテクチャのススメ 2018/10/18 3300円 (税込) ・3000円 (免税) ¥3,000

ディジタル回路設計とコンピュータアーキテクチャ [RISC-V版] (00) 大型本 – 2022/6/7

コンピュータアーキテクチャ[第6版]定量的アプローチ 新書 – 2019/9/25 ¥8,800

RISC-VとChiselで学ぶ はじめてのCPU自作 ――オープンソース命令セットによるカスタムCPU実装への第一歩 単行本(ソフトカバー) – 2021/8/25 ¥3,520

作って学ぶコンピュータアーキテクチャ —— LLVMとRISC-Vによる低レイヤプログラミングの基礎 単行本(ソフトカバー) – 2022/7/1 ¥3,960

Chiselを始めたい人に読んで欲しい本 ペーパーバック – 2020/8/28 ¥2,750

Chiselで始めるFPGA電子工作 ペーパーバック – 2022/1/9 ¥2,750