(アブストラクト期限:7月20日)

2024年8月1日木曜日

9:00-18:00 日本標準時 (UTC+9)

| 内容別カラー分類 |

| ① RISC-V ソリューション |

| ② 特別企画:日本の半導体戦略2024とRISC-V |

| ③ RISC-V 昼食交歓会 |

| ④ RISC-V 技術展示 |

| ⑤ RISC-V研究とオープン半導体 |

| ⑥ AI、RISC-V研究ポスター発表 |

| ⑦ プレス名刺交換会(招待制) |

| ⑧ RISC-V日本語出版物 |

RISC-V Day Tokyo カンファレンスは、日本最大の RISC-V イベントです。 RISC-V Day Tokyo 2024 Winter カンファレンスは、2024 年8 月 1 日木曜日 9:00 ~ 18:00 JST (UTC+9) に東京大学伊藤国際学術研究センター(予定)で開催されます。 RISC-V関連の優れた技術や製品、キーマンやエンジニアを集め、製品の認知度向上、企業間連携の実現、技術交流、情報収集などのビジネスチャンスを提供します。 ぜひこの機会に皆様のご参加をお待ちしております! 発表の動画や資料情報を後日ホームページに掲載いたします。

① RISC-V ソリューション ② 特別企画:日本の半導体戦略2024とRISC-V ③ RISC-V 昼食交歓会

2024年8月1日 時間 9:00-18:00

司会:SHコンサルティング 田胡 治之

| 時間 | 発表時間 | 言語 | プレゼンテーション題名 | 発表者 | 所属機関 (詳細はクリック) | 講演資料 |

|---|---|---|---|---|---|

9:00- | 30分 | – | 受付 名札 ペットボトル茶 書籍「日本の半導体戦略2024 1/2」 配布 | 録画機器音響映像セットアップ | |

| 9:30- 9:40 | 10分 | 日英 | 開会の言葉と「日本の半導体戦略2024+1/2」解説 | 河崎 俊平 | 書籍「日本の半導体戦略2024+1/2」著者, SHコンサルティング | – |

| 9:45- 10:15 | 30分 | 英 | AIイノベーションを多くの用途に使えるオープンソースRISC-Vプロセッサにより推進: Tenstorrentは、多用途でオープンソースのRISC-Vプロセッサを使用して、AIイノベーションを推進します。Tensixコアに基づくスケーラブルなAIアクセラレータは、効率的な制御フローとデータ移動のためにRISC-Vを利用しています。専門的なベクトルおよびマトリックスエンジンがAI計算を強化します。高度な機能を備えた高性能なAscalon RISC-Vプロセッサは、異種コンピューティングをサポートし、AIおよびサーバーのタスクに最適です。このオープンでモジュラーなアプローチにより、さまざまなAIアプリケーションにおいて高い適応性、性能、効率を実現し、イノベーションを促進し、多様な計算ニーズに応えます。 | ウエイ・ハン・リエン | テンストレント(カナダ) | ビデオ |

10:20– | 30分 | 英 | 超低消費電力カスタムRISC-VプロセッサによるAI異常検知による予知保全:Codasipの次世代プロセッサアーキテクチャ技術、 新製品100/700RISC-Vプロセッサ・ファミリー、新製品Codasip Studio Fusion、新しいBounded Customコンセプト、エッジIoT、AI、センサーフュージョンのアプリケーションにおける高性能と柔軟性、ならびに脆弱性を半減する安全技術CHERI等ご紹介します。後半には低消費電力なL110 RISC-Vコアをベースにした予知保全のデモンストレーションを行います。AIによる異常検知向けにプロセッサの最適化とカスタマイズを行い、ベースコアと同等以上のパフォーマンスを保ちつつ、クロックを1/4に下げ、超低消費電力を実現した例となります。 | ブレット・クライン | CCO (最高商務責任者), ズデネク・プリクリル | CTO (最高技術責任者) | コダシップ (Codasip)(ドイツ) | ビデオ |

10:50– | 15分 | 英 | 休憩時間:参加者はこの休憩時間にブースを見学できます。 | 出展者はこの時間までにブースを設営します。 | |

11:00-11:30 | 30分 | 英 | RISC-Vを活用して成功を勝ち取る: RISC-Vの開発者に負担をかけない特徴はそれを特別なものにし、この特徴が見えない形で革新を促します。これにより、あなたとあなたのチームが革新を通じて成功を収めることができるかもしれません。AndesはRISC-VコアIPを提供し、System On Chip (SoC)設計にRISC-Vコアを使用する際の制御を助けます。このプレゼンテーションにおいて、Andesは新しいRISC-V CPU IP製品を報告し、ロードマッププランも明らかにします。ロードマップには、アウトオブオーダーRISC-Vプロセッサ、RISC-Vベクタープロセッサ、およびISO-26262自動車グレードのRISC-Vプロセッサが含まれます。AIアクセラレータソリューションが紹介され、Andesカスタムエクステンション電子設計自動化ツールについても解説します。 | フランクウエル・リン | CEO and Chairman, アンデス テクノロジー (台湾) | ビデオ |

11:35-12:00 | 15分 | 英 | ポスターセッション発表者紹介: 中條教授に連れられた発表者が1分ずつ登壇して口頭説明するという方式を予定していますです。ポスターセッションへの参加は、アカデミック、個人、企業を問わず、募集要項の条件に合致し、価値ある応用や研究内容と認められた場合に可能です。参加希望者は、アブストラクトを提出し、承認を受けた後、自費でA0サイズのポスターを持参する必要があります。パネルとデモ用の机は主催者が準備いたします。 | 中條 拓伯 | 教授, 国立大学法人 東京農工大学 知能情報システム工学専攻(日本) | ビデオ |

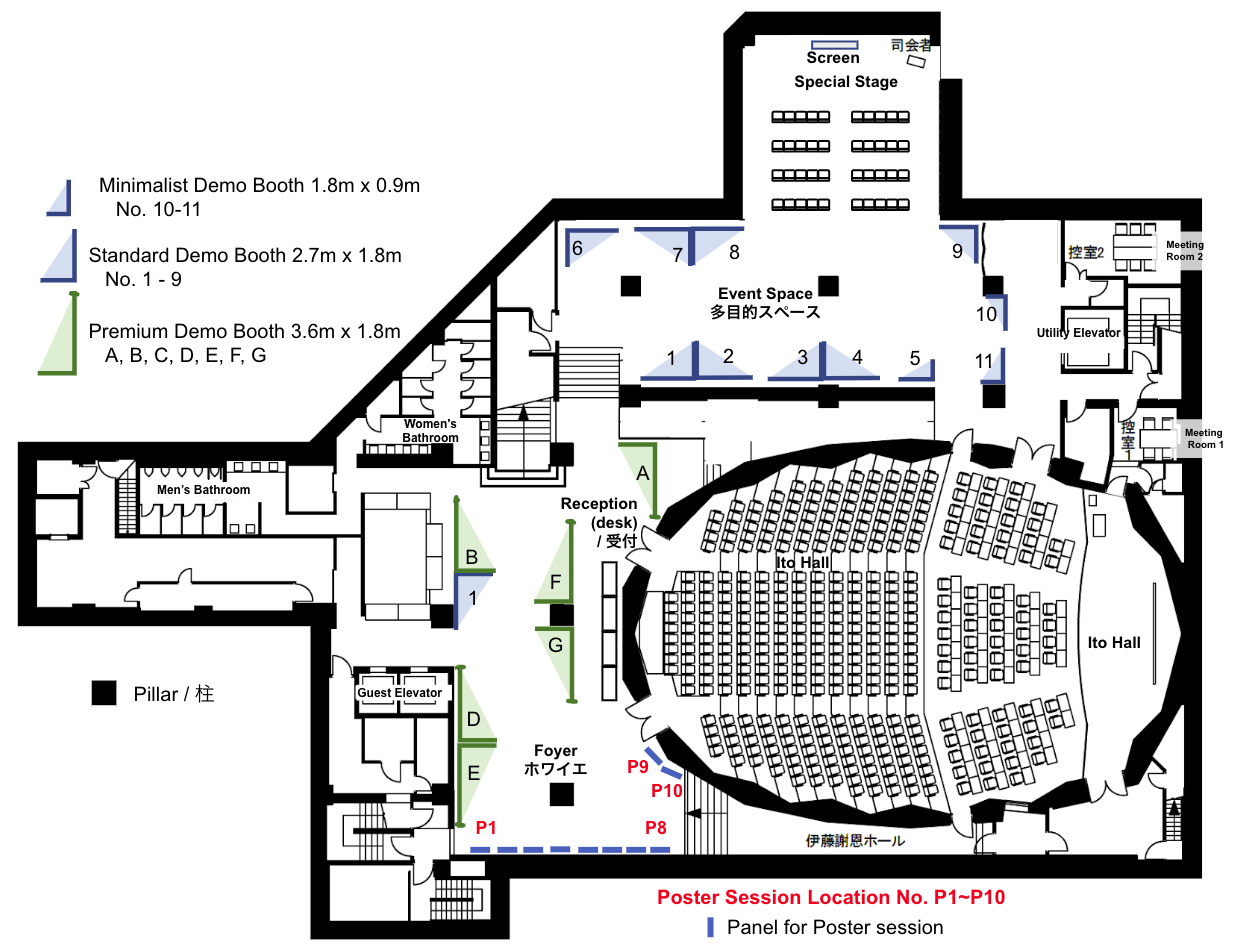

12:00-15:00 | 180分 | 英 | 地下2階 伊藤ホール ホワイエ南にてポスター発表:ポスター発表の場所についてはフロアプランマップを参照し、ポスターパネルの位置P1からP10を探してください。 | ポスター発表者各自によるマンツーマン発表 | – |

| 12:00-14:30 | 150分 | – | はじめ {昼食交歓会}:RISC-Vにおける昼食交歓会は、垂直に分断された半導体の専門分野で交流することを目的とします。ビジネス、応用、技術の側面から、日本の半導体産業がグローバルサプライチェーンの中で強固な位置を築き高い競争力を実現するために、参加者1人1人が日本の半導体産業の復興のイメージ作りをし、互いにシェアすることが必要です。共通の問題意識の中で、個人としての貢献方法を見出すことを目的とします。 | 正午の昼食レセプション開始と同時に、スタッフが、Ventana Microsystemsのご提供により、出席者にシンプルなランチと飲み物をお配りします。スタッフが行き届かない場合は、受付でランチパックをお受け取りください。スタッフは、正午と同時にホールに入りVentanaのシールが貼られたランチパックと飲み物を全出席者に迅速に手渡し配布します。 | – |

| 12:15-12:25 | 10分 | 日 | はじめ {特別企画:日本の半導体戦略2024 1/2} | 河崎 俊平 | 「日本の半導体戦略2024」編者, SHコンサルティング | ビデオ |

12:30-13:00 | 30分 | 日 | 我が国の半導体・デジタル産業戦略について(招待講演):半導体は、DX・GXの観点で極めて重要となるキーテクノロジーであり、経済産業省では2021年に「半導体・デジタル産業戦略」を策定した。2年が経過し、世界情勢は大きく変化し、経済安全保障リスクへの対応や半導体サプライチェーンの強靱化、デジタル化やグリーン化への対応はより現実的な課題となっている。これらの状況を踏まえ、2023年6月に2年ぶりの改定を行った。本講演では、その後のアップデートも含め、具体的な戦略・取り組みのうち、主に半導体関連の概要及び人材育成に関する政策について紹介する。 | 齋藤 尚史 | 経済産業省 商務情報政策局 情報産業課・課長補佐 | ビデオ |

13:05-13:15 | 10分 | 日 | 先端半導体教育:VLSI設計教育センター(VDEC)による未来のエンジニア育成(仮題):VLSI設計および教育センター(VDEC)による未来のエンジニア育成:このプレゼンテーションは、VDECがVLSI設計教育の進展において果たす役割を強調し、先進的なCADツールの活用や実践的なVLSIチップ製造サービスにより、未来のエンジニア育成を支援しています。 | 池田 誠 | 東京大学 VLSI設計教育センター (VDEC) および システム設計研究センター (d.lab) | ビデオ |

13:20-13:30 | 10分 | 日 | LSTC: 技術研究組合最先端半導体技術センターの取り組み:技術研究組合最先端半導体技術戦センター(LSTC)は、最先端半導体技術の研究開発と人材の育成を通じて、わが国半導体産業の持続的、自律的発展を担うプラットフォームとして、2022年12月に設立されました。現在、Rapidus株式会社、3国立研究開発法人、大学共同利用機関法人、9国立大学の14機関が参加する我が国の先端半導体研究および半導体人材育成をけん引する組織となっています。 | 森 雅彦 | 専務理事 | 技術研究組合最先端半導体技術センター (LSTC) | ビデオ |

| 13:35-13:45 | 10分 | 日 | テンストレントの日本産業との協力関係:テンストレントにとって、日本は世界的に重要な地位を占めています。このプレゼンテーションでは、日本の経済や産業との関わりについてテンストレントの取り組みを紹介します。さらに、NEDO(新エネルギー・産業技術総合開発機構)によって資金提供されている、ポスト5G情報通信システムにおける強化インフラの研究開発プロジェクトにおけるテンストレントの役割についても紹介する予定です。 | 石井 康夫(Yasuo Ishii)| チーフアーキテクト、RISC-Vプロダクト、テンストレント(カナダ) | ビデオ |

| 13:50-14:00 | 10分 | 日 | アンデス社のアウトオブオーダープロセッサおよびAI IPによる日本の先端半導体製造ファブの販売促進(題と概要は暫定):アンデスのアウトオブオーダープロセッサおよびAI IPが日本の次世代半導体ファブの販売促進に貢献できる点を解説します。コンピューティング、ネットワーキング、コントローラ用のアウトオブオーダーRISC-VプロセッサAndesCore AX65を紹介し、アウトオブオーダー実行とAI集積の利点、半導体製造ファブにおけるバリュープロポジションの強化について解説します。過去のケーススタディを通じて、IPとファブの提携が、日本の半導体産業におけるイノベーションを覚醒させるメカニズムを説明します。 | フランクウエル・リン | CEO and Chairman, アンデス | ビデオ |

| 14:05- 14:15 | 10分 | 日 | 車載システムにおけるSoCとプロセッサへの期待―組込システムの発展のために―: 車載システムはメカ制御から油圧、電気、電子と様々な手段でより高度な制御を実現し、自動車を通してより安全で快適な移動に貢献してきました。今、その次の手段としてデータドリブンをはじめとするより高度なコンピューティング技術が注目されています。このコンピューティング技術が注目されている背景と、その手段として重要となるSoCおよびその構成要素であるプロセッサに対しての期待を述べます。 | 杉本 英樹 | 株式会社デンソー 半導体基盤技術開発部 担当部長 | ビデオ |

| 14:20-14:30 | 10分 | 日英 | おわり {特別企画:日本の半導体戦略2024 1/2} | 田胡 治之 | 「日本の半導体戦略2024」編者, SHコンサルティング | – |

| 12:00-14:45 | 150分 | – | おわり {昼食交歓会}:昼食は、Ventana Microsystemsのご厚意によりご提供する予定です。昨年の夕食弁当配布の際、大量の弁当が余った経験を踏まえ、今年はフードロス削減を目指します。午後2時までは、皆様にお弁当を1つずつお配りするよう努めますが、午後2時以降は、余力のある方に残ったお弁当を配布する予定です。必要数のみ準備いたしますので、全員に行き渡るようにご協力のほどよろしくお願い申し上げます。 | 午後2時の昼食レセプション終了後、残りの飲み物及び昼食(Ventana Microsystemsのご提供)を配布いたします。追加で必要な方は、レセプションまでお越しください。スタッフは、ランチパックと飲み物の残りを2時からは、希望の出席者に配りフードロスを防止します。 | – |

14:30-14:50 | 20分 | 日 | シンプルなマイクロコントローラから複雑なマルチコアSoCまでのRISC-Vベースチップのデバッグの簡素化:RISC-Vアーキテクチャのデバッグプロセスを改善し、開発効率とシステム信頼性を向上させる方法を紹介します。命令モジュールと拡張ができるRISC-V命令セットを持つコアのデバッグにおけるソリューションと、LauterbachのモジュラーTRACE32システムについて解説します。組み込みシステム開発におけるデバッガの役割、自動車や航空宇宙などの産業での信頼性の重要性を説明します。TRACE32® PowerViewソフトウェアとハードウェアモジュールを導入し、RISC-Vシステムのために統合されたデバッグアプローチを提供します。 | 毛利 裕二 | 代表取締役, 日本ローターバッハ株式会社 | ビデオ |

14:55-15:15 | 20分 | 日 | 異種コンピューティングによりRISC-Vエコシステムを構築しイノベーションを促進: CanaanのK230チップにVeriSiliconのImage Signal Processor(ISP)IP ISP8000、DeWarp Processor IP DW200、2.5D Graphics Processor Unit(GPU)IP GCNanoVを集積する設計に焦点を当て、高精度で低遅延のエッジAIoTソリューションの創造を解説します。大規模モデルおよびマルチモーダル入力エッジ端末、3D構造化光認識モジュール、インタラクティブロボットなどの応用製品に与える利点について説明します。 | 森脇 暢(Nob Moriwaki) | 営業本部長 VP of Sales, Japan | ベリシリコン株式会社(予定) | ビデオ |

| 15:15-15:45 | 30分 | 日 | 汎用RISC-Vフラッシュマイクロコントローラ「R9A02G021」、64ビット汎用マイクロプロセッサ「RZ/Five」、音声制御およびモータ制御用RISC-V 32ビットASSP:ルネサス エレクトロニクスは、RISC-Vベースの3つの革新的な製品を紹介します。多用途なR9A02G021フラッシュマイクロコントローラ、複雑なタスク向けの強力な64ビットマイクロプロセッサRZ/Five、および音声とモータ制御のための32ビットASSPです。これらの製品は、さまざまなアプリケーションの性能と機能を向上させ、ルネサスの技術革新とソリューション提供へのコミットメントを示しています。 | 江藤 公治 | エンベデッドプロセッシングIC開発統括部 | ビデオ |

| 15:50-16:10 | 20分 | 英 | オールインワンRISC-V AIコンピュートエンジン:AIは学術研究からリアルタイムアプリケーションへと進化し、データセンターからモバイルフォン、車、カメラなどの組み込みシステムに広がっています。AIタスクのための専用NPUの開発は、トランスフォーマーモデルの台頭によってパラダイムシフトに直面し、新しい設計とアーキテクチャが求められました。MetaのLlama2のような生成AIの最近の登場は、強力なエッジ処理の必要性を拡大させました。この進化は、柔軟でスケーラブルかつオープンな処理ソリューションを必要としています。Semidynamicsの「オールインワン」RISC-V AIコンピュートエンジンは、Llama2を統合し、RISC-VオープンISAとオープンAIソフトウェアフレームワークの利点を例示し、将来性がありソフトウェアに優しいアプローチを提供します。このプレゼンテーションでは、組み込み環境での先進的なAIモデルについて探ります。 | ヴォルカー・ポリッツ | チーフセールスオフィサー セミダイナミクス(Semidynamics)(スペイン) | ビデオ |

| 16:15-16:35 | 20分 | 英 | ヴェンタナ マイクロシステムズの「Veyron V2」: 高性能データセンター向けRISC-Vアウトオブオーダープロセッサの性能と応用:このプレゼンテーションでは、ヴェンタナ マイクロシステムズの最新のRISC-Vプロセッサ「Veyron V2」の特性と応用例について説明します。Veyron V2はデータセンター向けに設計されており、高スケーラビリティ、進化した割り込みアーキテクチャ、および包括的なセキュリティ機能を備えています。AI、5G、オートモーティブなど多様な用途でのパフォーマンス向上を実現し、実際の導入事例を通じてその効果と実用性を紹介します。 | トラビス レイニアー | ヴェンタナ マクロシステムズ | ビデオ |

| 16:40-16:55 | 20分 | 日英 | ポスターセッションの講評と入賞者発表:ポスターセッションの参加者には表彰があります。当日は優秀な発表に対する入賞者の選定が行われ、ホールに登壇していただきます。後日、表彰状を送付される予定です。 | 中條 拓伯 | 教授, 国立大学法人 東京農工大学 知能情報システム工学専攻(日本) | ビデオ |

| 17:00-17:30 | 30分 | 日 | Rapidus株式会社の提供する設計環境 Raads (Rapidus AI-Assisted Design Solutions)について: Rapidus株式会社の先進的なファウンドリーサービスにおいて2nm技術における設計製造の短TAT化を実現するために、Rapidusが提供するディジタル設計環境であるRaads(Rapidus AI-Assisted Design Solutions)の概要と個別開発項目について解説します。Raadsは包括的な Rapidusにおける2nm設計製造の協業モデルであるRUMS(Rapidus & Unified Manufacturing Service)の構成要素の一つとなります。 | 鶴崎宏亀 | USシニアリサーチマネージャ, ラピダス株式会社 | ビデオ |

| 17:30-18:00 | 20分 | – | スタッフと出席者全員が伊藤ホールの敷地から退出し帰宅します。スタッフはホールから録音機器とWiFiシステムを撤去し、ゴミを収集袋に入れて車に積み込み、施設の家具を元の位置に戻します。参加者とスタッフと全ての荷物を地下2階から撤収します。 |

|

④ RISC-V 技術展示

2024年8月1日 10:30-16:30

地下2階 ホワイエ、多目的スペース

展示者・内容は変更になる可能性がありますことをご了承ください

| ブース番号 | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| A | 10:30-16:30 | アンデス | アンデス | |

| B | 10:30-16:30 | コダシップ | コダシップ | |

| D | 10:30-16:30 | 汎用RISC-Vフラッシュマイクロコントローラ「R9A02G021」、64ビット汎用マイクロプロセッサ「RZ/Five」、音声制御用、モータ制御用 RISC-V 32ビット ASSP | ルネサス エレクトロニクス株式会社 | |

| E | 10:30-16:30 | TBD | TBD | |

F | 10:30-16:30 | テンストレントのインファレンスAIソリューション展示 | テンストレント | |

| G | 10:30-16:30 | RISC-V 汎用CPU Akaria NS Family: 小型低消費電力NS11A、制御マイコン向けNS31A、アプリケーション向けNS72にて、エッジデバイスや組み込みシステムの熱とコストの制約に対応します。NS31Aでは、ISO 26262 ASIL Dの機能安全要件に準拠したAUTOSARプラットフォーム用のRISC-V CPUで、メモリ用のECCおよび高い信頼性と安全性を確保するためのデュアルコアロックステップアーキテクチャを備えています。 | デンソー株式会社 |

| ブース番号 | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| 1 | 10:30-16:30 | TBD | TBD | |

| 2 | 10:30-16:30 | eFabless / OpenMPWチップ / TinyTapeout チップの金属顕微鏡投影, 九工大チップ, OpenMPW8 インチウエハ, インバーターパズル等 | ISHI-KAI | |

| 3 | 10:30-16:30 | TBD | TBD | |

| 4 | 10:30-16:30 | DTSインサイトのRISC-V ICE ソリューション | DTSインサイト | |

5 | 10:30-16:30 | TBD | TBD | |

6 | 10:30-16:30 | ベリシリコンのIPソリューションとサービス | ベリシリコン | |

7 | 10:30-16:30 | RISC-V ノートパソコン(現物)、RISC-V Android、RISC-V ネットワーク接続ストレージ(NAS)、RISC-V NAS用Casa OS、Milk-V開発ボード、RISC-V Fedora等 | FedoraコミュニティおよびPLCT Lab(プログラミング言語とコンパイル技術研究所)、(上海および武漢) | |

8 | 10:30-16:30 | TBD | TBD | |

9 | 10:30-16:30 | JASA チップ デモ | 小林正隆 | 一般社団法人 組込みシステム技術協会 (JASA) 技術本部 ハードウェア委員会 RISC-V WG(株式会社日立産業制御ソリューションズ) | |

10 | 10:30-16:30 | RISC-V プロセッサ IP セキュリティ デモ | 電気通信大学 | |

11 | 10:30-16:30 | TBD | TBD |

⑦ プレス名刺交換会(招待制)

2024年8月1日 12:00-13:00

司会: 株式会社DTSインサイト

プロダクトソリューション事業部

営業部 営業一課

栗屋 淳(Kuriya Atsushi)予定

⑤ RISC-V研究とオープン半導体

2024年8月1日 12:00-

司会: 株式会社DTSインサイト

プロダクトソリューション事業部

営業部 営業一課

栗屋 淳(Kuriya Atsushi)

| 時間 | 発表時間 | 言語 | プレゼンテーション題名 | 発表者 | 所属機関 (with URL) | 講演資料 |

|---|---|---|---|---|---|

| 11:45- 12:00 | 15分 | 日英 | 開場 {プレス名刺交換会} (招待制) | 司会: TBD | – |

| 12:00- 12:05 | 5分 | 日英 | 歓迎の挨拶 {プレス名刺交換会} (招待制) | 司会: TBD | |

| 12:05- 12:25 | 30分 | 日英 | 歓談 {プレス名刺交換会} (招待制) | 司会: TBD | |

| 12:25- 12:30 | 5分 | 日英 | 閉会の言葉 {プレス名刺交換会} (招待制) | 司会: TBD | |

| 12:30- 12:45 | 10分 | 日英 | 開場撤収入替 {プレス名刺交換会} (招待制) | 司会: TBD | |

| 12:45- 12:55 | 10分 | 日 | 司会者の歓迎の言葉 {RISC-V研究とオープン半導体} | 栗屋 淳(Kuriya Atsushi)| 株式会社DTSインサイト プロダクトソリューション事業部 営業部 営業一課 | – |

| 13:00- 13:20 | 20分 | 日 | JASA RISC-V チップ計画:JASA RISC-V チッププロジェクトでは、デュアルRISC-Vを搭載し中容量(1MB)外付けメモリをXIP接続できるIoT管理チップを、2023-24年にeFabless / Skywater 130nmプロセスをターゲットとして開発しています。2026年および2029年には一般社団法人OpenSUSIが企画しているシャトルを活用しRoot of Trust (RoT) や無線通信機能を集積することも視野に入れています。将来的な取り組みとして、JASA版RISC-Vチップ評価基板の作成、RTOS移植、クラウド接続、開発環境整備を予定しています。これに加え、チップ開発に興味を持つ人々が1から同等レベルのものを開発できるよう産学協同でのWebベースの教育コンテンツの開発も進めています。 | 小檜山 智久 | 一般社団法人 組込みシステム技術協会 (JASA) 技術本部 ハードウェア委員会 RISC-V WG主査 (株式会社 日立産機システム) | – |

| 13:25- 13:45 | 20分 | 日 | ISHI-Kai オープンシリコン活動と小規模チップテープアウト機会への招待:ISHI-KAIは、オープンソースのプロセスデザインキット(PDK)および電子設計自動化(EDA)ツールを推進するコミュニティ主導のプロジェクトです。このイニシアチブは、半導体設計の共同作業に焦点を当てており、初心者の設計者を集めて、xschemやklayoutなどのツールを使用してインバータやオペアンプなどの個別のアナログ回路を作成します。これらの個別プロジェクトは、最終的に製造のための単一のレイアウトに集積されます。 | 今村 謙之 | メディアアーティスト, ISHI-Kai | |

| 13:45- 13:55 | 10分 | – | 10 分間の休憩 | Bio Break | – | – |

| 13:55– 14:15 | 10分 | 英 | RISC-V上のLinuxソフトウェアエコシステムについての現状:Fedora on RISC-Vの状況、リポジトリの状態、RISC-V開発ボードでサポートされているソフトウェア(例:Firefox、LibreOffice、Thunderbird、Chromium)について報告します。また、OpenSBI、UEFI、ubootのファームウェアと、RISC-Vソフトウェアエコシステムにおけるカーネルの状況も報告します。Arch-linuxやGentooなど、他のLinuxディストリビューションのRISC-Vでの現状についても言及します。これらの情報は、RISC-V上でのLinuxの普及と対応状況を理解するため重要です。 | 魏 傅(Wei Fu)| RISC-V International RISC-Vアンバサダー、Red Hat Software(北京)有限公司のプラットフォーム実現部門のプリンシパルソフトウェアエンジニア | |

| 14:20- 14:40 | 20分 | 英 | Jiachen計画: RISC-V 振興 2036(甲辰计划):Jiachen Project: RISC-V Prosperity 2036、別名「甲辰计划」は、2036年、次の竜年までにRISC-Vエコシステムを大幅に進展させることを目指した野心的なイニシアチブです。このプロジェクトは、ASE Labs、PLCT Labs、Sophgo、およびRISC-Vコミュニティの他の主要プレーヤーによって主導されています。 | 魏 武(Wei Wu)| RISC-V International RISC-Vアンバサダー、PLCT Labの共同創設者兼プロジェクトディレクター | |

| 14:45- 15:05 | 20分 | 英 | Canaan Kendryte K230D: AIoT 向けの最初の rv64ilp32 製品: Canaan Kendryte K230D は、64 ビット処理の利点と 32 ビット データ型のメモリ効率を両立させた最初の rv64ilp32 製品です。セキュリティが強化されたスマート ドア ロック、リアルタイム監視ホーム セキュリティ カメラ、高性能ドローンなど、さまざまなスマート ハードウェア製品に適しています。 | 任 郭(Ren Guo) | エンジニア、Alibaba(中国)のLinux CPUサブシステム担当 | |

| 15:05- 15:15 | 10分 | – | 20 分間の休憩 | Bio Break | ||

| 15:15- 15:35 | 20分 | 英 | Shell-Role型チップにおけるRISC-Vの技術的利点と応用:Shell-Role型チップは、固定ロジックのShell部と、柔軟性のあるRole部から構成される新しいチップアーキテクチャである。この例としてCRESTプロジェクトにおけるSLMLETと、Agile-Xプロジェクトにおけるテスト用チップを紹介する。SLMLETは、Role部に熊本大の提案するFPGAのIPを有している。一方、Agile-Xプロジェクトでは、ここにゲートアレイを用いて、Minimal Fabの利用により短時間低コストでASIC構成を実現することができる。本報告では両者の特徴を比較し、今後の可能性について紹介する。 | 天野 英晴 | 東京大学大学院工学系研究科 システムデザイン研究センター 特任研究員 | |

| 15:40- 16:00 | 20分 | 英 | スケーラブルなAIハードウェアアクセラレータとセキュアなNetwork-on-Chipフレームワーク: スケーラブルなAIハードウェアアクセラレータとセキュアなNetwork-on-Chipフレームワーク: RISC-VベースのスケーラブルなAIハードウェアアクセラレータとセキュアなNetwork-on-Chip (NoC) フレームワークの開発について解説します。効率的なAI計算を実現しつつ、NoC内の強力なセキュリティ対策を確保するアーキテクチャと設計原則を探ります。RISC-Vの柔軟性を活かしたカスタム拡張、AI最適化のための実装戦略、を取り上げます。電気通信大学(UEC)の設計自動化拠点と評価環境をを共有し、国内外の研究機関や企業との連携による技術的な利点とその将来的な可能性についても考察します。 | Hoang-Trong Thuc | 助教授 電気通信大学, 範 公可(Cong-Kha Pham) | 教授 コンピュータ・ネットワーク工学専攻 電気通信大学 | |

| 16:05- 16:25 | 20分 |

| AIチップ設計拠点の活動: 我が国におけるAIチップなどの半導体チップ開発を支援するために産総研と東大が共同でAIチップ設計拠点を運営している。2019年度から2022年年度にかけてはNEDO事業の一環として拠点の構築が行われ、並行して試験運用も実施された。2023年度からは産総研の共用設備として位置付けられ、自立運用が開始されている。本講演では、AIチップ設計拠点が整備・提供してきたLSI設計基盤やSoCプラットフォーム、さらにAIチップ設計拠点の今後の展開について紹介する。 | 内山邦男 | 招待研究員, 産業技術総合研究所(AIST) | |

| 16:25- 16:45 | 20分 | 日 | TS-Perf:各種CPUのTEE(Trusted Execution Environment)で処理時間を計測する技術:Trusted Execution Environment (TEE) は多くのCPUアーキテクチャで実装されている。IntelではSGX、Arm Cortex-AではTrustZone、RISC-VではKeystoneがある。Arm TrustZoneとRISC-V KeystoneではOS相当のソフトウェアが実行されるが、Intel SGXではライブラリレベルがTEEで実行されるなど、実装アーキテクチャは大きく異なる。このため、TEE内の実行時間の計測やTEE外のOSでの実行した場合との性能比較などが難しい。TS-Perfではその差分を吸収して、TEE内と通常のOSで同じバイナリの実行を比較できるようにした。TS-Perfを使った比較により、TEE内での性能差が明確になった。 | 須崎 有康(Kuniyasu Suzaki)| 教授 情報セキュリティ大学院大学 | |

| 16:45-16:55 | 10分 | 日 | 閉会の挨拶 | ||

| 16:55- 18:00 | 65分 | ー | 撤収 |

⑥ AI、RISC-V研究ポスター発表

2024年8月1日 11:35-15:00

技術展示場所 :Location No. RISC-V ポスター 展示 (ホワイエ)の配置図を参照ください。

| 枠 | 発表時間 | 言語 | 出展テーマ | 発表者 | 所属機関 | ポスター | |

|---|---|---|---|---|---|---|

| P1 | 11:35- 15:00 | 180nm CMOSでのIoT向けASCON暗号を搭載したRISC-V System-on-a-Chip:近年、IoTデバイスの数は急速に増加しており、IoTにおけるエッジコンピューティングは技術産業の新たな成長トレンドと考えられています。暗号技術はIoTデバイスのセキュリティを強化するために広く使用されていますが、リソースの制約や遅延などの制限も伴います。そのため、軽量暗号(LWC)は、セキュリティを維持しながら、リソースの使用量とシステムコストを最小限に抑えるバランスを取ります。ASCONは、実装と暗号解析の対象として有望なLWCアルゴリズムの一つであり、多くのバリエーションで、認証付き暗号化と関連データ(AEAD)およびハッシュ機能を提供し、さまざまな用途に対応します。本稿では、RISC-V System-on-a-Chip(SoC)の周辺機器として、ASCON暗号の実装を紹介します。ASCON暗号コアはFPGA上で1,424 LUTを占有し、180nm CMOS技術で17.4kGEを占有し、1.0Vの電源電圧と2MHzの周波数で417Gbits/Jのエネルギー効率を達成します。 | Khai-Duy Nguyen(電気通信大学、日本) Tuan-Kiet Dang(電気通信大学、日本) Binh Kieu-Do-Nguyen(電気通信大学、日本) Cong-Kha Pham(電気通信大学、日本) Trong-Thuc Hoang(電気通信大学、日本) | |||

| P2 | 11:35- 15:00 | 英 | 2024年におけるRISC-Vベクトル拡張の概要: 命令設計の観点から見ると、RVVは異なるVLENやワークロードにおいて、SIMD、NEC SX、SIMTと比較して優位性があるのでしょうか。RVVにおけるプロセッサ設計は、パイプラインの依存性や長いベクトルの処理によって悪影響を受けることもあります。 | 発表者:ルー・ヤン | 東京大学新領域創成科学研究科(日本、千葉)、チェン・ヤンユー | 重慶大学(中国、重慶)、マン・ヤン | 中国科学院計算技術研究所(中国、北京)、ジョン・インウェイ | 南方科技大学(中国、広東省、深圳) | – | |

| P3 | 11:35- 15:00 | ハイパーバイザ技術を利用したRISC-V拡張の容易な活用のためのシステム開発:RISC-Vにおいては、「拡張」と呼ばれるモジュール化された命令仕様が次々と策定されています。しかし、ハードウェアの実装が期待通りには進まず、多くの拡張が未使用のまま、行き先がわからない状態にあります。 | たかな のりまさ | 筑波大学, | |||

| P4 | 11:35- 15:00 | 英 | Cyclone V FPGA上の三重モジュール冗長RISC-Vプロセッサ: 原子力発電所の廃炉状況のような強い放射線環境下では、ロボットやその他のシステムには放射線耐性のあるプロセッサが必要です。現在、宇宙規格のプロセッサが利用可能ですが、たとえそのような宇宙規格のプロセッサを使用したとしても、福島第一原子力発電所では放射線耐性が十分ではありません。宇宙規格のプロセッサの寿命は約10時間に限られています。そこで、RISC-Vプロセッサにトリプルモジュラ冗長 (TMR) を導入して、全電離線量耐性を向上させました | いそべ まさと | 岡山大学 環境生命自然科学技術大学院, 渡邊 実 | 岡山大学 環境生命自然科学技術学部, 渡邊 誠也 | 岡山大学 環境生命自然科学技術学部 | – | |

| P5 | 11:35- 15:00 | ポスター発表65 | TBD | – | ||

| P6 | 11:35- 15:00 | ポスター発表66 | TBD | – | ||

| P7 | 11:35- 15:00 | 英 | 教育目的のためのLinux対応RISC-V SoCとOpenXC7:RISC-Vのソフトコアは広く利用可能ですが、Linuxを実行できるほとんどのコアは複雑であるため、教育目的には不向きです。そこで、私たちはQuasiSoCを紹介します。これは、MMUモードと非MMUモードの両方でメインラインのLinuxカーネルを実行できる、純粋なVerilogで書かれた32ビットRISC-V CPUおよびSoCです。32ビットの非MMUサポートは初めて実装され、現在ではLinuxカーネルとbuildrootの上流に追加されています。理解しやすいコード、BRAMライクなバスインターフェース、オプションのメモリ管理ユニットにより、教育シナリオに最適な選択肢となります。QuasiSoCは通常、SDRAM、HDMI、およびSDカード機能を有効にした場合でも、AMD/Xilinx Artix 7 xc7a35t FPGAの論理リソースのわずか25%しか使用しません。したがって、予算が限られた教育用の開発ボードの大多数に対応しています。 | 発表者:グ・イーミン(顧宜珉)| 東京大学(東京), ホ・シュー(何旭)| 中国科学技術大学(安徽省、合肥市), チェン・シンヤン(陳興延)| 中国科学技術大学(安徽省、合肥市),ジョン・シーチェン(鄭世成)| 中国科学技術大学(安徽省、合肥市)), ルー・ジエンリャン| (呂建良、中国科学技術大学(安徽省、合肥市) | ||

| P8 | 11:35- 15:00 | スレッド対応RISC-Vベースのマルチコアにおけるハードウェア/ソフトウェア共同設計:RISC-Vは2011年の誕生以来、急速な成長を遂げ、その命令セットを基にした多数の無料およびオープンソースプロセッサが誕生しました。RISC-Vは、IoT、ウェアラブルデバイス、AIなど、さまざまなデバイスでますます使用されるようになり、RISC-Vコアを用いたマルチコアプラットフォームの需要が高まっています。特定のアプリケーション向けに異なるRISC-Vコアを組み合わせることは理想的に思える一方で、ほとんどのオープンコアには効率的なマルチコア設計に必要な機能が欠けているため、困難が伴います。本研究では、これらのボトルネックを克服するためのハードウェア/ソフトウェア共同設計ソリューションを提案し、マルチコアシステムの性能を大幅に向上させることを目指します。 | Nguyen Binh Kieu(電気通信大学、日本)、Khai Duy Nguyen(電気通信大学、日本)、Tuan Kiet Dang(電気通信大学、日本)、Cong-Kha Pham(電気通信大学、日本)、Trong-Thuc Hoang(電気通信大学、日本) | |||

| P9 | 11:35- 15:00 | 英 | RISC-V対応DynamoRIOの実装と移植の進捗状況:DynamoRIOは、プログラム分析、プロファイリング、計測などの用途でその汎用性が評価されている動的コード変換システムです。 | 発表者:楊劉博士 (Dr. Yang Liu,) 精密論理および計算技術研究所 (PLCT Lab = Precision Logic and Computational Technologies Laboratory)、清華大学、北京 | – | |

⑧ RISC-V関連 日本語出版物

購入希望の方は書籍写真をクリック

[単行本] 日本の半導体戦略と電子地政学2024を読む: RISC-V と Googleオープン半導体の動向 2024/1/16 1500円(税込)・1364円(免税)¥1,364(免税)¥3,000

[単行本] Google半導体とRISC-Vと世界の電子地政学ー米国国防省がアジア地域で展開する柔らかい半導体戦略 2023/06/20 2000円(税込)・1818円(免税)¥1,818

[単行本] Google半導体とRISC-Vと世界の電子地政学ー米国国防省がアジア地域で展開する柔らかい半導体戦略 2023/06/20 2000円(税込)・1818円(免税)¥1,818

[カラー単行本] Googleオープン半導体とアジアの電子地政学 予告版 2022/11/14 500円 (税込) ・455円 (免税)

¥455

[単行本]RISC-V原典 オープンアーキテクチャのススメ 2018/10/18 3300円 (税込) ・3000円 (免税) ¥3,000

ディジタル回路設計とコンピュータアーキテクチャ [RISC-V版] (00) 大型本 – 2022/6/7

コンピュータアーキテクチャ[第6版]定量的アプローチ 新書 – 2019/9/25 ¥8,800

RISC-VとChiselで学ぶ はじめてのCPU自作 ――オープンソース命令セットによるカスタムCPU実装への第一歩 単行本(ソフトカバー) – 2021/8/25 ¥3,520

作って学ぶコンピュータアーキテクチャ —— LLVMとRISC-Vによる低レイヤプログラミングの基礎 単行本(ソフトカバー) – 2022/7/1 ¥3,960

Chiselを始めたい人に読んで欲しい本 ペーパーバック – 2020/8/28 ¥2,750

Chiselで始めるFPGA電子工作 ペーパーバック – 2022/1/9 ¥2,750