Thursday, December 4, 2025 9:00-18:00

Thursday, December 4, 2025 9:00-18:00

Japan Standard Time (UTC+9)

CLICK to go to Registration Site

Time | Presentation Title | Speaker |

9:30-17:50 | Moderator | Tomohisa Kohiyama | Chief, RISC-V Working Group, Japan Embedded Systems Technology Associations (JASA) | Chief Engineer, Infrastructure Systems Group, Hitachi Industrial Equipment Systems Co., Ltd. |

Welcome Remark: “Research and Innovation in RISC-V” | Makoto Ikeda | Professor, Department of Electrical Engineering and Information Systems, Graduate School of Engineering, The University of Tokyo | |

10:00-10:20 | Japan’s Semiconductor and Digital Industry Strategy | Hisashi Saito | Ph.D. (Engineering) , Deputy Director / Senior Coordinator | Information Industry Division, Commerce and Information Policy Bureau, Ministry of Economy, Trade and Industry (METI) |

Introduction to High-Performance Connectivity IP by Alphawave Semi | Sue Hung Fung | Product Line Manager, Principal IP Group Product Marketing, Alphawave Semi | |

11:00-11:30 | Chatbots to Robots Physical AI at the edge opens markets to new autonomous platforms and greater operational efficiencies. This presentation explores the essential technologies needed to implement physical AI, examining the four core computing challenges: Sense, Think, Act, and Communicate. By understanding the requirements of each component, we can identify the key technological advances needed to drive the next wave of physical AI innovation at the edge, and enter the autonomous supercycle. | Cheol Kim| Director of Product Marketing, MIPS Technologies |

| Invited Educational Lecture: “Security 101 – A Survey of Root of Trust and RISC-V TEE” This talk provides an overview of Trusted Execution Environments (TEEs) developed based on RISC-V, such as Keystone and CoVE, as well as Root of Trust technologies including Titan and Caliptra. These technologies require not only secure hardware implementations but also trustworthy software, along with external verification through Remote Attestation. The presentation will also compare these emerging RISC-V–based approaches with existing commercial solutions—such as Arm TrustZone, Intel SGX, TDX, AMD SEV-SNP for TEEs, and AMD Secure Processor (AMD-SP) for Root of Trust. | Kuniyasu Suzaki | Institute of Information Security | |

| Caliptra and OpenTitan Tutorial — Architecture and Integration of the Open Root of Trust Firmware Led by Google and Microsoft This tutorial will focus on Caliptra, an open Root of Trust (RoT) project under the Open Compute Project (OCP) led by Google, Microsoft, AMD and Nvidia, and supported by semiconductor companies such as Nuvoton, Samsung and Intel, as well as on OpenTitan, an independent RoT chip initiative led by Google and now being mass-produced by Nuvoton. Caliptra is designed as an SoC-embedded stack that includes firmware, provisioning, and Linux integration, whereas OpenTitan aims to provide a standalone security chip. While OpenTitan represents a transparent, discrete RoT implementation, Caliptra targets the standardization of integrated RoT solutions for cloud and datacenter systems. This session will explore both projects’ design philosophies, secure boot mechanisms, and approaches to improving trust through open-source development. | Andrés Lagar-Cavilla | Distinguished Engineer | Google LLC Mountain View, California, USA | |

12:40-14:00 | Lunch Break | Exhibits Floor Open |

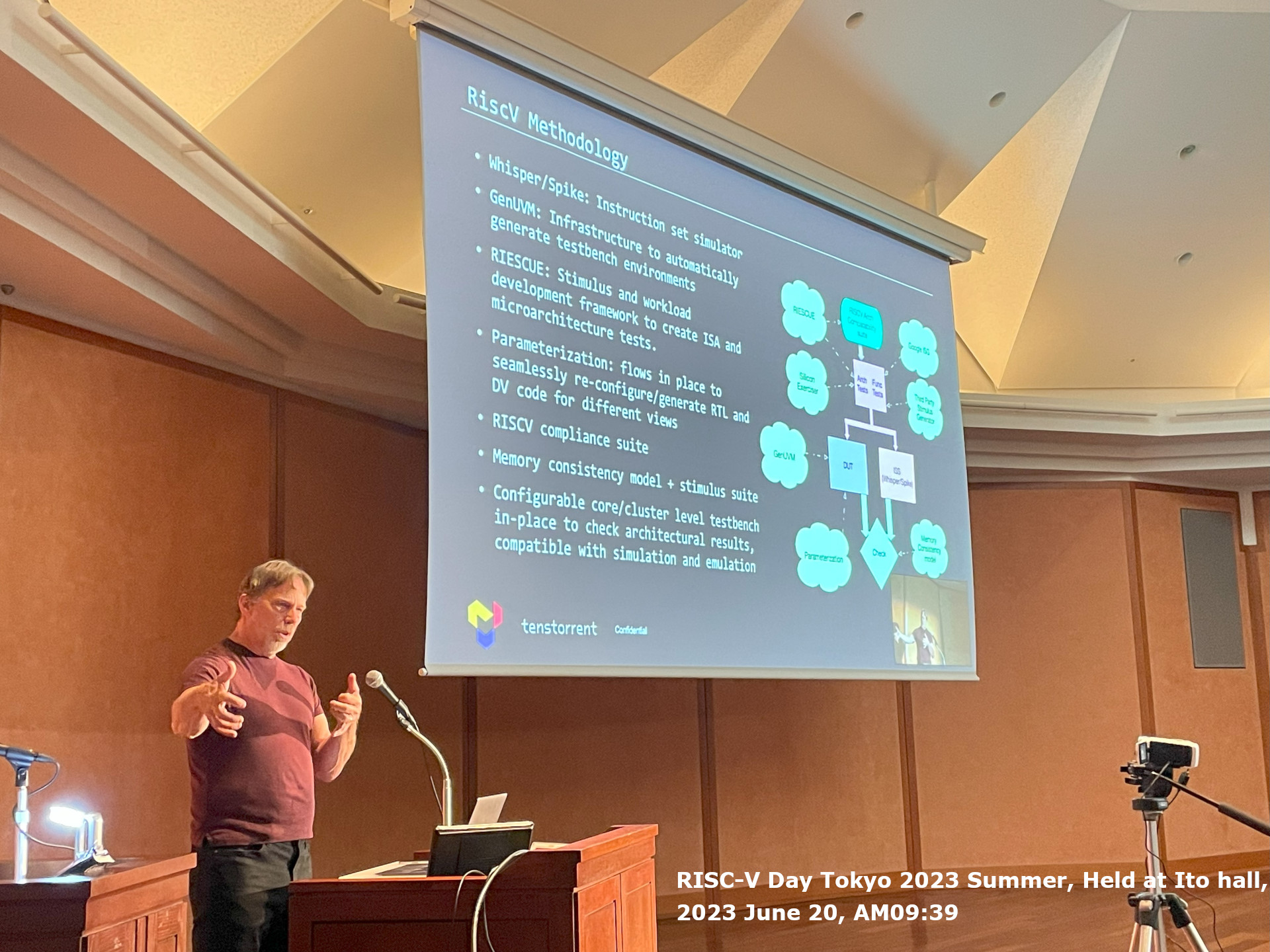

| Scaling Open Compute: RISC-V, Chiplets, and the Future of AI and Robotics This presentation explores how the RISC-V architecture and chiplet technology enable Tenstorrent to develop a wide range of computing platforms across diverse markets, including AI, automotive, and robotics. The presenter also addresses the challenges of building composable systems with chiplets. While the technology to build chiplets, such as UCIe, has matured significantly in recent years, there are still significant gaps in achieving interoperability among chiplets from different vendors. The presenter will highlight key interoperability issues that arise when integrating chiplets from different vendors and share the solutions Tenstorrent is pursuing to overcome these barriers. | Yasuo ISHII | RISC-V CPU Architecture Fellow | Tenstorrent Japan Yasuo is a processor architecture expert who leads next-generation RISC-V CPU microarchitecture design, frontend optimization, and performance exploration. He has nearly 20 years of industry experience and extensive knowledge in high-performance processor design, including CPU frontends, branch prediction, instruction fetch, caches, and data prefetching. Before joining Tenstorrent in 2023, he spent more than eight years at Arm as a Senior Principal Engineer, where he worked on CPU microarchitecture, frontend logic design, and performance analysis. At Arm, he played a key role in developing core technologies for advanced CPUs, including instruction fetch, branch prediction, and scheduling. Prior to his roles at Tenstorrent and Arm, he worked for over eight years as a hardware engineer at NEC in Japan, contributing to CPU logic design across a wide range of frontend technologies, including instruction caches, decode units, scheduling, prefetching, and memory disambiguation. | |

14:40-15:10 | Designing Agentic Loops that Actually Ship — Practical Frameworks for Building Reliable AI Agents in Robotics and Production Systems Agentic AI systems are closed-loop programs that can reason, plan, invoke tools, evaluate results, and iterate autonomously until a goal is achieved. However, making these systems production-ready requires engineering discipline across latency, cost, privacy, and reliability. This talk presents a practical framework for designing and deploying agentic AI loops at scale. The session explores how the ReAct (Reason + Act) paradigm enables robust tool-based agents and multi-agent collaboration, emphasizing tool routing policies, context compression, and on-device retrieval techniques that balance privacy and performance. As cloud-based AI systems encounter limits in responsiveness and data protection, Chirag discusses how RISC-V–based and chiplet-driven platforms are opening new frontiers for local autonomy—enabling intelligent agents to reason, learn, and operate directly on edge and robotic systems. Attendees will gain engineering blueprints and operational guardrails for building sustainable, self-improving AI agents across cloud, edge, and robotics domains, along with insights into how open hardware like RISC-V can power the next generation of scalable, trustworthy AI infrastructure. | Chirag Agrawal | Senior Software Engineer, Amazon.com, Inc., Seattle, Washington, USA Chirag Agrawal is a senior software engineer at Amazon who has contributed to the engineering foundations behind next-generation conversational-AI systems such as Alexa+. He has built mission-critical infrastructure, including the conversational-memory backbone and the RAG-based Bring-Your-Own-Content (BYOC) pipeline — foundational systems that power Amazon’s multi-agent, reasoning-driven architecture. His work spans real-time context compression, prompt optimization, and retrieval-augmented interaction frameworks, all designed to enhance latency, reliability, and scalability across production-grade intelligent agents. Chirag’s current research explores how agentic AI loops can achieve autonomy beyond the cloud, leveraging RISC-V–based and chiplet-driven platforms to bring reasoning and learning directly to edge and robotic systems. This pursuit reflects his broader vision of scalable, privacy-first, and self-improving AI infrastructure that bridges cloud-edge boundaries. He has been featured on InfoQ and leading AI-engineering podcasts for his work on practical frameworks for deploying sustainable agentic AI systems. At RISC-V Day Tokyo 2025 Autumn, he presents “Designing Agentic Loops that Actually Ship — Practical Frameworks for Building Reliable AI Agents in Robotics and Production Systems.” |

| Practical Evaluation and Reproducibility Testing of RISC-V CPU Chips — Developing JASA’s Original Open RISC-V Platform Using FPGA, Google Open MPW, and TinyTapeout, and Publishing It on GitHub The JASA RISC-V Working Group aims to strengthen implementation capabilities by building a reusable RISC-V platform based on the open RISC-V standard. Development has progressed in stages, with working demonstrations achieved at each step. Since 2022, the group has validated a 64-bit Linux boot on FPGA, gaining fundamental expertise in RISC-V system implementation. Beginning in 2024, the group initiated development of a chip roadmap—covering (1) MCUs, (2) Roots of Trust, and (3) networking IP—using open EDA tools, PDKs, and IP such as OpenROAD. Using prototype chips taped out through Google Shuttle MPW-6, 7, and 8, the group performed software evaluation, functional verification, and test procedure standardization, and published all resulting IP and verification logs on GitHub. To improve GitHub reproducibility, the team addressed several practical challenges, including restoration of frozen SiFive Freedom repositories, dependency resolution, Docker-based environment preparation, and toolchain version locking. In fiscal year 2025, following the suspension of eFabless activities, it became necessary to redesign the JASA1 MCU into a simplified logic configuration suitable for fabrication via TinyTapeout. Because TinyTapeout imposes strict limits on available logic area, a conventional 5-stage RISC pipeline could not fit. The CPU was therefore redesigned as a state-machine-based architecture, reducing logic size to one quarter of the original while maintaining RISC-V compatibility and enabling FreeRTOS operation. The design is currently under validation on FPGA and will proceed to tape-out. | Tomohisa Kohiyama | Chief, RISC-V Working Group, Japan Embedded Systems Technology Associations (JASA) | Chief Engineer, Infrastructure Systems Group, Hitachi Industrial Equipment Systems Co., Ltd. | |

| Scaling Open Compute: Initiatives in Japan and Advanced Course of Semiconductor design engineer Development Program In addition to Tenstorrent’s domestic R&D status, we will explain our initiatives in IP, AI chips, and server products; our efforts in automotive SoCs and robotics; and our Advanced Course of Semiconductor design engineer Development Program, which is currently preparing to begin its third recruitment period. | Mamoru Nakano | President, Tenstorrent Japan Since the company’s establishment in January 2023, Mamoru has led its business expansion and organizational development in the Japanese market. Prior to joining Tenstorrent, he served as the Country Manager of Graphcore Japan, overseeing sales, marketing, and customer engagement. Before that, he spent approximately 16 years as the head of Cray Inc.’s Japanese subsidiary, driving the company’s HPC business and regional growth across Asia. He also held the position of General Manager for HPC and Linux business across Asia at HP, and has long been a leading figure in the fields of high-performance computing and cloud infrastructure. | |

16:20-16:40 | Intermission | Exhibit Floor Open |

Open Architecture Lightening Talk ① | Nobushige Nakajima | Semiconductor Design Department 1, Digital Platform Solution Division, Hitachi Industry & Control Solutions, Ltd. (HiICS) | |

Open Architecture Lightening Talk ② | Takaaki Akashi|Country Manager – Codasip Japan | |

17:20-17:30 | Open Architecture Lightening Talk ③ | Noritsuna Imamura|ISHI-Kai, OpenSUSE |

RISC-V Day 2025 Autumn Closing Remarks In this context, Prof. Amano’s team is advancing work on Agile-X, a cluster-based building block utilizing RISC-V, as well as the SLIMLET system. In parallel, the Japanese translation of Computer Architecture: A Quantitative Approach, 7th Edition by Hennessy and Patterson is underway, further supporting the ecosystem’s growth in Japan. The next RISC-V Day event is scheduled for March 5, 2025. | Hideharu Amano | Senior Researcher, Institute of Industrial Science, System Design Research Center (d.lab), The University of Tokyo Advanced Design Division / Fundamental Design Division |

Time | Presentation Title | Speaker |

Hands-on Tutorial and Demo: OpenROAD and Tiny Tapeout Workflow | Noritsuna Imamura, ISHI-Kai, OpenSUSE |

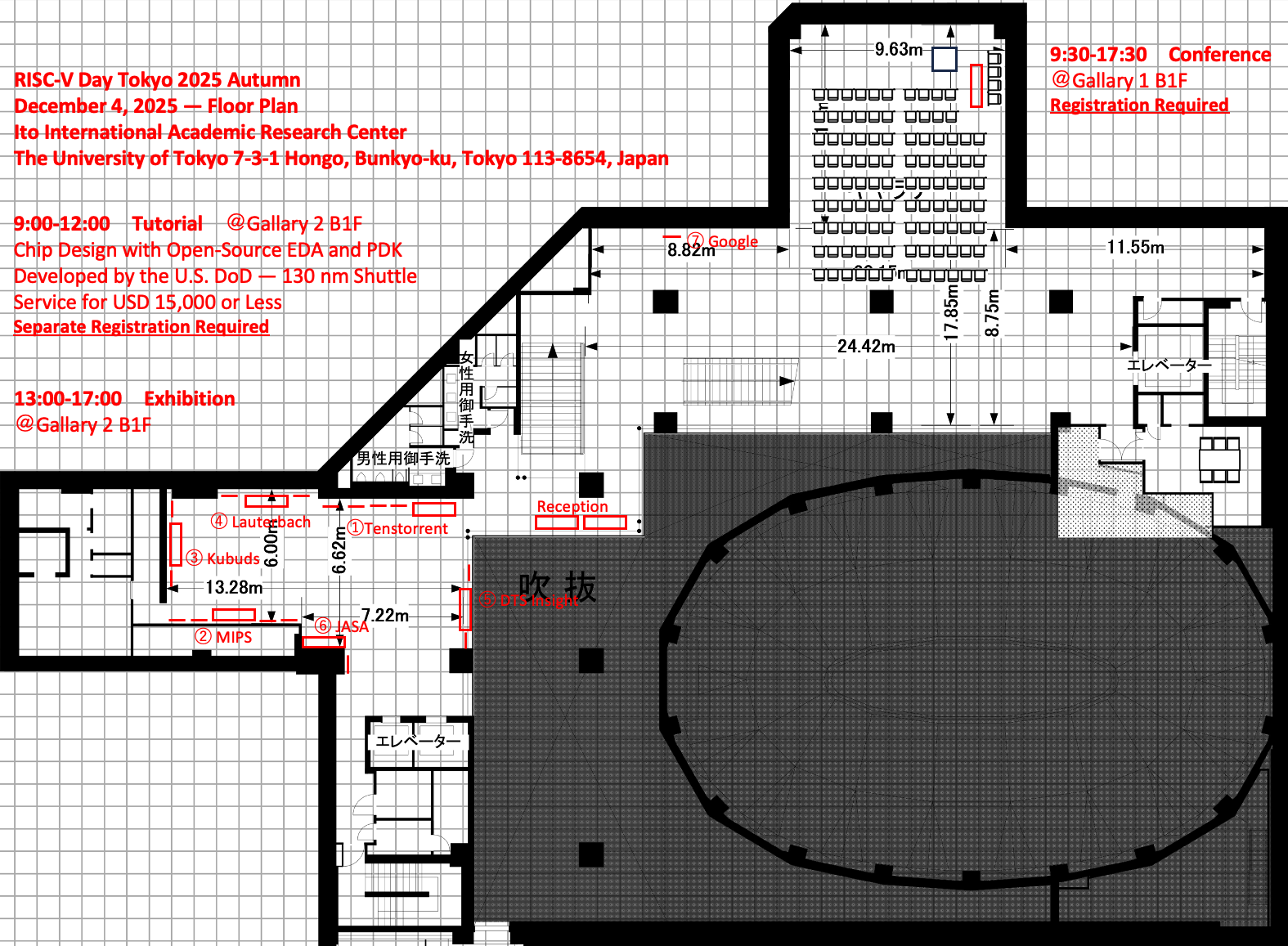

Venue Map