# オープンコンピュートによるスケーリング： 次世代半導体設計への取り組みと 半導体設計エンジニア育成プログラム（上級コース）

中野 守

テンストレントジャパン株式会社 代表取締役社長

Tenstorrent Inc.

APJ Region Manager

# Silicon Engineering Trends

あらゆる技術革新の波には、

半導体技術の革新の波が伴ってきた。

AIの波は、飛躍的に高まる計算能力と

半導体の更なる高度化への需要を牽引している。

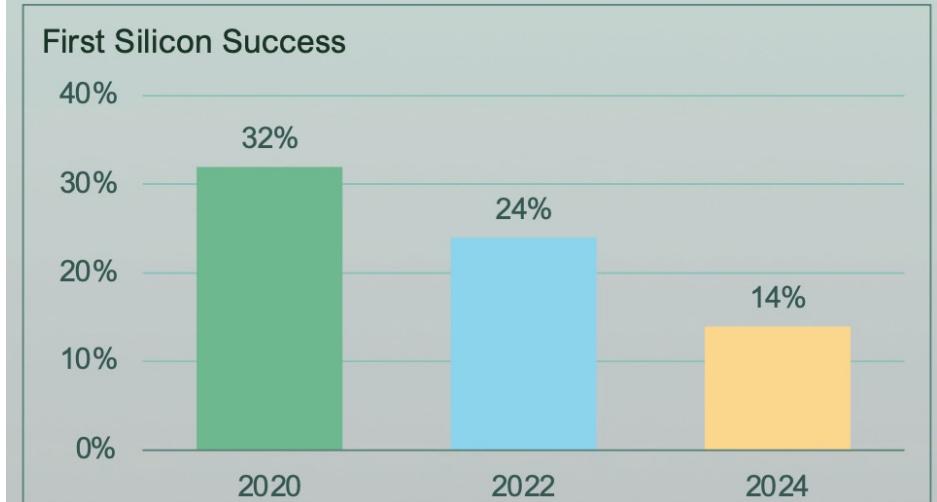

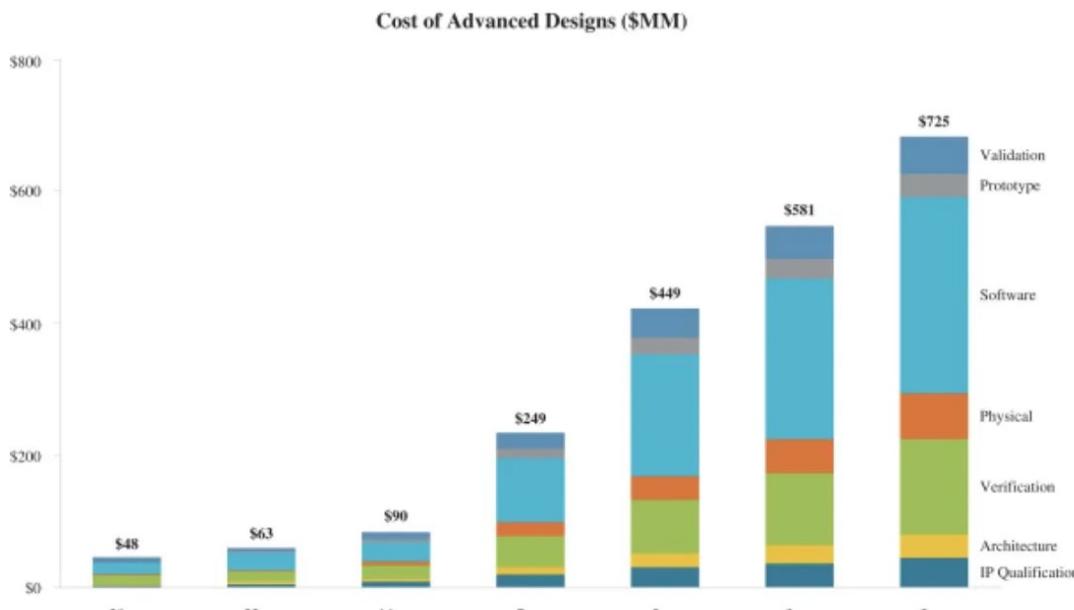

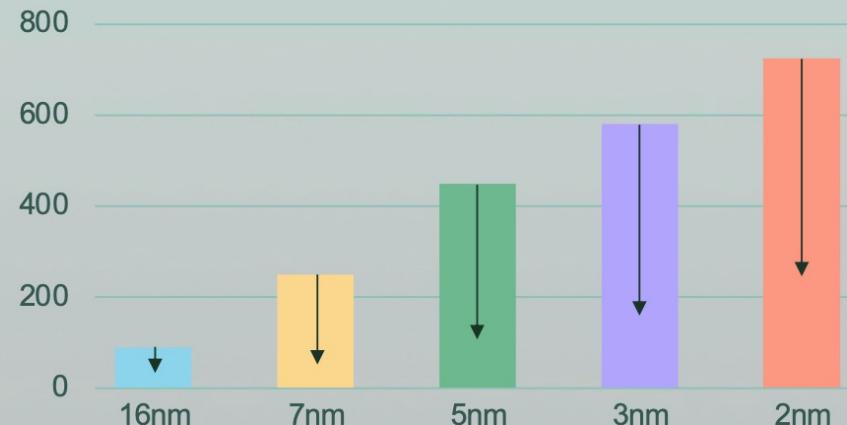

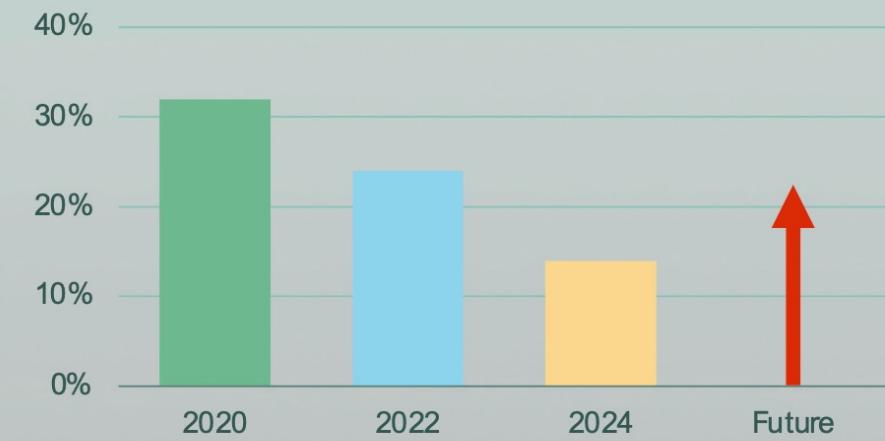

高度化、複雑性の増大は

チップ設計コストの急騰と

初回シリコン成功率の急落を引き起こしている。

# Tenstorrent's Mission

Enabling you to

“own your silicon future”

AI everywhere

最先端半導体開発の

シリコン設計コストを大幅に削減し、

初回シリコン成功率を高める

Cost of Advanced Design (\$MM)

First Silicon Success

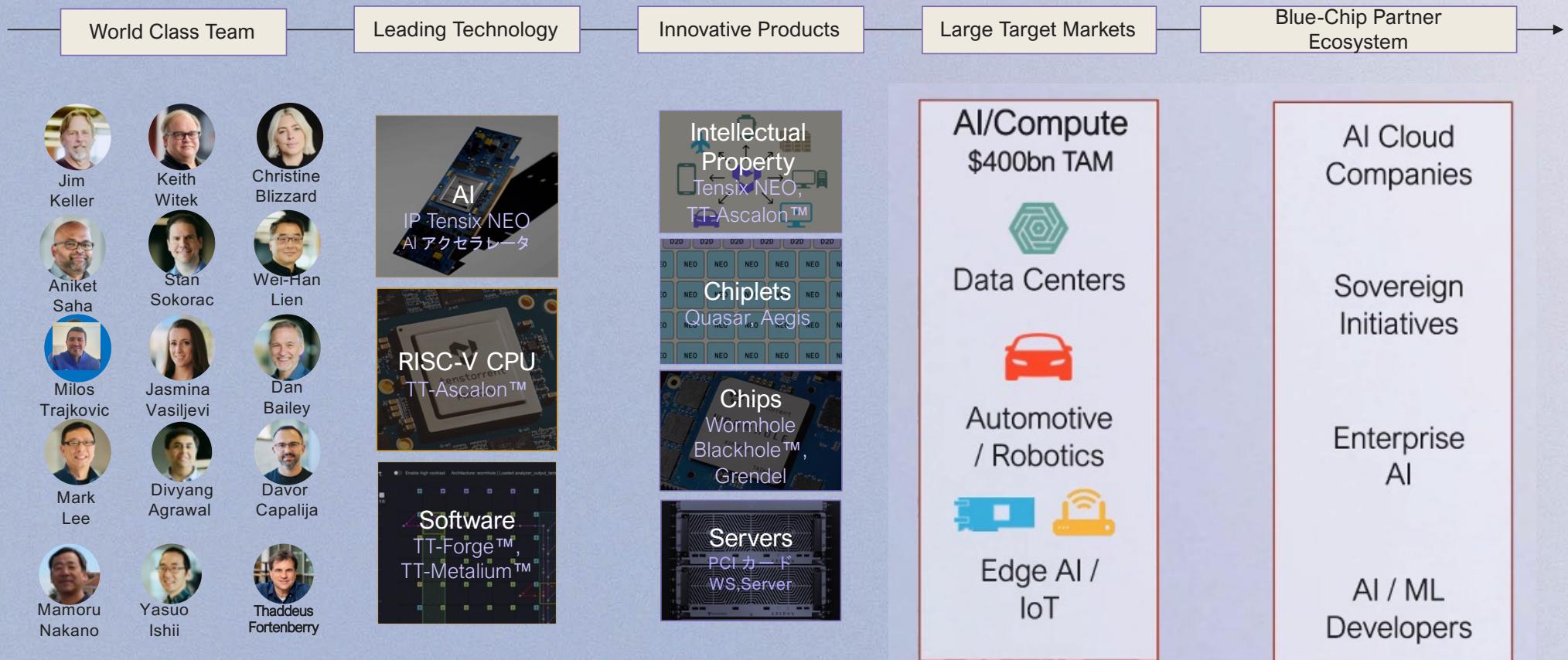

# Software, Silicon, and Systems to Run AI, ML, and Compute *Cheaper and Faster than Anyone Else*

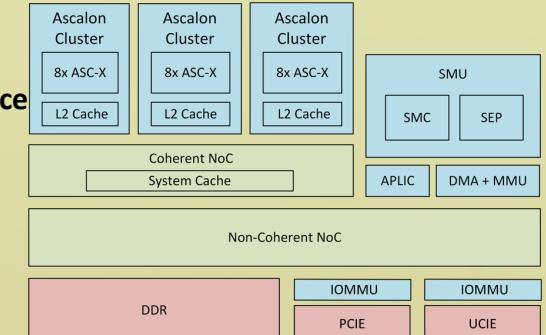

# Tenstorrent IP Portfolio

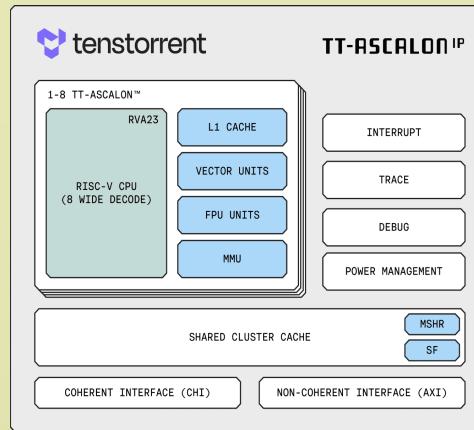

## RiscV CPU IP

### Application Processors

- Ascalon™

- Alexandria™

- Babylon™

- Cyrene™

- Callandor™

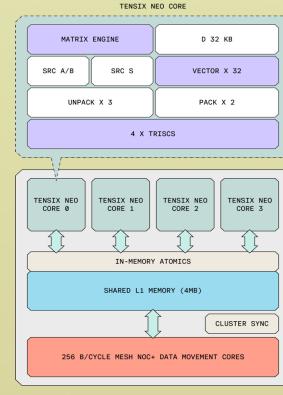

## Tensix AI IP

- Tensix™ Blackhole™

- Tensix Neo™

- Tensix Neo Auto

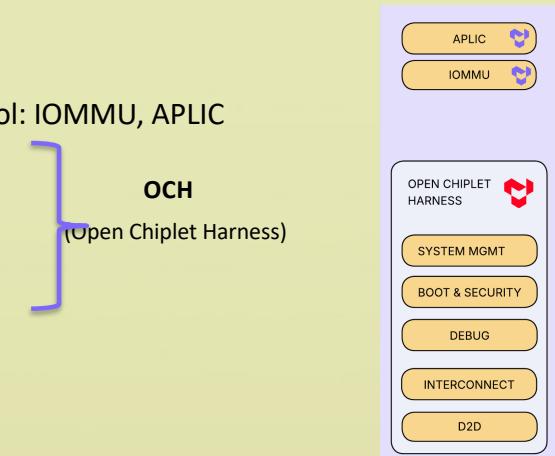

## System IP

- Memory & Interrupt Control: IOMMU, APPLIC

- System Management

- Boot & Security

- Debug & Test

- SoC Internal Fabric

- Chiplet D2D Interconnect

## Subsystem IP

### Compute Subsystem Reference

- Ascalon CPU clusters

- System IPs

- AI compute clusters

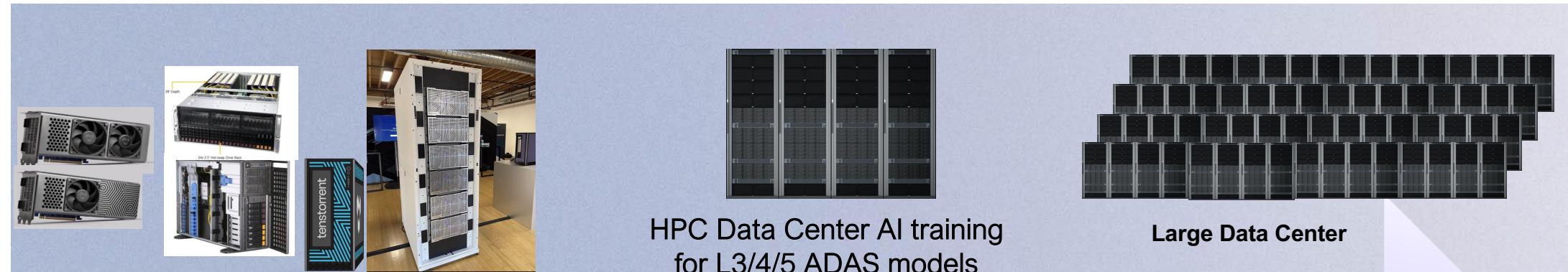

## Single Architecture + OCA + Open SDK

### mobile、Edge Device

### Automotive ADAS,AD/IVI

### Robotics etc

OCA: Open Chiplet Architecture

OCE: Open Chiplet Ecosystem

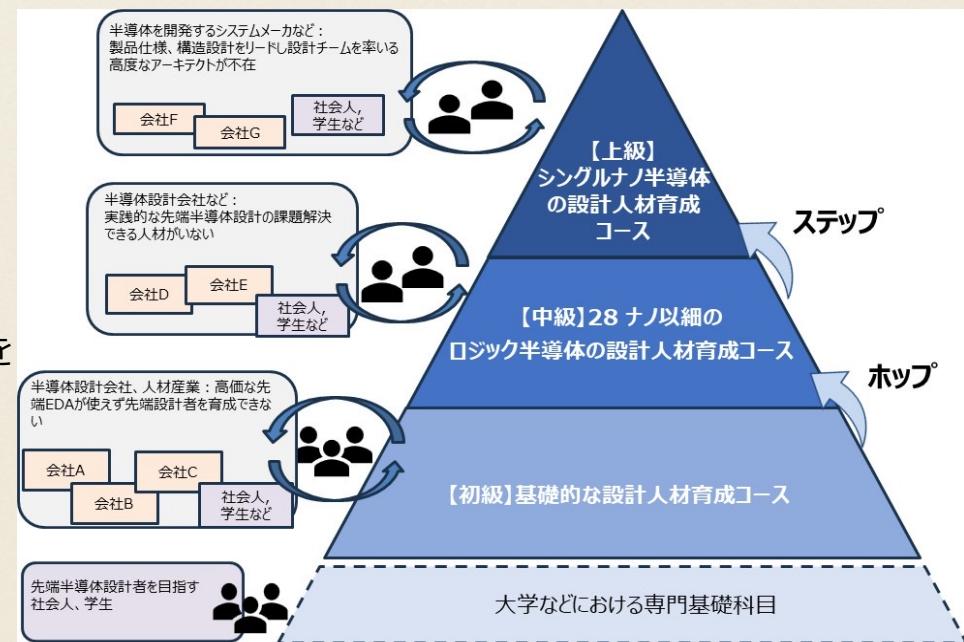

# 最先端デジタルSoC設計人材育成.

2024年11月5日発表 「ポスト5G情報通信システム基盤強化研究開発事業／人材育成」上級コースの委託先に選ばれました。

- 上級コース：シングルナノ半導体設計コース

シリコンバレーの最先端企業で実践的な研修（アドバンスコースOJT）を行う人材育成プログラム

## 上級コースの目標

- 最先端の半導体設計に必要な知識、実践能力を身につける。

- 全体を俯瞰しながら、高度な半導体設計ができる人材を育成する。

- 半導体設計者としての国際感覚および交渉能力を鍛える。

- 日本の多くのテクノロジー企業、研究機関、大学から募集

2025年5月7日から応募開始、7月1日より最初のトレーニングを開始。

年2回募集、現在第3期の応募受付中。

- 5年間のプロジェクト期間中に最大200人年の最先端半導体設計エンジニアを

米国拠点に於て、シングルナノ世代の最先端のCPU 及び

AI/MLアクセラレータ開発技術等を実践OJTを通して学ぶ。

- 技術分野 RISC-Vプロセッサ、AIアクセラレータ、Chipletなど

- 適応分野 データセンター、自動車SoC、エッジ・IoTデバイス

- 拠点 サンタクララ、オースチン、（トロント）、東京

Advanced SoC Design Talent Incubation Program

応募、詳細情報 Webサイト：<https://adip.jp>

# 最先端デジタルSoC設計人材育成 上級コース

IT, AI、半導体ビジネスなど

Vision, Strategy

アーキテクトとして

最先端半導体設計技術

CPU, AI アクセラレータ

Chiplet

SoC(AI,Auto/Robotics)

設計エンジニアとして

国際感覚、コミュニケーション能力、WWな人脈

国際的なビジネスパーソンとして

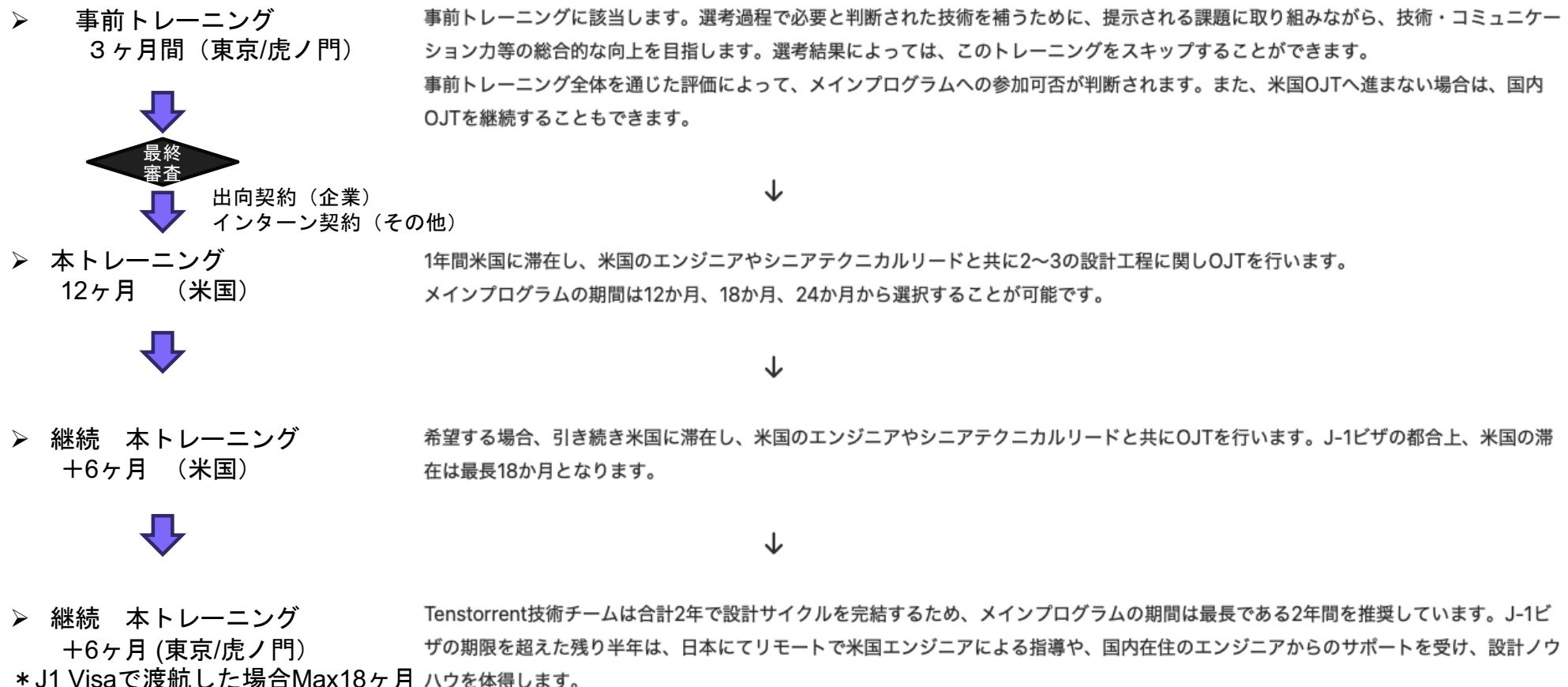

# トレーニングスケジュールと実施場所

## 1) 事前トレーニング (東京、虎の門)

国内 米国と国内エンジニアによるオンライン講義やテキストを使った自習の他、

比較的簡単な課題によるOJT

## 2) 3) 4) 米国Tenstorrent本社 (Santa Clara, Austinなど) におけるOJTトレーニング

米国に滞在し、米国のエンジニアやシニアテクニカルリードのもとでOJTを行います。

合計2年で設計サイクルを完結するため、最長2年の期間を推奨していますが、J1 Visaの期限を超えた残り

半年は、日本にてリモートで米国エンジニアの指導を受け、設計ノウハウを体得します。

| 期間   | 1)   | 2)    | 3)   | 4)   |

|------|------|-------|------|------|

| 工程数* | 3ヶ月間 | 12か月間 | 6か月間 | 6か月間 |

|      | -    | 1~3   |      |      |

|      | -    | 2~6   |      |      |

|      | -    | 全工程   |      |      |

\*以下の設計工程から選択してOJTを行う。

| プロセッサ、アクセラレータ開発                                                                                                                                 | 統合アーキテクチャ開発                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>初期デザイン設計</li><li>評価目標</li><li>論理設計</li><li>性能評価</li><li>論理設計、検討</li><li>物理設計、検討</li><li>評価準備、評価</li></ul> | <ul style="list-style-type: none"><li>統合アーキテクチャ設計、<br/>検討評価</li><li>パッケージボードの設計製造</li><li>チップ製造、評価</li><li>ボード製造評価</li></ul> |

# 上級コース OJTの概要（例）

| No. | 対応プロジェクト                                          | 概要                                                                                                                         |

|-----|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1   | CPU<br>Ascalonのカスタム版<br>開発                        | TenstorrentのRISC-Vコア AscalonD4, D8開発、及びこれらのコアをクラスタ化したAegisやAthenaの開発。インターンチームは、アーキテクチャ、RTL、検証、PDを含む設計などの製品開発をOJTとして学ぶ。     |

| 2   | 車載用AIチップレット<br>開発（RISC-V、AI<br>Acc）<br>ロボティクス用SoC | 車載用AIChiplet開発、Ascalon CPUの機能安全サポート<br>Ascalon IPをベースラインとして、ASIL-B/D準拠のAscalon IPを構築。インターンチームは、これらの製品開発をOJTとして学ぶ。          |

| 3   | AIアクセラレータ<br>TensixNeo, Neo+ 等                    | 次世代Tensix CoreであるNeoの開発及びその派生製品の開発。インターンチームは、アーキテクチャ、RTL、検証、PDを含む設計などの製品開発をOJTとして学ぶ。                                       |

| 4   | AIチップレット                                          | RISC-V & AIアクセラレータ、メモリ、IOなどを要素とした統合アーキテクチャを Chipletで実装する。統合アーキテクチャの設計、検証評価、パッケージボードの設計製造、チップ製造/評価、ボード製造評価などの製品開発をOJTとして学ぶ。 |

OCAに基づく Chiplet (Open Chiplet Architecture)はUCLe, PCIe,CXLなどの標準も取り込み以下の 5 レイヤの標準化を定義する

(Physical,Transport,Protocol, System,Software)

Tensix Core

データフロー型 + メニーコアSRAM はAI専用アクセラレータとして一般的な構造。

各コアにIO制御、命令制御を担う

CPUが 5 基配置されている。

このSDKはオープンソースで公開

されている。

# LSTC 設計人材育成プログラム 上級コース

## 第3期

募集：2025年12月1日～2026年1月30日

選考：2026年 2月2日～2026年2月27日

## 第4期

募集：2026年 6月1日～2026年7月31日

選考：2026年 8月3日～2026年8月28日

### 第3期、5期、7期

|          | Dec | Jan | Feb | Mar | Apr | May | Jun | Jul | Aug |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 募集期間     |     |     | →   |     |     |     |     |     |     |

| 選考期間     |     |     |     | →   |     |     |     |     |     |

| 事前トレーニング |     |     |     |     | →   |     |     |     |     |

| OJT (米国) |     |     |     |     |     |     | →   |     |     |

### 4期、6期、8期

|          | Jun | Jul | Aug | Sep | Oct | Nov | Dec | Jan | Feb |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 募集期間     |     | →   |     |     |     |     |     |     |     |

| 選考期間     |     |     | →   |     |     |     |     |     |     |

| 事前トレーニング |     |     |     | →   |     |     |     |     |     |

| OJT (米国) |     |     |     |     |     |     | →   |     |     |

# トレーニング期間

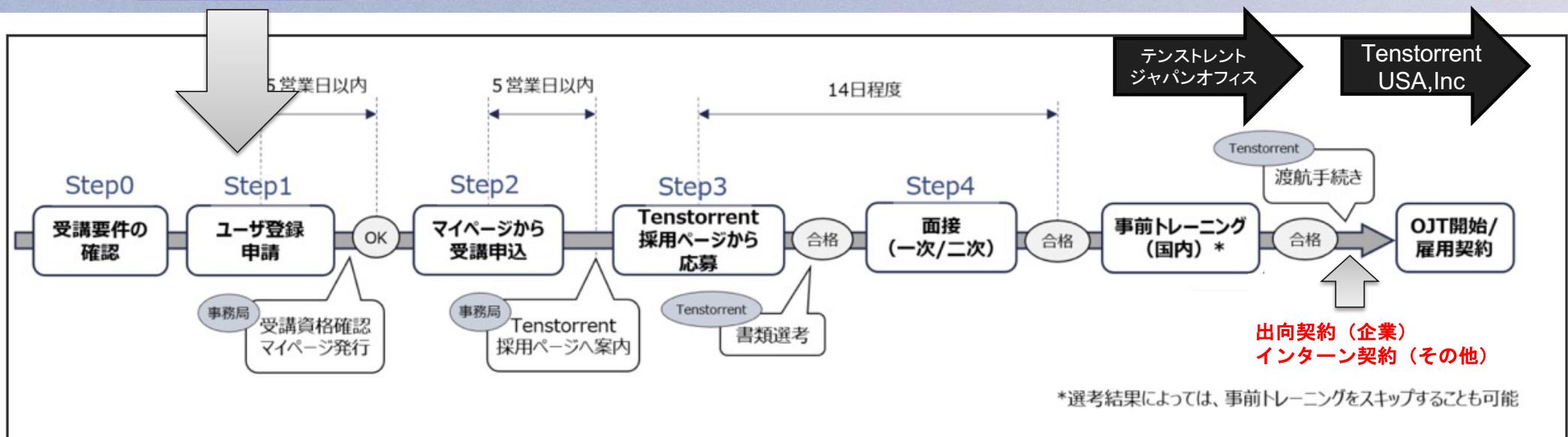

# 参加手続きの流れ

ADIP Webサイト

応募登録、詳細情報

<https://adip.jp>

## 必須要件

- J-1ビザが取得できること（渡米時にTenstorrentで支援）

- EE/CSまたは関連分野の学位に相当する学歴を有すること

- Linux、Tcl/Tk、Perl、Python等のプログラミングに精通していること

- 日本語、英語での高度なコミュニケーション能力を有すること

## あると望ましい要件

- 中・上級エンジニアまたは修士号・博士号取得者であること

- AIアクセラレータ、ASIC設計、FPGAなどの関連分野での実務経験

- SystemVerilog等のHDL経験者

- 大規模チップ開発プロジェクトにおけるリーダー経験があること

- EDAツールの高度な使用経験を持つこと

- 技術説明、プレゼンテーション能力を有すること

# Tenstorrent Santa Clara Office

# Tenstorrent Tokyo Office

ご視聴有難う御座いました!

参加をお待ちしています。

日本の多くのテクノロジー企業、研究機関、大学から受講生を募り、米国のハイテク地域において、米国を中心とする優れた半導体企業から集まった優れたアーキテクト、設計エンジニアが集まるTenstorrentのメンバーとなり1年もしくは2年間のOJTを通して実践的な経験とヒューマンリレーションを持った国際的なエンジニアとなって帰国します。

半導体人材育成プログラム

お問い合わせ・お申し込みは

**ADIP運営事務局**

Webサイト : <https://adip.jp>

お問い合わせメール : [info@adip.jp](mailto:info@adip.jp)