# RISC-Vを取り巻く研究とイノベーション

東京大学大学院工学系研究科

システムデザイン研究センター & 電気系工学専攻 &

電子情報工学科

池田 誠

# これまでの歩み

- 2019.09.30

- 2021.04.21

- 2021.11.19

- 2022.05.31

- 2022.11.16

- 2024.01.16

project for chip democratization~

- 2025.02.27

**VDECとAI拠点とRISC-V**

**チップの民主化とVDEC, d.labおよびAI拠点**

**VDEC / d.lab & AI拠点～チップの民主化とRISC-V**

**ようこそRISC-V Days Tokyo 2022 Spring**

**チップ設計の民主化と我々の取り組み**

**Introduction to Agile-X Project～2-week chip TAT**

**先端デジタルSoC設計プラットフォーム～設計人材育成・教育～**

# 国内の研究会におけるRISC-Vの位置づけ

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               |                                                                               |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|

| 1月1日(月) 午後 開会の挨拶 & オープニング (会場A: 201+202)<br>13:00 - 13:15                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                               | 1月1日(月) 午後 【VLD1】 (会場A: 201+202)<br>(15分)                                     |  |

| 1月1日(月) 午後 【VLD1】 (会場A: 201+202)<br>座長: 小田川 真之 (日本ケイデンデザインシステム)<br>13:15 - 14:35                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                               |                                                                               |  |

| (1) VLD<br>13:15-13:35 オープンソースEDAを用いたチップ作成と機能評価<br>[RECONF] 13:35-13:55 FPGA上の近似算算のLUT最適化によるエラー削減<br>13:35-14:15 長大長周期の自走分割データの最適化<br>14:15-14:35 Scalable FPGA Data-Sorting Accelerator Design for Parallel Single-Source Shortest Path Problem using High-Level Synthesis<br>[RECONF] 13:35-14:45 RISC-Vプロセッサにおける命令レベル擬似乱数子供 | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   |                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月1日(月) 午後 【DC1】会場B: 203<br>座長: 龍波 一輝 (千葉大学)<br>13:15 - 14:35                 |  |

| (5) DC<br>13:15-13:35 開発段階の必要十分条件を用いた複数目標最適化テスト<br>生産の最適化について<br>[RECONF] 13:35-14:15 における並列分割テスト<br>13:35-14:45 グリーピンスキー診断: 誤用化リスクアセスメント<br>RISC-Vプロセッサにおける命令レベル擬似乱数子供                                                                                                                                                        | 澤井大生・鶴川利典 (日本大)・竹内正哲 (京都産大)・新谷洋二 (日本大)<br>工・子洋・山本慎介・工・森川・甲斐・慎・植上重喜・高畠・森川 (愛媛大)<br>松本 俊 (高知工科大学)・上田 隆祐 (高知工科大学)・密山 伸幸 (高知工科大学)<br>上田 隆祐 (高知工科大学)・甲斐 伸弘 (高知工科大学)・密山 伸幸 (高知工科大学)<br>上村 伸弘 (高知工科大学)・上田 隆祐 (高知工科大学)・密山 伸幸 (高知工科大学)<br>上村 伸弘 (高知工科大学)・甲斐 伸弘 (高知工科大学)・密山 伸幸 (高知工科大学) | 1月1日(月) 午後 【DC1】会場B: 203<br>座長: 龍波 一輝 (千葉大学)<br>13:15 - 14:35                 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月1日(月) 午後 【VLD2】 (会場A: 201+202)<br>座長: 濱野 勝彦 (熊本大学)<br>14:50 - 15:40         |  |

| (9) VLD<br>14:50-15:40 [基調講演] 半世紀に一度の3つの追い風の中、最後<br>の10年<br>[RECONF] 15:40-15:55 休憩 (15分)                                                                                                                                                                                                                                      | 若林秀樹 (熊本大)<br>[RECONF] 15:40-15:55 休憩 (15分)                                                                                                                                                                                                                                   | 1月1日(月) 午後 【VLD2】 (会場A: 201+202)<br>座長: 濱野 勝彦 (熊本大学)<br>14:50 - 15:40         |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月1日(月) 午後 【VLD2】 (会場A: 201+202)<br>座長: 濱野 勝彦 (熊本大学)<br>14:50 - 15:40         |  |

| (12) VLD<br>14:50-15:40 [基調講演] SLDM (会場A: 201+202)<br>座長: 多和田 雅典 (早稲田大学)<br>15:40 - 15:55                                                                                                                                                                                                                                      | 若林秀樹 (熊本大)<br>[RECONF] 15:40-15:55 休憩 (15分)                                                                                                                                                                                                                                   | 1月1日(月) 午後 【VLD2】 (会場A: 201+202)<br>座長: 濱野 勝彦 (熊本大学)<br>14:50 - 15:40         |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月1日(月) 午後 【VLD2】 (会場A: 201+202)<br>座長: 平山 聰司 (岩手大学)<br>15:40 - 15:55         |  |

| (13) VLD<br>10:25-10:45 [基調講演] 半導体の構造と機能の分離とそれを去るGUBO簡略化<br>[RECONF] 10:45-11:05 バス通信方式のチップ設計<br>11:05-11:25 Rocket Chipの方式によるシステム開発と実験<br>[RECONF] 11:25-11:45 休憩 (15分)                                                                                                                                                       | 高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)                                                                                                                                      | 1月2日(火) 午前 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (16) VLD<br>10:25-10:45 [基調講演] 半導体の構造と機能の分離とそれを去るGUBO簡略化<br>[RECONF] 10:45-11:05 バス通信方式のチップ設計<br>11:05-11:25 Rocket Chipの方式によるシステム開発と実験<br>[RECONF] 11:25-11:45 休憩 (15分)                                                                                                                                                       | 高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)                                                                                                                                                                  | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (17) VLD<br>10:45-11:05 40nm ToReRAM/Med-disturbによる読み出し速度<br>[RECONF] 11:05-11:25 ReRAMによる電荷移動型半導体の動作評価<br>11:25-11:45 反復エラー注入によるRPA実験<br>[RECONF] 11:45-11:55 休憩 (15分)                                                                                                                                                        | 佐藤大輔・三澤義人・松井伸一・竹内 健 (東大)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)                                                                                                                                                                  | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (18) VLD<br>11:05-11:25 ReRAMによる電荷移動型半導体の動作評価<br>[RECONF] 11:25-11:45 休憩 (15分)                                                                                                                                                                                                                                                 | 高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)                                                                                                                                                                                                                          | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (19) VLD<br>11:25-11:45 Fine-tuning手法によるVTPに向けた<br>[RECONF] 11:45-11:55 休憩 (15分)                                                                                                                                                                                                                                               | 三澤義人・森川・平井 健 (東大)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)<br>高橋一成・喜久井一郎・伊藤洋輔 (東京農工大学)                                                                                                                                                                                                     | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (20) VLD<br>13:00-13:30 開会の挨拶 & オープニング (会場A: 201+202) (15分)                                                                                                                                                                                                                                                                    | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (21) VLD<br>13:30-13:45 [基調講演] RISC-Vプロセッサにおける命令レベル擬似乱数子供                                                                                                                                                                                                                                                                      | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (22) VLD<br>13:30-13:45 休憩 (15分)                                                                                                                                                                                                                                                                                               | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (23) VLD<br>13:45-14:45 [基調講演] RISC-Vのレイアウト最適化                                                                                                                                                                                                                                                                                 | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (24) VLD<br>14:45-15:00 休憩 (15分)                                                                                                                                                                                                                                                                                               | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (25) VLD<br>15:00-15:20 Flash FPGA用にY-RISC-Vアーキテクチャとソートアロケーションの実験                                                                                                                                                                                                                                                              | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (26) VLD<br>15:20-15:35 小型積算を目的としたDTM PUFのレイアウト最適化                                                                                                                                                                                                                                                                             | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】ICD (会場A: 201+202)<br>座長: 田中 明寿 (産業技術総合研究所)<br>13:00 - 13:30 |  |

| (27) VLD<br>15:35-16:35 [基調講演] RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                                         | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (28) VLD<br>16:35-16:55 [基調講演] 重複セシングによるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                                  | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (29) VLD<br>16:55-17:15 [基調講演] ベル平准化とアーキテクチャ実験と評価                                                                                                                                                                                                                                                                              | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (30) VLD<br>17:15-18:15 [基調講演] ワードセグメントによるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                                | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (31) VLD<br>18:15-18:30 [基調講演] 生産用ECC回路の実験と評価                                                                                                                                                                                                                                                                                  | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (32) VLD<br>18:30-18:45 [基調講演] 生産用ECC回路の実験と評価                                                                                                                                                                                                                                                                                  | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (33) VLD<br>18:45-19:00 [基調講演] ワードセグメントによるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                                | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (34) VLD<br>19:00-19:15 [基調講演] ワードセグメントによるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                                | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (35) VLD<br>19:15-20:00 [基調講演] リバーフラッシュ回路によるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                              | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (36) VLD<br>20:00-20:15 [基調講演] リバーフラッシュ回路によるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                              | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (37) VLD<br>20:15-20:30 [基調講演] リバーフラッシュ回路によるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                              | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (38) VLD<br>20:30-20:45 [基調講演] リバーフラッシュ回路によるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                              | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (39) VLD<br>20:45-21:00 [基調講演] FMAのためのラック学習を用いたQUBO構築手法<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                                      | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

| (40) VLD<br>21:00-21:15 [基調講演] インジケーションによるループ平准化と電力無効化波送信システム<br>座長: 佐藤義和 (熊本大)                                                                                                                                                                                                                                                | 片下敏宏・小笠原恵輔・福井一裕・福澤洋一郎・佐藤義和 (東芝)<br>木村晋平・早川義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>鈴木良典・西村和也・伊藤義人 (東芝)<br>Meng Happon・Kazutoshi Wakabayashi・Makoto Ikeda (U Tokyo)                                                                                                                   | 1月2日(火) 午後 【招待講演】RECONF (会場A: 201+202)<br>座長: 佐藤義和 (熊本大)<br>13:35 - 14:45     |  |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                               |                                                                               |  |

# こんなのどうやって創るの？

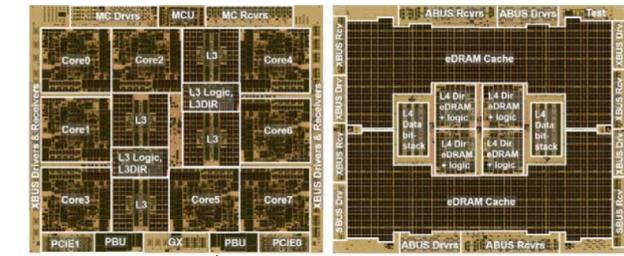

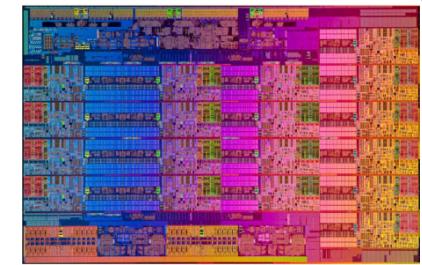

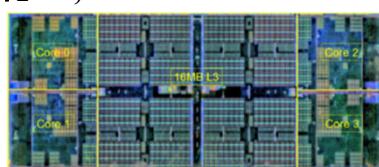

IBM z: 2015年: 22nm

5.2GHz, 40億Tr/71億Tr, 8core

Intel E5-2600v3: 2015年:

22nm, 3.8GHz, 56億Tr,

AMD Zen 4: 2024年

: 5nm, 90億Tr, + IO

Tier 6nm 110億Tr

IBM TrueNorth: 2016年:

1Mニューロン, 256Mシナプ

ス28nm, 54億Tr, 4.3cm<sup>2</sup>

東京大学

THE UNIVERSITY OF TOKYO

AMD Zen 2: 2020年: 7nm,

4.7GHz, 39億Tr, 4 core x 16

tier → 64 core

+ IO Tier

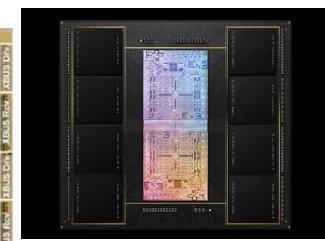

Apple M1 Ultra: 2022年:

5nm, ??GHz, 1,140億Tr,

CPU 20core+GPU64core

|                   |                             |  |                                                                |                                                                                               |

|-------------------|-----------------------------|--|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Cerebras Systems  | WSE-3(Wafer Scale Engine 3) |  | TSMC 5nm, トランジスタ数: 400B, コア数: 90万, AIコアメモリ: 44GB (オンチップSRAM)   | 「世界最大」のチップウェハー1枚を丸ごと1つのチップとして使用。チップ間通信のボトルネックを解消し、超大規模モデルの学習において圧倒的な速度を誇る。                    |

| Groq              | GroqChip (LPU)              |  | 14nm (次世代は4nm), メモリ: 230MB SRAM                                | 「超低遅延」の推論高価なHBM（広帯域メモリ）を使わず、SRAMのみで構成。LLMの**推論（生成）**において、人間が知覚できないレベルの爆速応答を実現。                |

| SambaNova Systems | SN40L                       |  | 再構成可能データフロー (RDU),<br>メモリ: 3階層 (SRAM + 64GB HBM + 最大1.5TB DDR) | 「混合メモリ構成」SRAM, HBM, DDRの大容量メモリを統合し、巨大なモデル（1兆パラメータ級）の推論・学習を効率的に処理可能。                           |

| Tenstorrent       | Wormhole(次世代: Blackhole)    |  | 12nm, RISC-V + Tensix                                          | 「ジム・ケラー率いるRISC-V」伝説的設計者ジム・ケラーが指揮。安価で拡張性が高く、電力効率に優れたチップ。推論・学習の両対応。                             |

| Etched            | Sohu                        |  | TSMC 4nm, Transformerモデル専用, メモリ: 144GB                         | 「Transformer専用」汎用性を捨て、現在主流のTransformerモデル（ChatGPT等の中身）だけを動かすことに特化することで、NVIDIA GPU比で桁違いの効率を実現。 |

# なぜこのようなチップ・チップベンチャーが出てこない？

- **投資（半導体を理解した投資）の欠如**

- ~100億程度のリスクマネーが必要、それを軽減するためには、ウエハシャトルの無料枠などの施策が不可欠

- **モチベーション（山つ気）の欠如**

- ほんのお隣のAI分野では山ほど起業があるので、これは理由ではないかも？

- **アイデアの欠如**

- 同上？

- **環境の欠如**

- VDEC・AIDC等の活動はあれどそれだけでは不足？

- **設計者/アーキテクトの欠如**

- ということで人材育成・教育

Advanced SoC Design Talent Incubation Program

デジタルSoC設計人材の育成をめざして

2024年11月～(講座開始は2025年5月)

# 初級・中級・上級 3つのコース

## 最先端の環境でキャリアとスキル

開発全体の構想・統括を担う人材がいない

⇒ 開発プロジェクトを牽引し、高度設計

のできるアーキテクトに

### 上級コース

Tenstorrent(米国サンタクララ・オースティン)によるOJTプログラム:

一流のエンジニアや関係者と、仕様定義、開発項目の決定、エンジニアチームの編成、プロジェクト全体のとりまとめなどを集中的に学ぶ

半導体製品開発の全体構想を纏められるアーキテクトとしての即戦力、国際的なコミュニケーション能力、ビジネスセンス

実践的な先端半導体設計の課題を解決

できる人材がいない

⇒ 設計エンジニア、チームリーダーとして

活躍できるエキスパートに

### 中級コース

## 実践的な開発体験を通して即戦力としてのスキル

28nmノード以降のロジック半導体の設計人材育成コース

AIチップ設計拠点の最先端半導体設計・検証環境と試作・動作実績のある SoC 設計資産を活用

実践的な半導体設計技術者を目指す

半導体産業全体の知見を深める講座

高価な先端EDAが使えず、先端設計者を育成できない

⇒ 最新の先端EDAツールをマスターして設計のスペシャリストに

### 初級コース

使用EDAツール: Synopsys, Cadence

## 新人教育や社員のリスキリング

先端半導体設計者を目指す

社会人、学生

大学などにおける専門基礎科目

最先端EDAツールのスペシャリスト育成コース

半導体設計の各工程で利用する最先端EDAツールの使いこなしを学ぶ9つのコース

デジタル回路・アナログ回路における設計フローの各工程で必要なスキルを、集中的に学習

・修了試験合格者には修了証を授与

# 米国を中心とした取り組み

## ・ 投資

- DARPA CRAFTプロジェクト: TSMC 16nm試作の無料試作: 2016~2019(おおむね20億円のプロジェクトで、当時最先端チップ設計試作を無料で大学に提供)

- 複数の成果が国際会議に採択

## ・ 設計者/アーキテクトの欠如

- チップテープアウト講義の実施 (2020~: Appleが資金、Intelが12nm試作無料枠を提供?): 主に大学院 (一部学部生も参加) のセメスターを跨いだテープアウト講義・実習

- 講義の内容にもかかわらず著名国際会議に採択発表されている

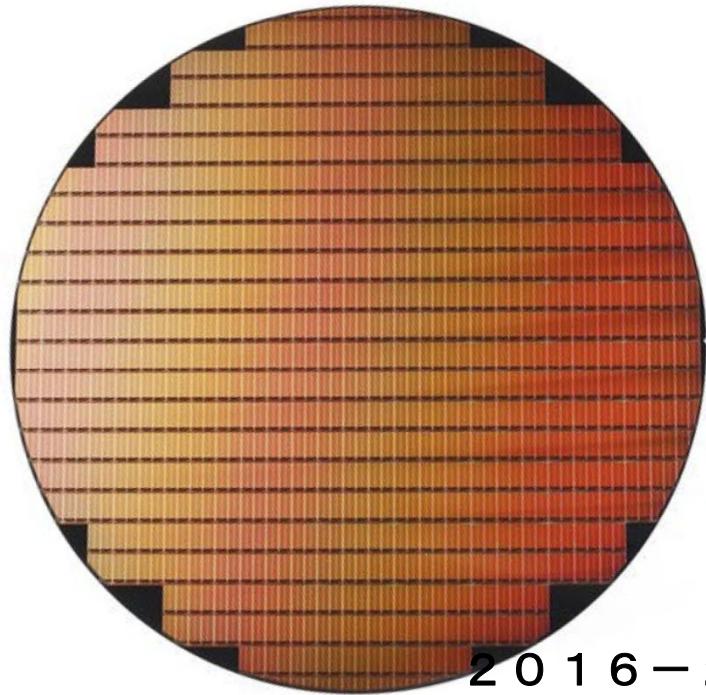

## DARPA multi-project run (MPW) shuttle details

- **ALL runs available to ALL Defense Contractors**

- Wafer diameter: 300mm

- Single exposure area: 26mmX33mm

- Exposures (shots)/wafer: ~80

- Project area unit: 2.5mmX2.5mm

- Projects/shot: ~100

2016 – 2019 の 4 年間 :

1 回のシャトル (5 億円程度? (推測) ) × 4 回? = 20 億

RISC-V Day Tokyo 2025 Autumn/Dec. 4, 2025

DISTRIBUTION A. Approved for public release. Distribution unlimited.

16

# 各国におけるテープアウト講義・・・

| 大学                 | 内容                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETH                | Cadence → OpenSource                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| スタンフォード            | EE271/EE272/EE372/EE391: Intro to VLSI/Chip Design Flow/Tapeout Class/Chip Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CMU                | <p>18-220/240/320 – Core circuits/Core logic design/Basic analog and digital circuits</p> <p>18-422/622 – Introduction to digital VLSI design Fall</p> <p>18-525/725 – Projects in IC design (UG capstone)/Projects in IC design: taping out Spring</p> <p>18-726 – Projects in IC design: first silicon Fall</p> <p>60 students – mix of PhD, MS, and undergrad: Self-formed teams of 4-5 students, 15 projects per class, Digital, mixed-signal, and analog/RF designs: Commercial tool flow (mainly Cadence), TSMC 28nm (added TSMC 180nm this year)</p>                                                                                                                                                                                                       |

| UCSD               | <p>Schematic to Silicon: ADC Tapeout in 10 Weeks, TSMC 65 GP, Cadence workflow, 9 (!) circuits professors, 17 (!) <u>graduate</u>-level circuits classes, 2-quarterで実施 : senior-level undergraduate and first-year graduate</p> <ul style="list-style-type: none"> <li>· ECE 266A (Spring): Physical design and simulation, Chip fabrication (over the summer) &lt;-- Critical for a quarter-based system!</li> <li>· ECE 266B (Fall): Measurement and characterization</li> </ul> <p>First offered in Fall 2021, annually since, enrollment limited to 50, 18 chips taped out (!!!), 200 students have completed the course (~25% PhD, 37% MS, 30% BS-MS, 8% / <a href="https://github.com/ProfDrewHall/SAR_ADC">https://github.com/ProfDrewHall/SAR_ADC</a></p> |

| UCB                | TSMC28nm → Intel 16nm, Mostly undergraduate (EE)CS students, with no chip design experience, Design complete SoCs, by teams of ~20 students, Build a design template (Chipyard) through a series of labs, Students exposed to (almost) every step in the chip design process, Tape out in Spring, fabricate over the Summer, bring up in Fall                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Nortre Dame, IN    | <p>Challenges of EDA in Classroom Environments, Current State of Design in R2/R3 Universities, First Success: CMC Microsystems in HLS and DAC, Howard University Advanced IC Design Course, Improvements for High-Level Synthesis – Flowkit</p> <p>High Cost of Entry: 123 of licensees are R1 institutions: 83% of all R1s Institutes Non-R1s constitute 92 licenses: Only 4.8% of non-R1 technical universities</p> <p>Howard University: Support through Apple New Silicon Initiative, TSMC 180nm R RF G</p>                                                                                                                                                                                                                                                   |

| Morgan State Univ. | <p>Objective: to design an SoC from RTL to GDSII in 15 weeks, Class Size: 30</p> <p>Prerequisites: digital logic design, computer architecture, and microelectronic circuits</p> <p>Foundry access to 16 nm FinFet technology via Intel University Shuttle University Program</p> <p>EDA Tools: Open Source (e.g., Chipyard, OpenTitan) and commercial (Cadence, Siemens, and Synopsys)</p>                                                                                                                                                                                                                                                                                                                                                                       |

## Why teach this kind of course?

- Traditional VLSI curricula emphasize theory but fall short on practical implementation

- This course provides hands-on experience across the full chip lifecycle, from schematic to silicon

- Prepares students to be complete engineers, not just theoreticians or tool operators

- Aligns with industry demand for graduates who understand tools, flows, and post-silicon validation

- Empowers undergraduates with experiences typically reserved for graduate-level research

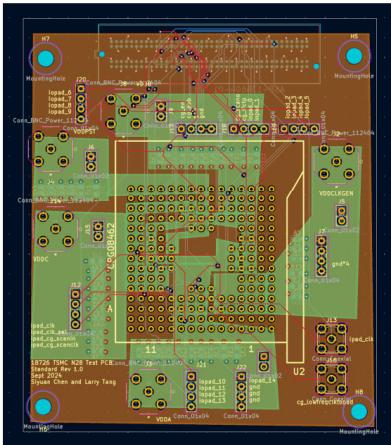

## Standard Test PCB

Standard pad frame → standard packaging → standard PCB

- 4-layer board with segmented power plane

- Students are given schematic version

- Must layout PCB

- But don't design from scratch

- Can add customizations

- Can use TA version if there is an error

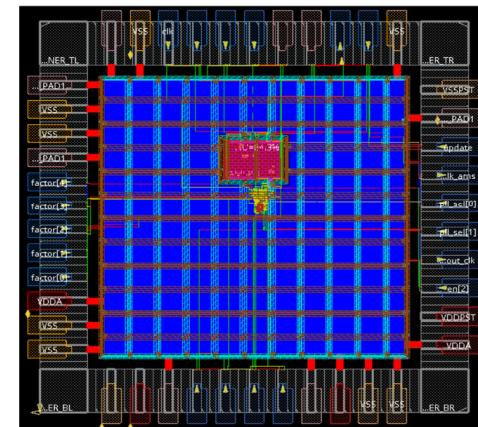

## Standard Pad Frame and Assignment

- 1mm x 1mm pad frame w/ 43 pads

- Asym 12/11/11/10 arrangement

- 7+7 pads for VDD{A/B/C}/VSS for three core power domains

- 15 signal pads that you can use for your design (W S E sides)

- 2+2 pads for VDDPST/VSSPST

- 1+1 pads for VDD\_CLKGEN/VSS

- 8 signal pads reserved for clock generator control (N side)

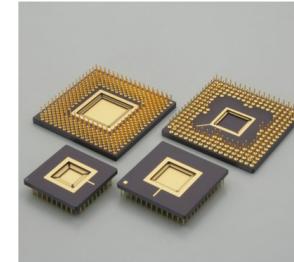

## Standard Package

84-pin ceramic PGA - CPG08462

- 84 pins (more than) enough for 43 pads

- 5mm x 5mm die cavity

- 2mm bond wires for 1mm x 1mm die

- Order 10 packages per project @ \$20/pkg

- Compatible with readily available sockets

# ESSERC2025での驚き

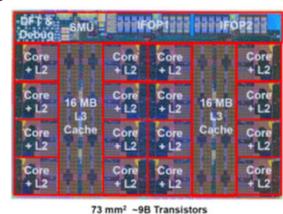

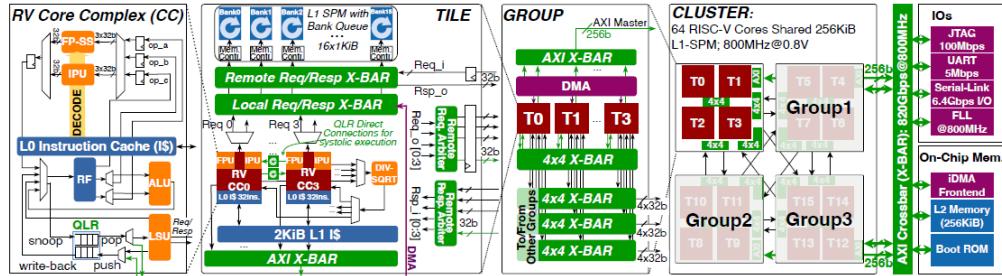

## A 410 GFLOP/s, 64 RISC-V Cores, 204.8 GBps Shared-Memory Cluster in 12 nm FinFET with Systolic Execution Support for Efficient B5G/6G AI-Enhanced O-RAN

Yichao Zhang\* Marco Bertuletti\* Sergio Mazzola\* Samuel Riedel\* Luca Benini\*†

\*IIS, ETH Zürich †DEI, University of Bologna

{yiczhang, mberuletti, smazzola, sriedel, lbenini}@iis.ee.ethz.ch

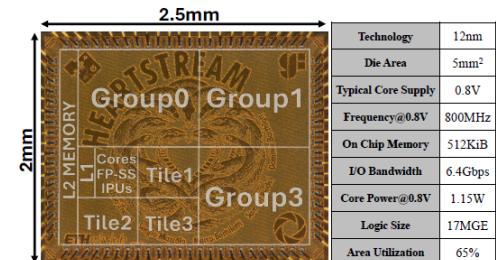

Fig. 2. HeartStream's 64 RISC-V cores shared-L1-memory hierarchical design architecture. L1 memory addresses are 32-bit interleaved across banks of 16 Tiles in 4 Groups. Each Tile's cores share an FP division/square-root unit. Core-Complex includes a 32b RISC-V core, IPU, FP-SS, and Systolic QLR.

Fig. 3. Die micrograph and design summary. HeartStream was implemented in GlobalFoundries' 12 nm FinFET technology on a 5 mm<sup>2</sup> die. It achieves a 65% high utilization logic cell placement in the core area.

a Floating Point Sub-System (FP-SS). For efficient software-defined O-RAN, both units support domain-specific instructions: Multiply&Accumulate (MAC), load-post-increment operations, SIMD operations, efficient complex arithmetic, widening sum-of-dot-product, and three-term addition instructions [9]. One Tile-shared FP division&square-root unit helps to accelerate matrix-inversion for MIMO detection. A key efficiency booster is hardware-supported flexible systolic execution with programmable tonology [10] within the shared-memory cluster.

### ACKNOWLEDGMENT

This work has received funding from the Swiss State Secretariat for Education, Research, and Innovation (SERI) under the SwissChips initiative.

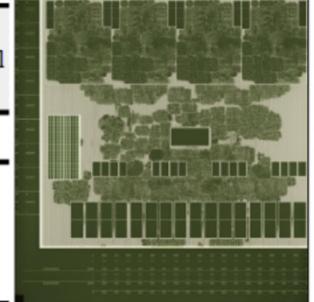

## COSMIC: A Multi-Vector-Core Heterogeneous RISC-V SoC for Intelligent Audio DSP in Intel 16

Ethan Gao, Jasmine Angle, Lucy Revina, Jacob Leigh, Wenda Zhang, Naichen Zhao, Tushar Goyal, Michael McCulloch, Jonathan Wang, John Lomax, Jessica Fan, Mihai Tudor, Rachel Lowe, Ted Kim, Kevin He, Nico Castaneda, Anto Kam, Rahul Kumar, Rohan Kumar, Felicity Akitan, Connor Dang, Shichen Qiao, Joshua Lin, Andy Chen, Minh Nguyen, Vedang Joshi, Bryan Ngo, Ella Schwarz, Ken Ho, Viansa Schmulbach, Nikhil Jha, Yufeng Chi, Jerry Zhao, Borivoje Nikolic

University of California Berkeley, CA, USA evgao@eecs.berkeley.edu

| Chip Specifications |                   | IP Blocks              |

|---------------------|-------------------|------------------------|

| Technology          | Intel 16 FinFET   | Vector Cores, DMA      |

| Area                | 4 mm <sup>2</sup> | FFT, Convolution Accel |

| Scratchpad          | 32 kB             | I <sup>2</sup> S Audio |

| Operation           | Nominal           | Functional             |

| Voltage             | 0.85 V            | 0.55–1.10 V            |

| Frequency           | 900 MHz           | 50–1250 MHz            |

| Power               | 340 mW*           | 10.9–875 mW*           |

| Energy Efficiency   | 254 GOPS*/W       | 137–440 GOPS*/W        |

\*power and MAC operations on 4 fully saturated vector cores (2 ops / MAC)

### ACKNOWLEDGMENT

This project is the work of many in UC Berkeley's special topics chip tapeout and bring-up classes. We thank Apple's New Silicon Initiative for supporting the tapeout class through guest lectures, design reviews, and funding for course staff; and Intel University Shuttle Program for donating the chip fabrication and packaging, and NSF CCRI ENS #2016662 and NSF POSE 2303735 Awards. We acknowledge Jared Zerbe, Ajith Amerasekera, Eric Smith and Ramesh Abhari from Apple, and Bryan Casper, Matt Rebsom, and Nancy Robinson from Intel for support, SLICE and BWRC students, staff, and, and member companies.

# ご清聴ありがとうございます