## オープンソースIP, PDK, EDAツール活用による RISC-Vチップの開発

OT × デジタル

2025年12月4日

株式会社 日立産業制御ソリューションズ

コネクティブエンジニアリング事業部

デジタル基盤ソリューション本部

セミコンダクタ第一設計部

中島 伸盛

で、次の安全・安心・快適な社会へ

# 日立産業制御ソリューションズ

<Mission> 人々の生活を安全・安心で豊かなものにするため、優れた技術で新しい価値を提供し、社会の発展に貢献する。

日立製作所

コネクティブインダストリーズ

インダストリアルAIビジネスユニット

エンタープライズソリューション事業部

ソリューション&サービス事業部

日立産業制御ソリューションズ

トータルシームレスソリューション統括本部

## 日立産業制御ソリューションズ Hitachi Industry & Control Solutions, Ltd.

- 代表者：取締役社長 上田 元春

- 設立：2014年4月

- 資本金：30億円（日立製作所 100% 出資）

- 売上高：820億円（2024年度）

- 社員数：3,550名（2025年4月）

- 本社：

○東京本社（ショールーム“未来”）

東京都台東区秋葉原（秋葉原大栄ビル）

○茨城本社

茨城県日立市大みか町

### ●他の拠点

- ・事業所：3カ所（横浜、日立、ひたちなか）

- ・オフィス：1カ所（名古屋）

- ・支店・営業所：4カ所（水戸、名古屋、大阪、広島）

複雑化していくシステムに

「OT×デジタル」で挑む

# 日立産業制御ソリューションズ コネクティブエンジニアリング事業部概要

数十年<sup>\*1</sup> におよぶ『組込み』製品開発に貢献

## 自動車分野・CASE<sup>\*2</sup>

- ✓ 設計支援(SE/MBSE<sup>\*3</sup>、MBD<sup>\*4</sup>)

- ✓ 車載情報・車両制御(IVI<sup>\*5</sup>、コネクティビティ)

- ✓ 規格・法規(機能安全、セキュリティ、CI/CD<sup>\*6</sup>)

- ✓ 自動運転開発支援(AD/ADAS<sup>\*7</sup>、センシング)

- ✓ EV開発支援(インバーター制御、バッテリー制御)

- ✓ 新技術開発支援(AUTOSAR、SDV<sup>\*8</sup>、OTA<sup>\*9</sup>)

**実績：自動車メーカー 11社

サプライヤー 35社以上**

## パワエレ

- ✓ モーター・インバーター制御開発(EV、産業機器など)

- ✓ 統合解析(複雑に影響しあうシステムの温度・ノイズの解析)

## 半導体・組込みOS

- ✓ 映像処理 / 分析技術

- ✓ アーキテクチャ設計支援

- ✓ 各種OS / マイコン対応

- ✓ SoC<sup>\*10</sup> / FPGA<sup>\*11</sup>

- ✓ 組込みプラットフォーム開発

- ✓ CASE対応組込み開発

**実績：携帯電話、

家電・映像製品ほか**

## 産業・医療分野、ほか

- ✓ 医療関連(内視鏡、医療情報システム)

- ✓ 建機・農機関連

- ✓ ビル・交通・鉄道関連

<sup>\*1</sup> 前身組織からの実績 \*2) CASE : Connected, Autonomous/Automated, Shared, Electric \*3) SE/MBSE : Systems Engineering/Model-based Systems Engineering \*4) MBD : Model Based Development \*5) IVI : In-Vehicle Infotainment

\*6) CI/CD : Continuous Integration / Continuous Delivery \*7) AD/ADAS : Autonomous Driving/Advanced Driver Assistance System \*8) SDV : Software Defined Vehicle \*9) OTA : Over-the-Air \*10) SoC : System on a chip \*11) FPGA : Field Programmable Gate Array

# Contents

## 1. はじめに

- 1.1 現状の市場動向とその背景

- 1.2 日立産業制御ソリューションズの取り組み

## 2. 取り組み事例について

- 2.1 RISC-Vチップの試作開発

- 2.2 試作開発の進め方

- 2.3 試作開発の進捗状況

- 2.4 課題と今後の取り組み

## 3. おわりに

- 3.1 まとめ

# 1. はじめに

- 1.1 現状の市場動向とその背景

- 1.2 日立産業制御ソリューションズの取り組み

1

## 1.1 現状の市場動向とその背景

# 半導体開発には多額の投資が必要

ロングテール需要者は、特定用途・専用機能を搭載したSoCを開発しにくい。

## 半導体市場の現状

▶ 半導体を開発できるのは大手企業に偏っている

理由としては、

- ・日本の半導体産業全体が大手主導

- ・技術的・資金的ハードルが高い

- ・ファブレスとの関係性

(中小企業はNDAや最低発注量の壁があり)

ロングテール需要者は、特定用途のSoC開発に際して、必要以上の機能を搭載した汎用SoCに頼らざるを得ない

## 1.2 日立産業制御ソリューションズの取り組み

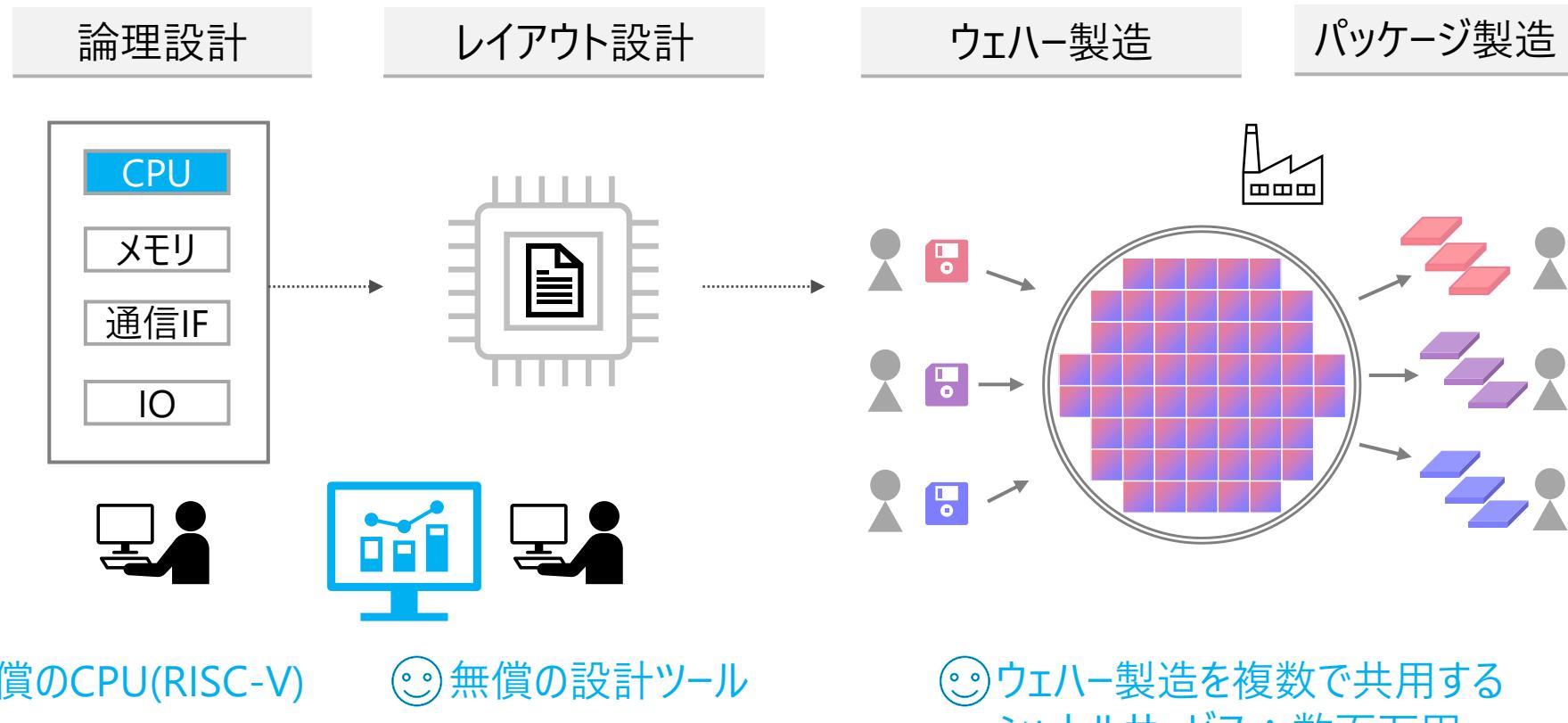

# RISC-Vと無償EDA、ウェハー共有で低コストチップ製作の機会が到来

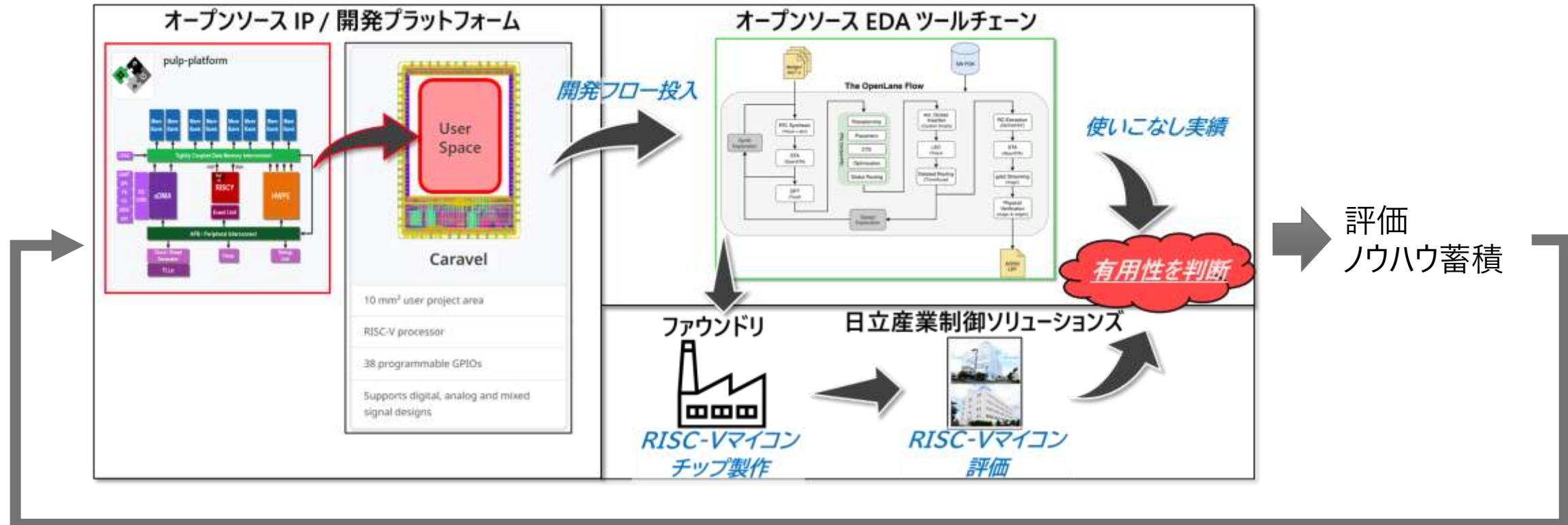

RISC-Vに加え、オープンソースEDAツールやウェハー共有サービスの活用により、低成本でのチップ製作が可能となった。日立産業制御ソリューションズでは、試作・製造・評価を通じて、品質やサポート体制を検証する取り組みを実施。

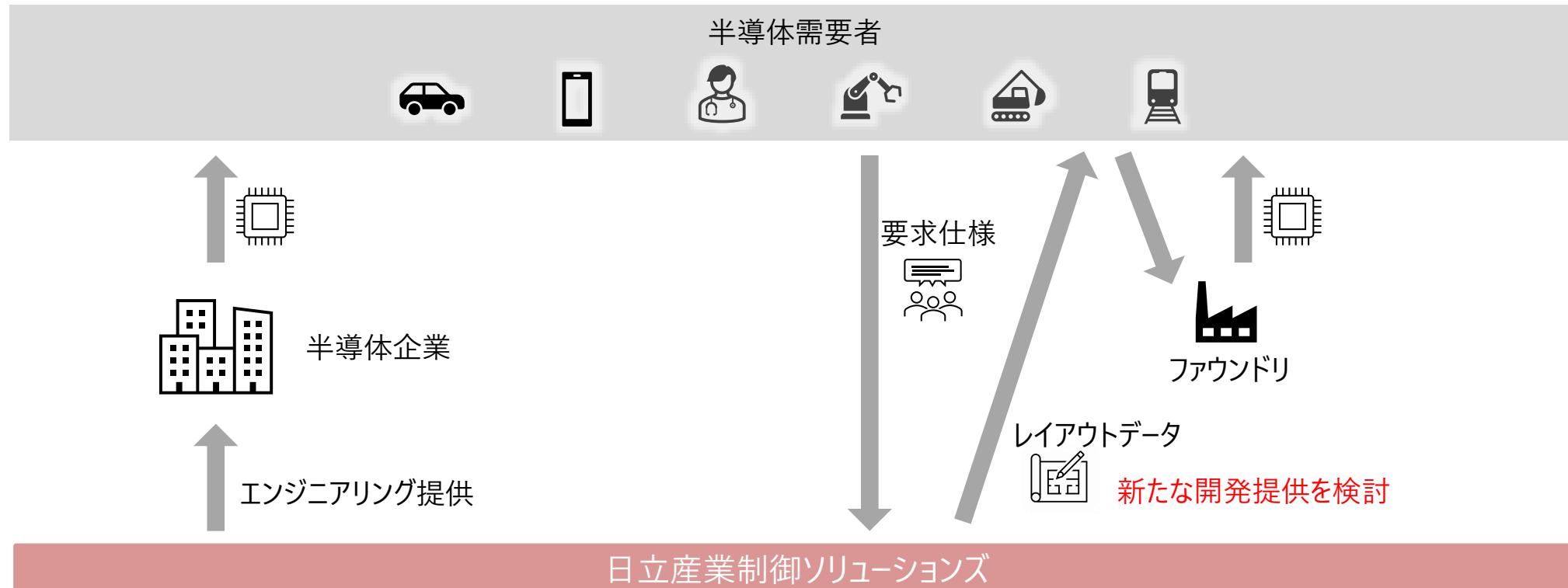

## 1.2 日立産業制御ソリューションズの取り組み

## 日立産業制御ソリューションズでは、新たな半導体開発提供を検討

日立産業制御ソリューションズは半導体企業向けにエンジニアリングサービスを提供している。今回、試作・製造・評価を通じて品質やサポート体制を検証し、新たな半導体開発提供の実現可能性を検討することを目的としている。

## 1.2 日立産業制御ソリューションズの取り組み

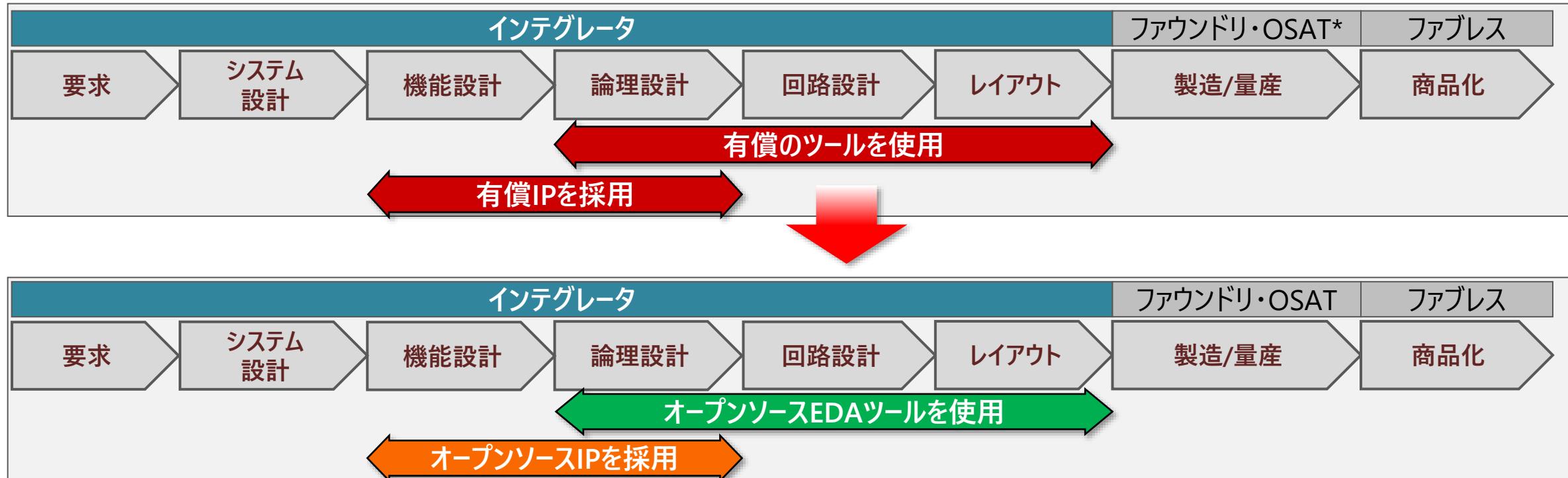

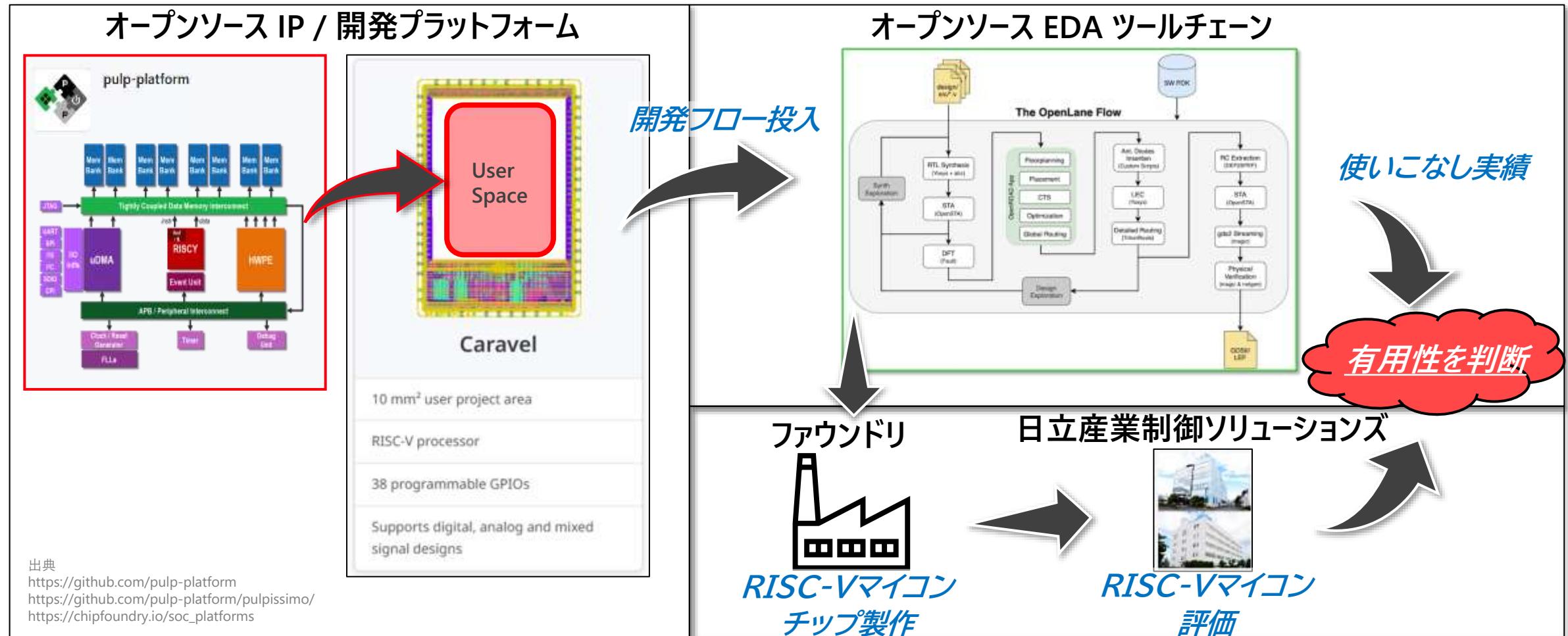

# オープンソース活用を試行・評価し、有用性を判断したい

本日は、オープンソースを活用した設計の取り組み内容をご紹介します。

判断基準1. 品質

判断基準2. サポートの不確実性

商用に比べて機能が限定的であり、性能面に懸念あり。

問題が発生した際に技術サポートが受けられない可能性がある。

\* OSAT: Outsourced Semiconductor Assembly and Test

## 2.取り組み事例について

- 2.1 RISC-Vチップの試作開発

- 2.2 試作開発の進め方

- 2.3 試作開発の進捗状況

- 2.4 課題と今後の取り組み

## 2.1 RISC-Vチップの試作開発

# オープンソースのIP, PDK, EDAツールの有用性を判断する

## 2.1 RISC-Vチップの試作開発

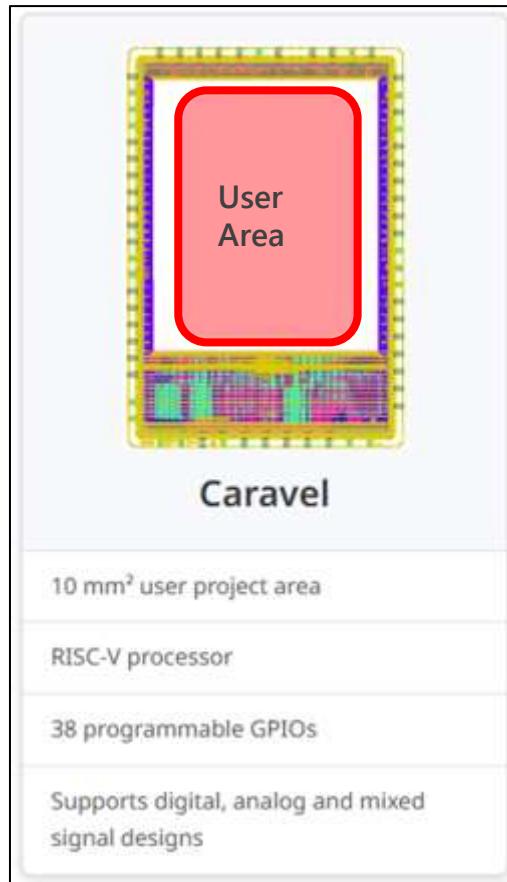

# シャトルサービスを利用してRISC-Vマイコンを製造

出典 [https://chipfoundry.io/soc\\_platforms](https://chipfoundry.io/soc_platforms)

## Caravel (ChipFoundry)

- [https://chipfoundry.io/soc\\_platforms](https://chipfoundry.io/soc_platforms)

- 10 mm<sup>2</sup> ユーザ論理エリア

- GPIO 38 pin

- SkyWater's 130nm PDK

## chipIgnite – MPW(Multi-Project-Wafer)サービス (ChipFoundry)

- <https://chipfoundry.io/chipignite>

- 14,950 USD

- CI2511 シャトルにエントリー

- テープアウト 2025年11月11日 期限 → 12月2日に延期

- デリバリー 2026年 5月 2日 予定 (評価ボード含)

## 2.1 RISC-Vチップの試作開発

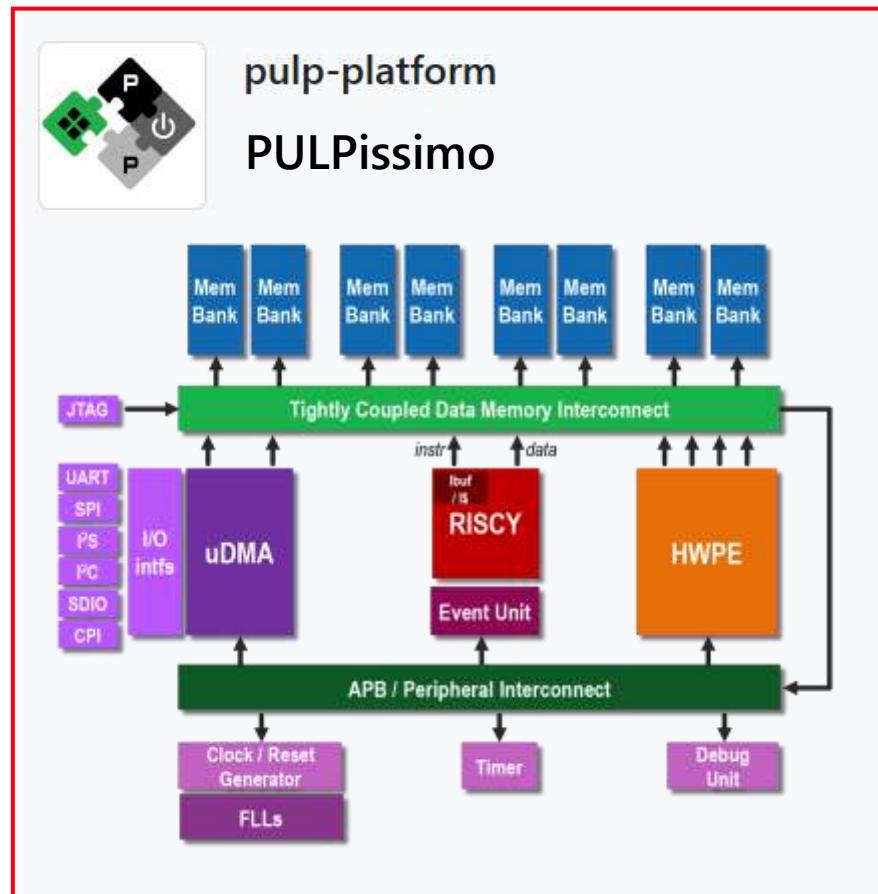

# オープンソースIPを活用してRISC-Vマイコンを設計

出典 <https://github.com/pulp-platform>

<https://github.com/pulp-platform/pulpissimo/>

## Parallel Ultra Low Power (PULP) platform

- <https://pulp-platform.org/>

- ETHチューリッヒとボローニヤ大学によるプロジェクト(2013～)

- オープンなハードウェア・ソフトウェアの開発プラットフォームを提供

- IoTからHPCまでスケーラブルなアーキテクチャ

## PULPissimo

- <https://github.com/pulp-platform/pulpissimo/>

- PULP-platformの中のマイコンアーキテクチャの1つ

- RISC-Vシングルコアと周辺IFを含むサブシステムで構成される

- CV32E40P(RI5CY) : 32bit 4-stage core

- uDMAを備えた周辺IF (UART, SPI, I2C, ...)

- HWPE (Hardware Processing Engines) をサポート

- System Verilogでコーディング

## 2.1 RISC-Vチップの試作開発

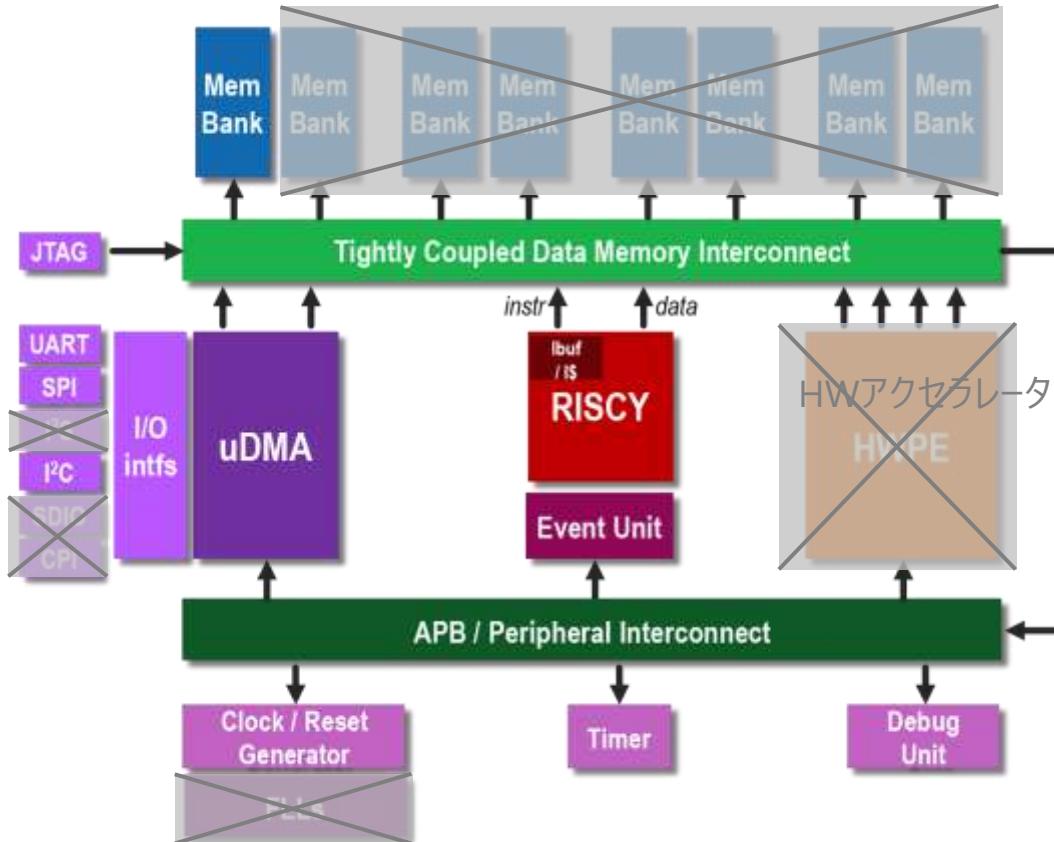

# 最初のステップとして必要最小限のリソースを持つRISC-Vマイコンを試作

Caravelの制約事項（面積）により機能・性能を削減

出典 <https://github.com/pulp-platform>

<https://github.com/pulp-platform/pulpissimo/>

|           |                                                                                 |

|-----------|---------------------------------------------------------------------------------|

| CPU       | RISC-V 32bit 5-stage シングルコア<br>CV32E40P FPUなし                                   |

| HWアクセラレータ | なし                                                                              |

| 動作周波数     | 25MHz                                                                           |

| 内蔵SRAM    | 32kB                                                                            |

| Boot Rom  | 2kB                                                                             |

| I/F       | UART(1), SPI master(1), I2C(1),<br>JTAG(1), GPIO(14)<br>非搭載 : I2S, SDIO, CPIは削除 |

| Pin数      | 64pin QFN (ユーザー割当38pin)                                                         |

| タイマー      | あり                                                                              |

| ADC, DAC  | なし                                                                              |

| 動作電圧      | コア電圧(1.8V), IO電圧(3.3~5.0V)                                                      |

| 動作温度      | 0~75°C                                                                          |

## 2.1 RISC-Vチップの試作開発

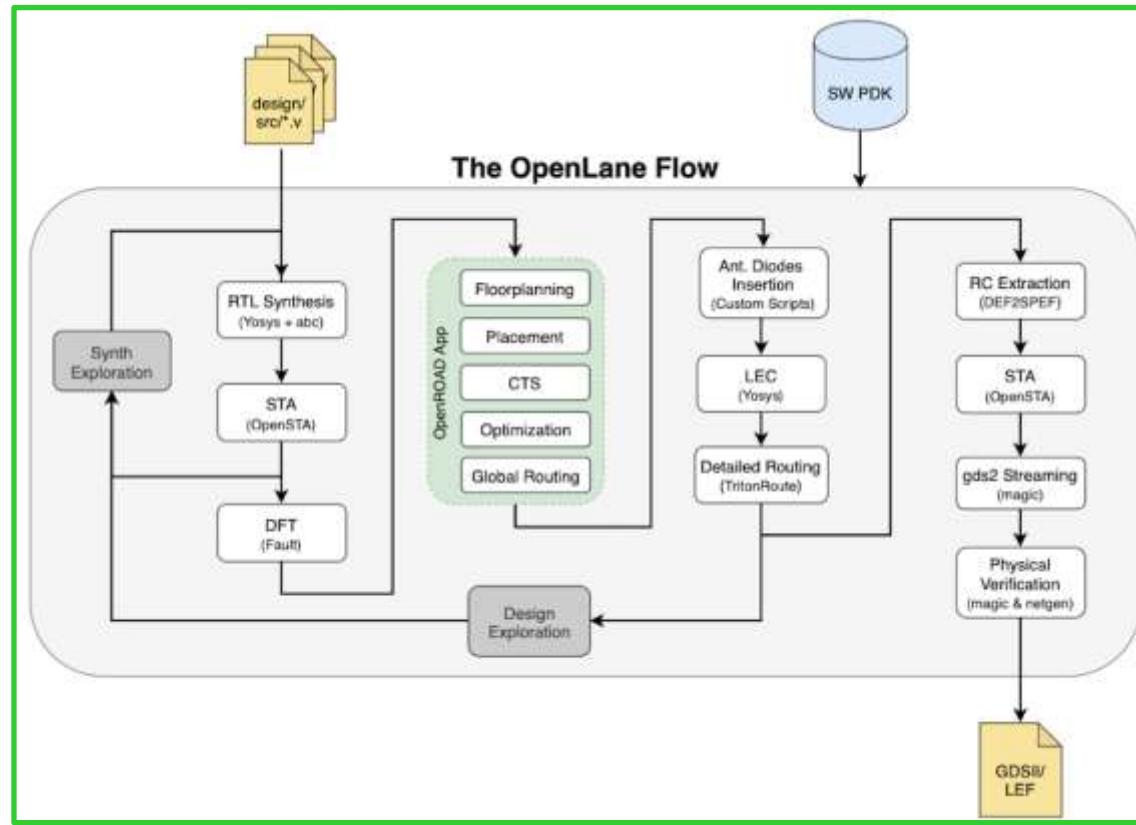

# オープンソース EDA ツールチェーンを利用

出典 [https://github.com/The-OpenROAD-Project/OpenLane/blob/superstable/docs/source/flow\\_overview.md](https://github.com/The-OpenROAD-Project/OpenLane/blob/superstable/docs/source/flow_overview.md)

## OpenLane

- <https://github.com/chipfoundry/openlane-2/>

- RTLから物理レイアウト、GDSII作成までの全工程を自動化したツールチェーン

- 多様なオープンソースEDAツールを統合

- OpenROAD, Yosys, Magic, Netgen, CVC, SPEF-Extractor, Klayout

- 検証は別途 ICARUS Verilog や FPGA を活用

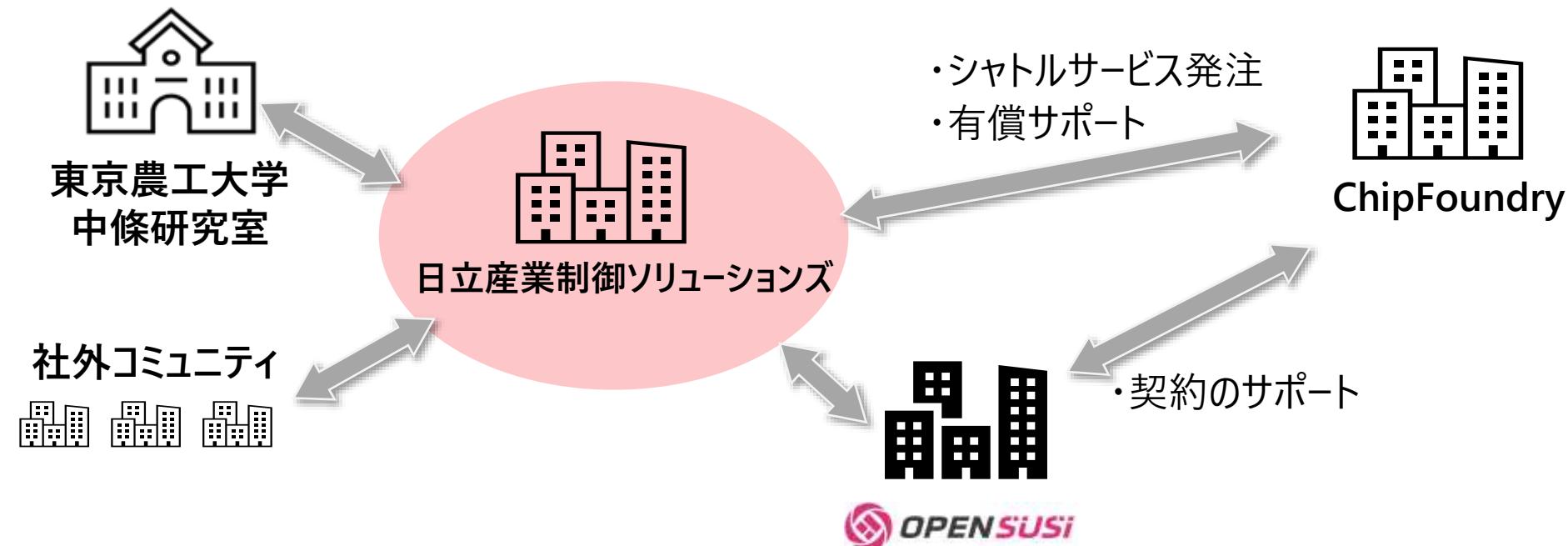

## 2.2 試作開発の進め方

## 社外組織とも連携し、試作開発を加速

- ・ 東京農工大学 中條研究室との共同研究による開発推進

- ・ OpenSUSI によるChipFoundryとのシャトルサービス契約サポート

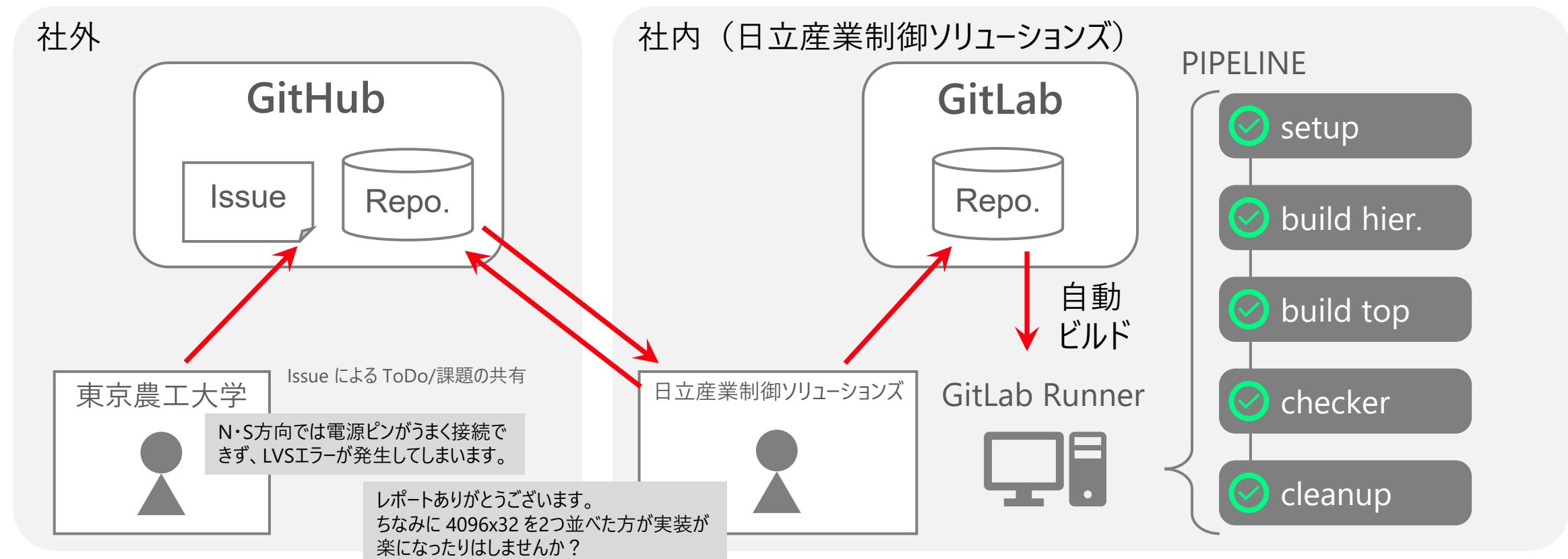

## 2.2 試作開発の進め方

## ソーシャルコーディングツールを活用しCI環境を構築

- 東京農工大学 中條研究室とGitHubを使用したソースの共有

- 社内にGitLabを使用したCI - Continuous Integration - 自動ビルド環境を構築

## 2.2 試作開発の進め方

# OpenSUSIのご支援をいただきシャトルサービスへの発注を実現

## 【発注前】

## 【発注】

社内の調達部門との調整や、輸出管理手続き、オープンソースIPのライセンス調査の実施も必要

## 2.3 試作開発の進捗状況

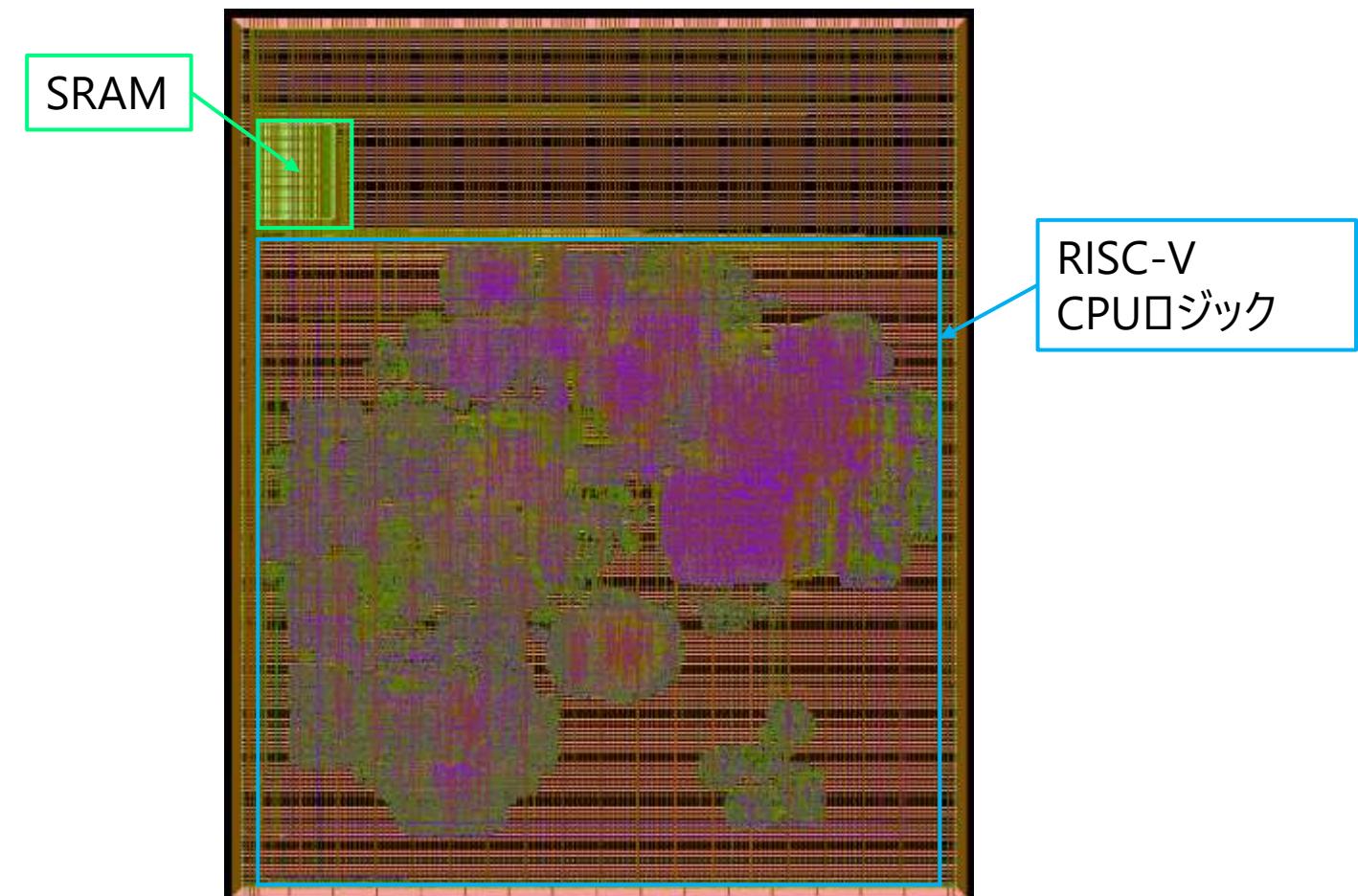

# RISC-Vマイコンをテープアウト

12月2日にGDSデータ提出

2026年5月2日 評価ボード 納入予定

実機評価実施予定

KLayoutによるGDSファイル表示

## 2.4 課題と今後の取り組み

## 試作開発の実施によりさまざまな課題を抽出

| # | 課題                                 | 対応                                                                                                                                                                                     |

|---|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | YosysがSystem Verilogに対応していない       | <ul style="list-style-type: none"> <li>System VerilogをVerilogに変換するオープンソース・ツールを複数試行 (Synlig, sv2v)</li> <li>どちらのVerilogもSyntax Error発生→自力で変換</li> <li>ツールによる変換前後の論理一致性検証が未実施</li> </ul> |

| 2 | OpenRAMによるRAMマクロを実装すると DRCエラー      | <ul style="list-style-type: none"> <li>おそらく無視できるはずだがエラー回避手段が見つからず…</li> <li>今回はCommercial SRAMを使用</li> </ul>                                                                           |

| 3 | RTLビューワーが無く、大規模なオープンソース IP論理の把握に苦労 | <ul style="list-style-type: none"> <li>FPGA開発ツールを補助的に使用したが、商用ツールには及ばない</li> </ul>                                                                                                      |

| 4 | タイミング違反パスの個別調整できない                 | <ul style="list-style-type: none"> <li>タイミング違反パスを個別に調整することができないため、OpenLaneの設定ファイル (config.json) のパラメータを試行錯誤的に調整</li> <li>論理の階層分離、レイアウトも試行錯誤</li> </ul>                                 |

| 5 | サポート体制やドキュメントが不足                   | <ul style="list-style-type: none"> <li>ChipFoundryの有償サポートを契約</li> <li>ドキュメントが更新されていないため、ソースコードベースでの機能動作把握が常となる</li> </ul>                                                              |

## 2.4 課題と今後の取り組み

# 今後も評価・機能実装のサイクルを回し 実開発適用の可否を判断

実開発適用の可否を判断したい（商用IP/開発ツールとのすみわけ）

- ・商用ツールとの機能・品質観点での差の把握

- ・適用可能な製品ターゲット・用途の検討

出典

<https://github.com/pulp-platform>

<https://github.com/pulp-platform/pulpissimo/>

[https://chipfoundry.io/soc\\_platforms](https://chipfoundry.io/soc_platforms)

[https://github.com/The-OpenROAD-Project/OpenLane/blob/superstable/docs/source/flow\\_overview.md](https://github.com/The-OpenROAD-Project/OpenLane/blob/superstable/docs/source/flow_overview.md)

## 2.4 課題と今後の取り組み

# オープンソースIP, PDK, EDAツールの知見・ノウハウ蓄積を今後も推進

## オープンソースIPの選定と評価

- ✓ オープンソースIPの調査・収集と品質評価

(CPU, 周辺IP, ハードマクロなど選択肢拡充)

- ✓ IP利活用のためのガイドライン作成

(導入前チェック項目や解析手法の確立)

## オープンソースPDK, EDAでの設計最適化

- ✓ 性能・面積・電力見積によるライブラリ選択

- ✓ 階層分割によるレイアウト最適化

## 検証・シミュレーション環境の構築

- ✓ RTLシミュレーション環境の構築と拡充

- ✓ RISC-V ISAテストスイートの導入とカスタマイズ

## ツールチェーンの構成と運用方法

- ✓ 各ツールの役割と連携方法

- ✓ バージョン管理と依存関係の整理

- ✓ CI/CD環境の拡充

## 合成・配置配線フローの最適化

- ✓ 合成、配置配線、DRC/LVSのパラメータ調整

- ✓ エラー発生時のトラブルシューティング手順

## PDK (Process Design Kit) の取り扱い

- ✓ オープンPDKの構造、活用方法の見える化

## 3. おわりに

### 3.1 まとめ

3

## 3.1 まとめ

# オープンソースを活用した半導体チップ開発の知見・ノウハウを蓄積

## 半導体市場の動向

オープンソースIP, PDK, EDAツールの活用により開発コストを低減

品質課題

商用IP/開発ツールとのすみわけ

- 従来品相当の機能・品質はそもそも難しい

- 製品ターゲット・用途は絞る必要がある

サポートの不確実性

## 日立産業制御ソリューションズの取り組み

社外組織とも連携し、オープンソースを活用した開発フローを試行

評価観点を定め段階的に評価

設計過程の知見・ノウハウを蓄積

今後、商用IP/開発ツールだけでなくオープンソースIP/開発ツールも活用した開発をサポート

# ご清聴ありがとうございました

- RISC-Vは、Asanovic, Krsteの登録商標です。

- Open SUSIは、株式会社AIST Solutionsの登録商標です。

- その他記載の会社名、製品名は、それぞれの会社の商号、商標もしくは登録商標です。

- 一部の図は、「OpenLane」、「PULPissimo」、「Caravel」の成果物を基にしており、Apache License 2.0に準拠しています。

**HITACHI**