Sponsors

RISC-V Day Online Vietnam 2020 Program Schedule

September 18, 2020 (Fri) 10:00 – 17:00 ICT (Indochina Time, GMT+7)

The hashtag for the conference is #riscv_day.

| Time | Lang | Presentation Title | Speaker | Affiliation | Media |

|---|---|---|---|---|

| 10:00 | E | Welcome and Introduction from Moderator | Takahiro Kitayama*| KAMAKE no SUSUME Corp. | |

| 10:10 | E | Why Are We Using RISC-V as a Model Processor for University Education? | Hideharu Amano* | Keio University | Video |

| 10:40 | E | RISC-V: Instruction Sets Want to be Free | Krste Asanovic*, Chairman, RISC-V International / University of California, Berkeley | Video |

| 11:10 | V | Vanguard – the first Open Source RISC-V SoC project in Vietnam | VLSI Technology Page, Quynh Do-ngoc* and Quan Nguyen-hung | Video |

| 11:40 | E | Advanced SIMD architecture derived by applying RISC-V architecture | Yamaguchi Yoshiki*, Tan Yuxi, and Abdelhamid Riadh Ben | University of Tsukuba | Video |

| 12:10 | E | RISC-V Linux Distro Status and Build System for RPM-like System | Wei Fu | Senior Software Engineer, Red Hat Software (Beijing) Co., Ltd.Shanghai Branch | Video |

| 12:40 | ー | Intermission | Intermission | |

| 13:10 | V | Microprocessors: X86, ARM, and the future is RISC-V | Thang Tran, Ph.D | Principal Engineer, Andes Technology | Video |

| 13:40 | E | TEE Hardware for RISC-V Implementation | Ckristian Duran*, Trong-Thuc Hoang, Cong-Kha Pham | UEC, Akira Tsukamoto, Kuniyasu Suzaki | AIST, TRASIO | Video |

| 14:10 | E | ASA RISC-V Processor Optimized For Edge AI/ML, Security, Smart IoT Sensors | Islam Md Ashraful*, ASAMicro | Video |

| 14:40 | E | RISC-V Dedicated High-Performance Computers for Designing Medicine | Makoto Taiji*, RIKEN Center for Biosystems Dynamics Research | Video |

| 15:10 | V | Research and Development Activities on RISC-V and its Applications for IoTs | Duy-Hieu Bui* | SISLAB, VNU University of Engineering and Technology, and Xuan-Tu Tran | Vietnam National University, Hanoi | Video |

| 15:40 | E | Digital Design in Chisel | Martin Schoeberl*, Associate Professor, Technical University of Denmark | Video |

| 16:10 | E | New RISC-V Security Directions | Shumpei Kawasaki*, SH Consulting Vietnam Company Limited | Video |

| 16:40 | E | AI: Scale from Edge to Server with RISC-V and Linux | Florian Wohlrab*, Head of Sales for EMEA and Japan, Andes Technology | Video |

| 17:10 | V | Greetings from Organizer (Message Read) | Cong-Kha Pham*, University of Electro-Communications | Video |

Virtual Demo Booth

The virtual demo booth provides opportunities for visitors to “see” demos and ask questions through a live streaming.

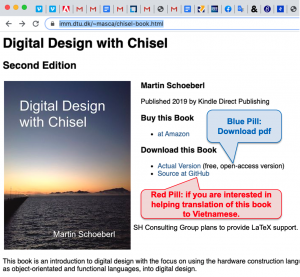

A Book of Interest

This book is an introduction into digital design with the focus on using the hardware construction language Chisel. Chisel brings advances from software engineering, such as object-orientated and functional languages, into digital design.This book addresses hardware designers and software engineers. Hardware designers, with knowledge of Verilog or VHDL, can upgrade their productivity with a modern language for their next ASIC or FPGA design. Software engineers, with knowledge of object-oriented and functional programming, can leverage their knowledge to program hardware, for example, FPGA accelerators executing in the cloud.The approach of this book is to present small to medium-sized typical hardware components to explore digital design with Chisel. Press here and choose red pill or blue pill.

Looking forward to seeing you all !