# RISC-V

#### Instruction Sets Want to be Free

RISC

Krste Asanovic Prof. EECS, UC Berkeley; Chairman, RISC-V Foundation; Co-Founder and Chief Architect, SiFive Inc.

Why Instruction Set Architecture matters

## Why can't Intel sell mobile chips?

- 99%+ of mobile phones/tablets based on ARM v7/v8 ISA

- Why can't ARM partners sell servers?

- 99%+ of laptops/desktops/servers based on AMD64 ISA (over 95%+ built by Intel)

- How can IBM still sell mainframes?

- IBM 360, oldest surviving ISA (50+ years)

# ISA is most important interface in computer system where software meets hardware

# **Open Interfaces Work for Software!**

| Field      | Open Standard    | Free, Open Implement. | Proprietary Implement. |

|------------|------------------|-----------------------|------------------------|

| Networking | Ethernet, TCP/IP | Many                  | Many                   |

| OS         | Posix            | Linux, FreeBSD        | M/S Windows            |

| Compilers  | С                | gcc, LLVM             | Intel icc, ARMcc       |

| Databases  | SQL              | MySQL, PostgresSQL    | Oracle 12C, M/S DB2    |

| Graphics   | OpenGL           | Mesa3D                | M/S DirectX            |

| ISA        | ?????            |                       | x86, ARM, IBM360       |

3

Why not successful free & open standards and free & open implementations, like other fields?

# **Companies and their ISAs Come and Go**

- Digital Equipment Corporation, RIP! (PDP-11, VAX, Alpha)

- Intel's dead ISAs (i960, i860, Itanium, ...)

- SPARC

- Sun opened v8 as IEEE 1754-1994, acquired by Oracle, all closed down

- MIPS

- Sold to Imagination, bought by Wave

- Opened up MIPS R6 ISA in 2018, then made not open in 2019

#### IBM POWER

- Initially proprietary, now ISA opened as OpenPower

- ARM

- Sold to Softbank at >40% premium in 2016

- Nvidia now acquiring ARM

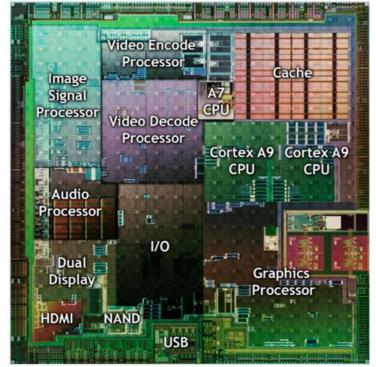

# Today, many ISAs on one SoC

- Applications processor (usually ARM)

- Graphics processors

- Image processors

- Radio DSPs

- Audio DSPs

- Security processors

- Power-management processor

- > dozen ISAs on some SoCs each with unique software stack

### Why?

- Apps processor ISA too big, inflexible for accelerators

- IP bought from different places, each proprietary ISA

- Engineers build home-grown ISA cores

NVIDIA Tegra SoC

5

# Do we need all these different ISAs? Must they be proprietary? Must they keep disappearing?

What if there was one stable free and open ISA everyone could use for everything?

6

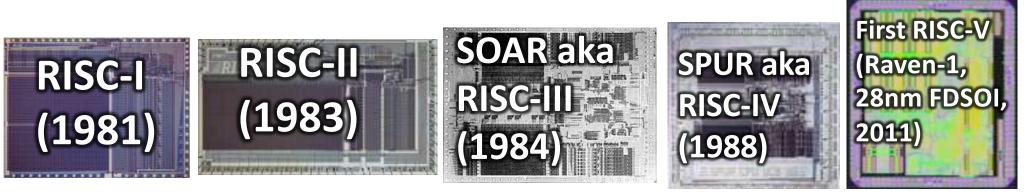

# **RISC-V Background**

- In 2010, after many years and many research projects using MIPS, SPARC, and x86, time for architecture group at UC Berkeley to choose ISA for next set of projects

- Obvious choices: x86 and ARM

- x86 impossible too complex, IP issues

- ARM mostly impossible complex, no 64-bit in 2010, IP issues

- So we started "3-month project" during summer 2010 to develop clean-slate ISA

- Principal designers: Andrew Waterman, Yunsup Lee, David Patterson, Krste Asanovic

- Four years later, May 2014, released frozen base user spec

- many tapeouts and several research publications along the way

- Name RISC-V (pronounced "risk-five") represents fifth major Berkeley RISC ISA

# **RISC-V** International

- **RISC-V** is the opensource hardware Instruction Set Architecture (ISA)

- Frozen base user spec released in 2014, contributed, ratified, and openly published by RISC-V International

**RISC-V International** is a non-profit entity serving members and the industry

Our mission is to accelerate RISC-V adoption with shared benefit to the entire community of stakeholders.

- Drive progression of ratified specs, compliance suite, and other technical deliverables

- Grow the overall ecosystem / membership, promoting diversity while preventing fragmentation

- Deepen community engagement and visibility

# CHINA

MORE THAN 200 MEMBERS HAVE JOINED THE CRVA AND CRVIC ASSOCIATIONS AS WELL AS 33 MEMBERS IN THE GLOBAL RISC-V FOUNDATION. ACROSS 2019 WE'VE LED DISCUSSIONS IN 6 CITIES AS WELL AS HOSTED A DAY OF TALKS AT THE WORLD INTERNET CONFERENCE. IN NOVEMBER, WE HOSTED 500 ATTENDEES AT THE CHINA RISC-V FORUM.

# EUROPE

THE EUROPEAN PROCESSOR INITIATIVE HAS DECLARED RISC-V AS A KEY ARCHITECTURE FOR THE NEXT GENERATION OF HPC PROCESSORS AND SYSTEMS, FOCUSED ON ACCELERATION.

# INDIA

2014 WITH THE FUNDING OF 6 RISC-V PROCESSORS THROUGH THE SHAKTI PROJECT, RISC-V HAS BEEN WIDELY DECLARED THE NATIONAL ARCHITECTURE OF INDIA.

# JAPAN

MOMENTUM IS CONTINUING TO GROW IN OUR ENGAGEMENT AND EVENTS WITH A 50% JUMP AT OUR 2019 TOKYO DAY TO 360 REGISTERED ATTENDEES.

# NORTH AMERICA

NORTH AMERICA. INDUSTRY ADOPTION HAS TAKEN OFF WITH MILLIONS OF CORES SHIPPING FROM NVIDIA, WESTERN DIGITAL, SIFIVE, AND OTHERS.

# PAKISTAN

ON THE ROAD TO DECLARING RISC-V THEIR NATIONAL ARCHITECTURE, TWO OF THE BIGGEST GATHERINGS EVER OF 3000+ IN PAKISTAN FOR TWO SIFIVE TECH SYMPOSIUMS – OCT 2019

#### More than 435 RISC-V Members across 33 Countries Around the World

450 44 Chip **25 Software** 400 SoC, IP, FPGA Dev tools, firmware, OS 350 300 24 Industry **9 //O** 250 Memory, network, storage cloud, mobile, HPC, ML, automotive 200 150 **31 Services** 32 Research 100 Fab, design services Universities, Labs, other alliances 50 200+ Individual RISC-V developers and advocates 0 Q2 03  $\bigcirc 4$ Q3 Q4 2015 2015 2016 2016 2016 2016 2017 2017 2017 2017 2017 2018 2018 2018 2018 2019 2019 2019 2019 2019 December 2019

Gcc, binutils, glibc, Linux, BSD, LLVM, QEMU, FreeRTOS, ZephyrOS, LiteOS, SylixOS, ...

#### **Proprietary software:**

Lauterbach, Segger, IAR, Micrium, ExpressLogic, Ashling, Imperas, AntMicro, ...

**Software**

ISA specification Golden Model

Compliance

#### Hardware

...

RIS

**Open-source cores:** Rocket, BOOM, RI5CY, Ariane, PicoRV32, Piccolo, SCR1, Swerv, Hummingbird,

International

#### **Proprietary core providers:**

Alibaba, Andes, Bluespec, Cloudbear, Codasip, Cortus, InCore, Nuclei, SiFive, Syntacore, ...

Inhouse cores: Nvidia, WDC, Alibaba, +others

# What's Different about RISC-V?

- Far smaller than other commercial ISAs

- Clean-slate design

- Clear separation between user and privileged ISA

- Avoids µarchitecture or technology-dependent features

- Modular ISA designed for extensibility/specialization

- Small standard base ISA, with multiple standard extensions

- Sparse &variable-length instruction encoding for vast opcode space

- Stable

- Base and first standard extensions are frozen

- Additions via optional extensions, not new versions

- Community designed

- Developed with leading industry/academic experts and software developers

#### Engaged engineers are domain experts Drive technical priorities in 20+ focus areas

Opcode Space Mgmt Standing Committee V Extension (Vector Ops) Task Group Software Standing Committee Cryptographic Extension Task Group Base ISA Ratification Task Group Debug Specification Task Group Privileged ISA Spec Task Group Fast Interrupts Spec Task Group Memory Model Spec Task Group UNIX-Class Platform Spec Task Group Processor Trace Spec Task Group Formal Specification Task Group Compliance Task Group Trusted Execution Env Spec Task Group B Extension (Bit Manipulation) Task Group J Extension (Dynam. Translated Lang) Task Group P Extension (Packed-SIMD Inst) Task Group

+ Security Committee, HPC Special interest group, soft-core SIG, and Safety Task Group

ORG

PATTERSO

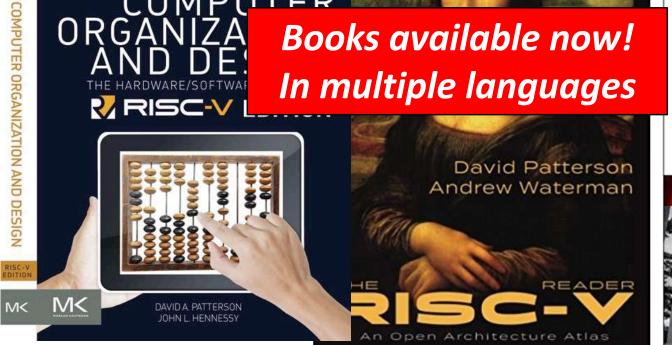

# **RISC-V** in Education

**Books available now!**

**RISC-V** spreading quickly throughout curricula of top schools

COMPLITER

John L. Hennessy | David A. Patterson

21

#### omputer ARCHITECTURE

A Quantitative Approach 17. 3124 M<

- Engineers sometimes "don't see forest for the trees"

- The movement is *not* happening because some benchmark ran 10% faster, or some implementation was 30% lower power

- The movement *is* happening because *new business model* changes everything

- Pick ISA first, then pick vendor or build own core

- Add your own extension without getting permission

- Implementation features/PPA will follow

- Whatever is broken/missing in RISC-V will get fixed

# **Modest RISC-V Project Goal**

# Become the industry-standard ISA for all computing devices

- RISC-V originally designed for research into application-specific processors

- Small base, sufficient to run full C compiler and software stack

- Provides minimal "skeleton" on which to hang domain-specific extensions

- No "permission" needed to build your own extension

### **RISC-V Vector Extension (RVV) Overview**

|                  | v31[0] | v31[1] | v31[VLMAX-1] |

|------------------|--------|--------|--------------|

| <u>32 vector</u> |        |        |              |

| <u>registers</u> |        |        |              |

|                  | v1[0]  | v1[1]  | v1[VLMAX-1]  |

|                  | v0[0]  | v0[1]  | v0[VLMAX-1]  |

Maximum vector length (VLMAX) depends on implementation, number of vector registers used, and type of each element.

- Unit-stride, strided, scatter-gather, structure load/store instructions

- Rich set of integer, fixed-point, and floating-point instructions

- Vector-vector, vector-scalar, and vector-immediate instructions

- Multiple vector registers can be combined to form longer vectors to reduce instruction bandwidth or support mixed-precision operations (e.g., 16b\*16b->32b multiply-accumulate)

- Designed for extension with custom datatypes and widths

Vector CSRs

#### vtype

*Vtype sets width of element in each vector register (e.g., 16-bit, 32-bit, ...)*

vI

Vector length CSR sets number of elements active in each instruction

#### vstart

Resumption element after trap

vcsr (vxrm/vxsat)

Fixed-point rounding mode and saturation flag fields in vector CSR

# **Some RVV Design Points**

| Name         | lssue<br>Policy | lssue<br>Width | VLEN<br>(bits) | Datapath<br>(bits) | VLEN/Datapath<br>(beats) |

|--------------|-----------------|----------------|----------------|--------------------|--------------------------|

| Smallest     | InO             | 1              | 32             | 32                 | 1                        |

| Simple       | InO             | 1              | 512            | 128                | 4                        |

| InO-Spatial  | InO             | 2              | 128            | 128                | 1                        |

| OoO-Spatial  | 000             | 2-3            | 128            | 128                | 1                        |

| OoO-Temporal | 000             | 2-3            | 512            | 128                | 4                        |

| OoO-Server   | 000             | 3-6            | 2048           | 512                | 4                        |

| OoO-HPC      | 000             | 3-6            | 16384          | 2048               | 8                        |

# **RISC-V Encoding Terminology**

Standard: defined by the Foundation

Reserved: Foundation might eventually use this space for future standard extensions

Custom: Space for implementer-specific extensions, never claimed by Foundation

# **RISC-V Custom Extension Example**

| Standard RV32IMAFD<br>Software |   |   |   | FD |          | Custom<br>SW<br>Libraries |        |

|--------------------------------|---|---|---|----|----------|---------------------------|--------|

| Base<br>RV32I                  | М | A | F | D  | Reserved | Custom                    | Custom |

# **Fragmentation versus Diversity**

#### **Fragmentation:** Same thing done different ways

#### **Diversity:** Solving different problems

Two powerful forces keep fragmentation at bay:

- Users: No one wants a repeat of vendor lock-in.

- Software: No one, not even nation state, can afford their own software stack. Upstream open-source projects only accept frozen/ratified Foundation standards.

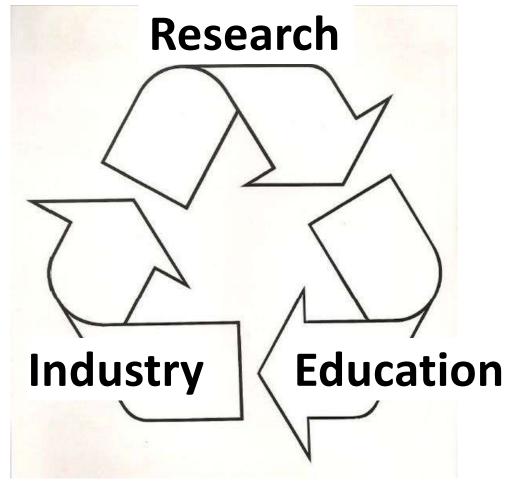

Open ecosystem is key to keeping the virtuous cycle going