2025年12月4日木曜日 9:00-18:00 日本標準時 (UTC+9)

2025年12月4日木曜日 9:00-18:00 日本標準時 (UTC+9)

ここをクリックすると無償参加登録できます。

時間 | 講演タイトル | 講演者 BIO |

9:30-17:45 | 司会 | 小檜山 智久(こひやま ともひさ) | 一般社団法人 組込みシステム技術協会(JASA)RISC-V WG主査 | 株式会社 日立産機システム インフラシステム統括本部 主管技師 |

開会挨拶:「RISC-Vを取り巻く研究とイノベーション」

| 池田 誠(いけだ まこと))| 東京大学 大学院工学系研究科 電気系工学専攻教授 | |

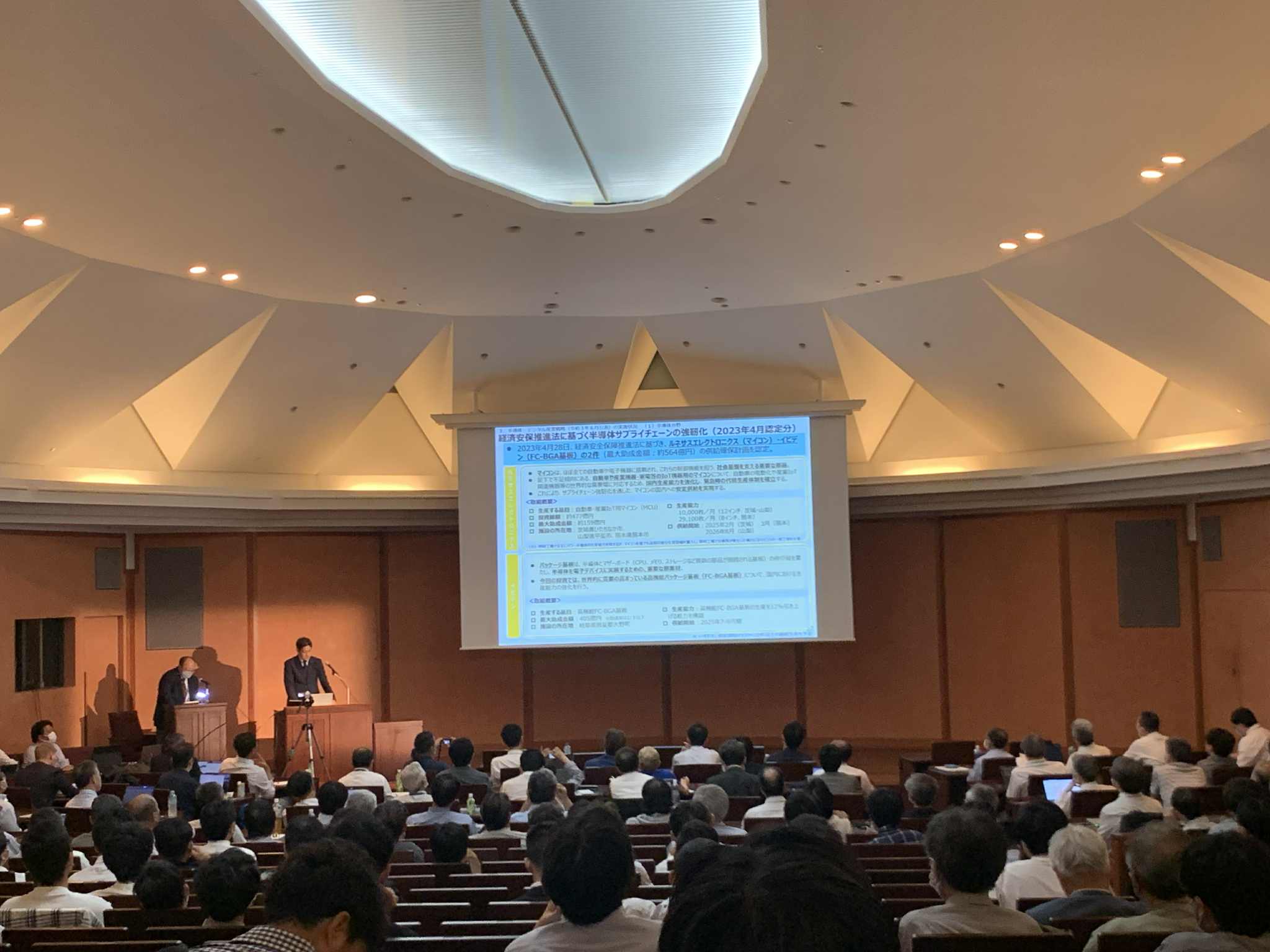

10:00-10:20 | 我が国の半導体・デジタル産業戦略について | 齋藤 尚史(さいとう ひさし)| 経済産業省 商務情報政策局 情報産業課 総括補佐 博士(工学) 技術開発と産業振興を統合的に推進する姿勢で、日本の半導体・電子産業の再興に取り組んでいる。民間企業において約10年にわたり半導体の研究開発に従事し、製造およびプロセス技術の分野で豊富な実績を持つ。2021年に経済産業省へ入省し、以降は半導体・デジタル産業戦略の策定や、国内外の製造拠点誘致、半導体技術開発支援など、日本の半導体産業政策の中核を担っている。 |

Alphawave Semi の高性能コネクティビティ IPとチップ統合技術 | スー・ホン・フォン(Sue Hung Fung)|Alphawave Semi IP事業部 プロダクト ライン マネージャー | |

11:00-11:30

| チャットボットからロボットへ エッジにおけるフィジカルAIは、自律型プラットフォームの新市場を切り開き、高い運用効率を達成する。フィジカルAIを実装するために不可欠な「Sense(認識)」「Think(推論・判断)」「Act(動作)」「Communicate(通信)」という中核技術を考察する。エッジ領域における次のフィジカルAIイノベーションを牽引し、自律化のスーパサイクルに参入するために必要な技術進化の方向性を解説する。 | チョル・キム(Cheol Kim)|MIPS Technologies プロダクトマーケティング ディレクター エッジAI、IoT、組込み、自動車、通信インフラ市場において豊富な経験を持つテクノロジーリーダーである。ハーバード・ビジネススクール(エグゼクティブMBA)、テンプル大学(MBA)、オレゴン大学(理学士)、明治学院大学(文学士)を修了。Intel、ThunderSoft、Schleuniger Global、Rimnet、LG などで、30年以上にわたり多様な技術分野で活躍。 |

| セキュリティ 101 ― Root of Trust と RISC-V TEE の概観 RISC-Vをベースとして開発されているTEE(Keystone, CoVEなど)やRoot of Trust(Titan, Caliptraなど)の技術について概観する。これらの技術はハードウェアで機能を開発するのみではなく、活用するソフトウェアも信頼できる必要があり、Remote Attestationを通じた外部からの検証も必要となる。既に商用のTEEとしてはArm TrustZone, Intel SGX, TDX, AMD SEV-SNPなど、Root of TrustとしてはAMD Secure Processor (AMD-SP)が出ているがそれらとの比較も行う。 | 須崎 有康 (すざき くにやす)|情報セキュリティ大学院大学 教授 1991年 東京農工大学大学院博士後期課程中退。同年、通商産業省工業技術院電子技術総合研究所に入所。1997-8年 オーストラリア国立大学の客員研究員。2001年 改組により国立研究開発法人産業技術総合研究所。2001年 イリノイ大学アーバナ・シャンペーン校の客員研究員。2009年 東京大学より博士(情報理工学)。2022年9月より本学教授。情報処理学会、電子情報通信学会、IEEE各会員。2010年IPA日本OSS貢献者賞。 | |

| CaliptraおよびOpenTitanチュートリアル ― オープンRoot of Trustファームウェアのアーキテクチャと統合(GoogleおよびMicrosoftにおける最新動向) 本チュートリアルでは、Google・Microsoft・AMD・NVIDIA が主導し、Nuvoton・Samsung・Intel などの半導体企業が支援する Open Compute Project(OCP) 傘下のオープン Root of Trust(RoT)プロジェクトである Caliptra を中心に、さらに Google が主導し、現在 Nuvoton により量産化されている独立型 RoT チップ・イニシアチブ OpenTitan にも焦点を当てるものである。Caliptra は、ファームウェア、プロビジョニング、Linux 統合を含む SoC 組込み型スタック として設計されているのに対し、OpenTitan は スタンドアロン型のセキュリティチップ を提供することを目的としている。すなわち、OpenTitan が透過性の高い 独立型 RoT 実装 を体現するのに対し、Caliptra は クラウドおよびデータセンターシステム向けの統合型 RoT ソリューションの標準化 を目指している。本セッションでは、両プロジェクトの 設計思想、セキュアブート機構、および オープンソース開発による信頼性向上へのアプローチ を探るものである。 | アンドレス・ラガル=カビーヤ | 特別主席エンジニア | グーグル LLC (Google LLC)米国、カリフォルニア州 マウンテンビュー グーグルの特別主席エンジニアとして、オープンハードウェアセキュリティとコンフィデンシャルコンピューティングの領域を牽している。オープン・コンピュート・プロジェクト(OCP)では、グーグルを代表する主要な技術リーダーの一人。Open Compute Security Project(OCSP)およびData Center Secure Control Module(DC-SCM)仕様の方向性を策定している。オープンサーバーアーキテクチャにおける一貫したRoot of Trust(信頼の基点)、セキュアブート、および認証フレームワークの実装を定義している。グーグル社内では、DC-SCMによるハードウェアレベルのセキュリティから、上位層のHSM(ハードウェアセキュリティモジュール)サービスやコンフィデンシャルコンピューティング環境に至るまで、プラットフォームレベルの信頼メカニズムを統合し、稼働中データ(data in use)の完全な検証可能保護を実現している。ラガー=カヴィーヤ氏のリーダーシップの下、グーグルの内部インフラストラクチャとOCPエコシステムは、透明性・相互運用性・暗号的検証可能性を備えた新たなセキュリティ基盤へと前進している。オープンスタンダードと実運用規模のシステムを橋渡しすることで、同氏は現代のデータセンターにおける「設計による信頼(trust by design)」のあり方を再定義し続けている。 | |

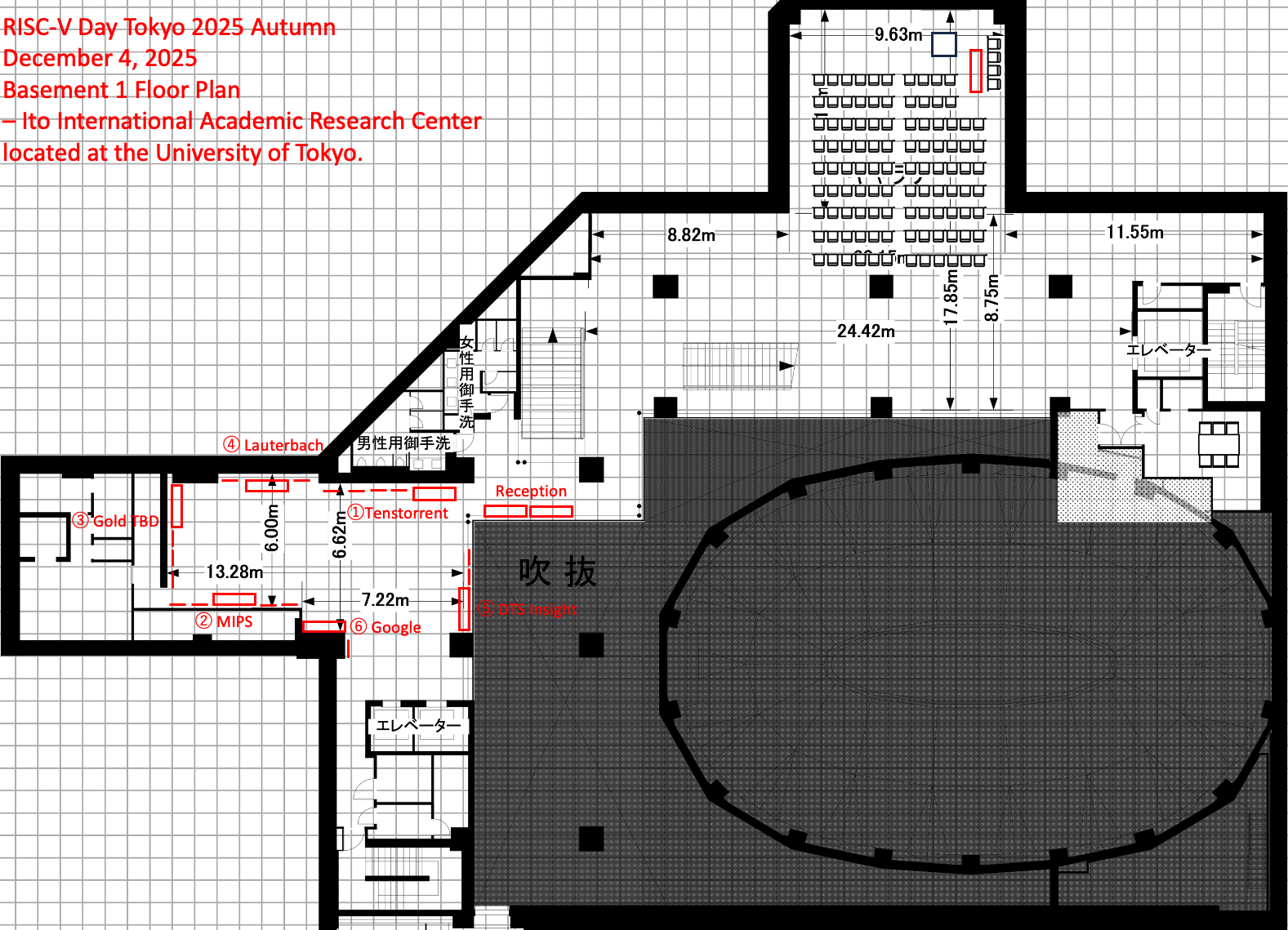

12:40-14:00 | ランチタイム | 展示エリアオープン |

| オープンコンピュートによるスケーリング:RISC-V、チップレット、AI・ロボティクスの未来 RISC-V アーキテクチャとチップレット技術が、Tenstorrent による AI、自動車、ロボティクスなど多様な市場向けの幅広いコンピューティングプラットフォーム開発をどのように可能にしているかを解説する。チップレットを用いたコンポーザブルシステムの構築に伴う課題についても取り上げる。近年、UCIe をはじめとするチップレット構築技術は大きく進歩しているが、異なるベンダー間のチップレットで相互運用性を実現するうえで、依然として大きなギャップが存在する。本講演では、異なるベンダーのチップレットを統合する際に発生する主要なインターオペラビリティ(相互運用性)問題を明らかにし、Tenstorrent がこれらの障壁を克服するために取り組んでいるソリューションを紹介する | 石井 靖夫(Yasuo Ishii)|RISC-V CPU アーキテクチャ フェロー|Tenstorrent Japan 次世代RISC-V CPU のマイクロアーキテクチャ設計、フロントエンド最適化、性能探索のリードを務めるプロセッサアーキテクチャの専門家である。CPU フロントエンド、ブランチ予測、命令フェッチ、キャッシュ、データプリフェッチングなど、高性能プロセッサ設計に関する広範な知識と20年近い実務経験を有する。2023年に Tenstorrent に参画する以前は、Arm において 8 年以上勤務し、Senior Principal Engineerとして CPU マイクロアーキテクチャ、フロントエンドロジック設計、性能探索を担当した。Arm 在籍中は、主に命令フェッチ、ブランチ予測、スケジューリングなど、先端CPUの中核技術を牽引した。Tenstorrent および Arm 以前は、日本の NEC にて 8年以上にわたりハードウェアエンジニアとして CPU ロジック設計に従事した。指令キャッシュ、デコード、スケジューリング、プリフェッチング、メモリディスアンビギュエーションなど、汎用CPUの主要フロントエンド技術を幅広く開発した経験を持つ。 | |

14:40-15:10 ビデオ | 実運用に耐えるエージェントAIループの設計 ― ロボティクスを視野に入れた実システム信頼性を担保する実践的AIフレームワーク エージェント型AIシステム(Agentic AI Systems)とは、推論・計画・ツール呼び出し・結果評価・反復処理を自律的に行い、目標達成まで閉ループで動作するプログラムである。しかし、このようなシステムを実運用レベルに仕上げるためには、レイテンシ・コスト・プライバシー・信頼性といった複数の側面にわたる工学的規律が求められる。本講演では、大規模にエージェントAIループを設計・展開するための実践的フレームワークを提示する。特に、ReAct(Reason + Act)パラダイムが堅牢なツールベースエージェントやマルチエージェント協調をいかに実現するかを解説し、ツールルーティングポリシー、コンテキスト圧縮、オンデバイス検索技術など、プライバシーと性能の両立を支える手法に焦点を当てる。また、クラウドベースAIの応答性やデータ保護に限界が見え始める中、RISC-Vベースおよびチップレット駆動型プラットフォームがローカル自律性の新たな地平を開いていることを論じる。これにより、知的エージェントはエッジデバイスやロボティクスシステム上で直接推論・学習・動作することが可能となる。参加者は、クラウド・エッジ・ロボティクス領域を横断して持続可能かつ自己改善型のAIエージェントを構築するためのエンジニアリング設計指針と運用上の枠組みを得るとともに、RISC-Vのようなオープンハードウェアが次世代のスケーラブルで信頼性の高いAIインフラをいかに支えるかについての洞察を得ることができる。 | チラーグ・アグラワル(Chirag Agrawal)| Alexa+ AIエージェントエンジニアリング部 シニアソフトウェアエンジニア | アマゾン・ドットコム社(Amazon.com, Inc.)(米国ワシントン州シアトル) チラグ・アグラワル氏は、アマゾンにおいて次世代会話型AIシステム(例:Alexa+)の基盤技術の設計と開発に貢献してきたエンジニアである。Alexa+とは、アマゾンが開発を進める大規模言語モデル(LLM)と複数のAIエージェントを統合した次世代音声アシスタント基盤であり、アグラワル氏はその中核となる会話メモリ基盤およびRAG(Retrieval-Augmented Generation)型Bring-Your-Own-Content(BYOC)パイプラインを構築した。これらは、ユーザや企業が独自データを活用して生成AIと対話できる仕組みであり、アマゾンのマルチエージェント推論アーキテクチャを支える重要なインフラである。同氏の研究領域は、リアルタイム文脈圧縮、プロンプト最適化、検索拡張型対話フレームワークなど多岐にわたり、大規模AIエージェントのレイテンシ・信頼性・スケーラビリティを大幅に向上させている。現在は、クラウド依存から脱し、RISC-Vベースおよびチップレット駆動型プラットフォーム上でAIが自律的に推論・学習・動作するアーキテクチャを追求している。これは、スケーラブルでプライバシー重視、かつ自己改善可能なAIインフラをクラウドとエッジの双方にまたがって構築するというビジョンに基づくものである。アグラワル氏は、InfoQや国際的なAIエンジニアリング系ポッドキャストにおいて、持続可能なエージェント型AIシステムの実践的設計フレームワークに関する知見で注目を集めている。 |

| RISC-V CPUチップ評価の実践と再現性検証 — FPGA・Google Open MPW、TinyTapeoutによるJASA独自RISC-Vオープンプラットフォーム開発とGithub公開 JASA RISC-V WG では、RISC-V オープン規格に基づく 再利用可能な RISC-V プラットフォーム を構築し実装力強化を目指している。開発は段階的に進められ、各ステージで動作デモを実現してきた。2022 年からは FPGA を用いた 64bit Linux ブートの実証 を行い、RISC-V 実装の基礎技術を習得した。2024 年から、① MCU、② ルートオブトラスト、③ ネットワーク IPなどのチップ開発ロードマップ をOpenROAD に代表されるオープン EDA、PDK、IPを活用し開発することにした。2022年にGoogle シャトル MPW-6、7、8 にテープアウトした試作チップを活用し、ソフトウェア評価、動作確認、テスト手順の標準化を行い、成果として得られた IP と検証ログを GitHub で全面公開 した。Github再現性向上のため、凍結済み SiFive Freedom 系リポジトリの復元、依存関係の整理、Docker 化、ツールチェーンのバージョン固定など、実務的な課題にも直面した。2025 年度に入り、eFabless 社の活動休止を受け、JASA1 MCU の論理設計を単純化して TinyTapeout で実装可能な構成へと再設計するニーズが生じた。TinyTapeout には搭載可能な論理規模に厳しい制約があるため、従来の 5 ステージ RISC パイプライン構成では収まらない。そこで、TinyTapeout 向けに CPU をステートマシン型へ再設計し、論理量を 1/4 に削減した。そのうえでFreeRTOS が動作可能な RISC-V MCU を実現した。現在 FPGA 上で動作検証を行なっているが、テープアウトを行う。 | 小檜山 智久(こひやま ともひさ) | 一般社団法人 組込みシステム技術協会(JASA)RISC-V WG主査 | 株式会社 日立産機システム インフラシステム統括本部 主管技師 | |

16:00-16:20 ビデオ | オープンコンピュートによるスケーリング:日本の取り組みと半導体設計エンジニア育成プログラム(上級コース) Tenstorrentの国内における研究開発状況に加え、Ip, AI Chip、サーバ製品などの取り組み、自動車向けSoc,ロボイクス向けの取り組み、さらに現在3期の募集開始を控えている人材育成プログラム 上級コースについて説明する。 | 中野 守(なかの まもる)| テンストレント・ジャパン株式会社 代表取締役社長 |

16:20-16:40 | 休憩 | 展示は開いています。 |

オープンアーキテクチャ・ライトニングトーク ① | ① 中島 伸盛 | 株式会社 日立産業制御ソリューションズ(HiICS) デジタル基盤ソリューション本部 セミコンダクタ第一設計部 | |

オープンアーキテクチャ・ライトニングトーク ② | ② 明石 貴昭 | Country Manager – Japan, Codasip GmbH(ドイツ) | |

17:10-17:20 | オープンアーキテクチャ・ライトニングトーク ③ | ③ 今村 謙之 (いまむら のりつな) | ISHI会 (略称: ISHI会) / OpenSUSE |

RISC-V Day 2025 Autumn 閉会挨拶 | 天野 英晴 | 東京大学大学院工学系研究科附属 システムデザイン研究センター 上席研究員 先端設計研究部門 基盤設計研究部門 |

| Time | Presentation Title | Speaker |

| 『自前チップ設計試作』講座:OpenROAD と Tiny Tapeout ワークフロー オープンソースEDAツール OpenROAD と教育プラットフォーム TinyTapeout を用い、LSI設計からチップ製造までの基本的なワークフローを実践的に学ぶ。参加者は、設計自動化・物理実装・検証の各プロセスを対話的に体験しながら、オープンソースハードウェア設計の基礎を身につける。本チュートリアルは、SkyWater 130nm(Sky130)プロセスをベースに、Verilogによるデジタル回路設計、OpenLANE, xschem, ngspice, KLayout などのオープンEDAツールを用いた設計から、GitHub Actionsによる自動GDSII生成までを一貫して解説する。さらに、TinyTapeoutシャトルへの提出を通じて、オープンソースツールとコミュニティ主導の設計プラットフォームが、ASIC製造をどのように身近なものにしているかを体感できる。このセッションの目的は、参加者にオープンソースハードウェア設計手法の実践的理解を提供し、TinyTapeoutエコシステムの教育的可能性を体験してもらうことである。3時間のハンズオンでチップ設計手法を実践的に学べます。PCを持参し、会場でオープンEDAツールのDockerイメージをインストールします。WindowsはWSL(Ubuntu 24.04推奨)、Macは最新Dockerを事前に導入ください。ハンズオン後は関連講演と展示を実施。 | 今村 謙之 (いまむら のりつな) | ISHI会 (略称: ISHI会) / OpenSUSE |

無償配布図書

本書の第一の目的は、オープンソース技術を半導体設計に適用し、ムーア則減速後の半導体業界を再度活性化しようとする米国国防省「国防高等研究計画局」DARPAが Google に委託して開発した「オープンロード」(Open ROAD = Open Realization of Advanced Designs)とRISC-V 運動を解説することである。

本書の第二の目的は、アジア各地域の政府が、米国で RISC-V のオープンソース潮流に触発され、半導体産業に参画することにより地域経済の発展を考えることを始めている様子を解説することである。インドは RISC-V を「国家アーキテクチャ」とし、2 人の元インテルの幹部を大臣にし半導体産業を興そうとしている。中国はRISC-V を活用して米国の輸出規制を自力で乗り越えようとしている。インド、ベトナム、タイ、インドネシアなどの国々も、DARPA + Google の技術を背景とし、少ない予算で国家半導体プロジェク トをスタートしようとしています。

本書の第三の目的は、次世代半導体の核となるロジック半導体の実相について解説することである。現在の水平分業化された半導体サプライチェーンを構成する、台湾の TSMC、 英国の Arm などの年次報告などの公表データを定点観測的に独自調査し、20年以上のトレンドを明らかにした。

RISC-V International 提携アナリストの数値も使い、データを可視化した。

本書の第四の目的は、データセンター用のAIアクセラレータについて解説することである。2022年11月30日に一般公開された自然言語学習推論エンジンであるChatGPTは、NvidiaのGPUに支えられている。AIの深層学習や自然言語処理には膨大な電力が必要となるため、電力需要が増大する中で、Nvidiaを凌駕しようと、データセンター用AIチップの消費電力削減に挑むスタートアップ企業を解説する。

題名:『Google半導体とRISC-Vと世界の電子地政学 RISC-V Day Tokyo 2023 Summer版』

単行本: 304ページ(147×209ミリ) 定価(本体1818円+税)

編集者:田胡 治之

発売日:2023年6月20日 第一版第1刷 発行

販売方法:主要書店、通販サイト

発行: 株式会社ソハコ

発行者: 河崎 俊平

発行: 株式会社ソハコ

書籍コード:ISBN 978-4-911019-00-9

分野コード:C0034

定価:(本体1818円+税)

分野:テクノロジー CPU

分類:B2-53 ハードウエア開発 コンピュータアーキテクチャ B8-02 深層学習 ディープラーニング

JANコード:192-0034-01818-7