▶ 発表(口頭/ポスター)応募はこちら【無料】

▶ スポンサー発表および展示募集

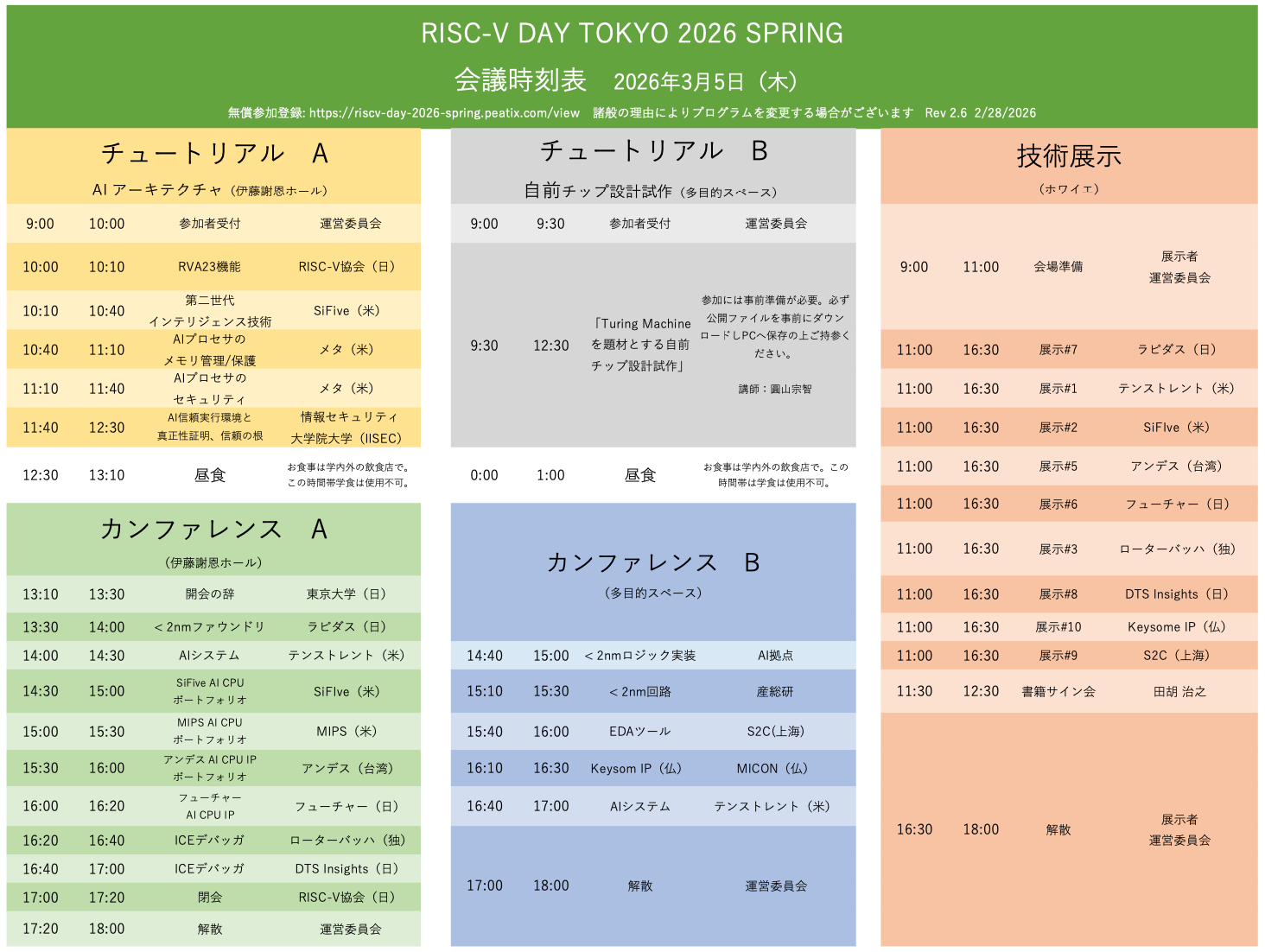

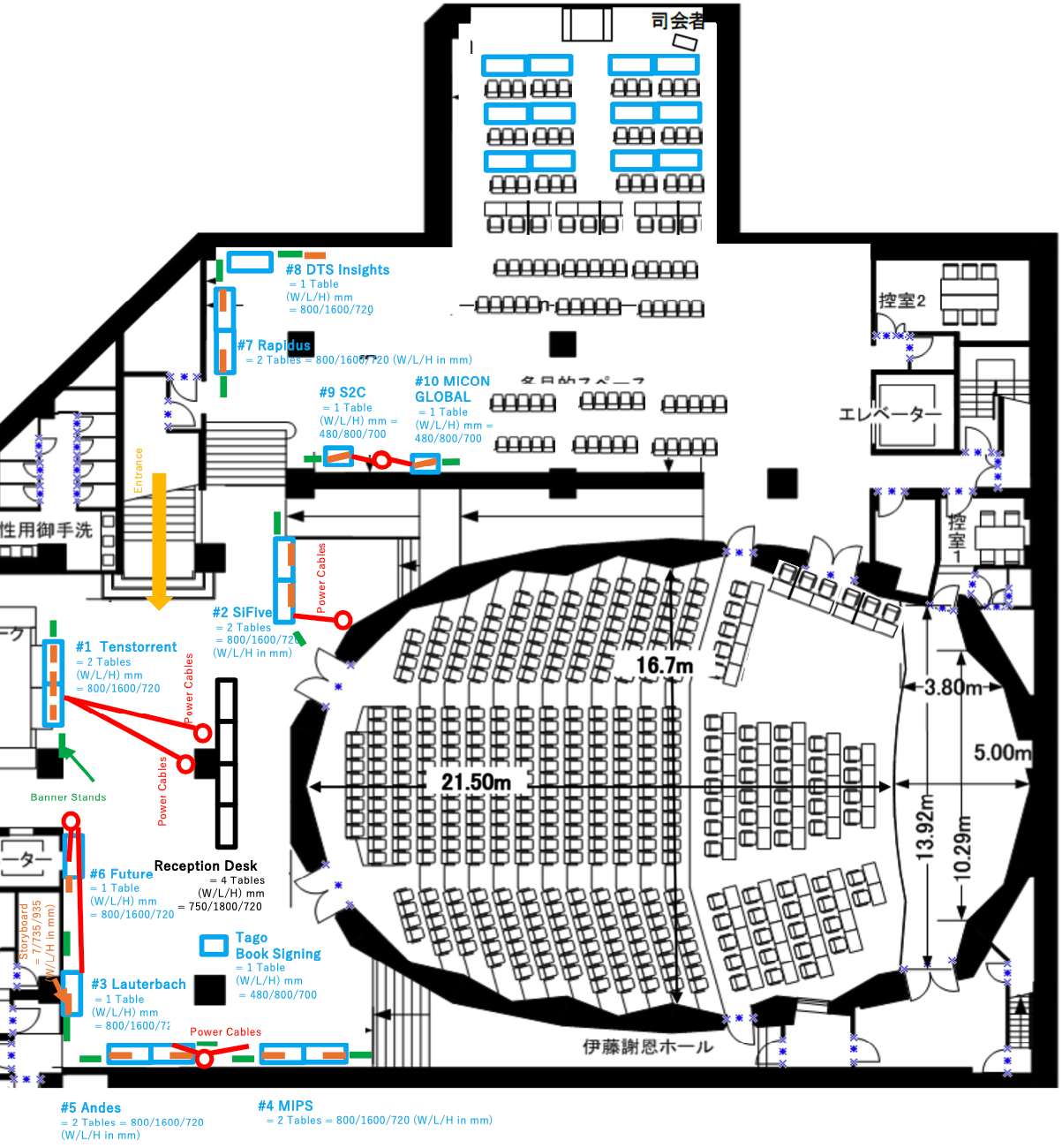

カンファレンスA @伊藤ホール(発表者写真はクリックで拡大)

時間 | 発表題目 | 発表者 |

開会の辞(Welcome Remarks) | 開会の辞(Welcome Remarks) | |

Rapidusにおける2nmプロセス向け標準セルライブラリー開発と設計基盤整備 | 鶴崎 宏亀 | ラピダス株式会社 エンジニアリングセンター 設計技術統括部 ディレクター | |

オープンコンピュートが拓くAIの未来:チップレット、スケーラブルAI、AI開発 | 中野 守(なかの まもる)| テンストレント・ジャパン株式会社 代表取締役社長 | |

SiFive 第2世代 Intelligence ファミリーの紹介 | 近藤 芳人 | 代表取締役社長, サイファイブ ジャパン(本社:米国) | |

RISC-Vを用いたフィジカルAIプラットフォーム設計におけるソフトウェア主導型知能 | 片山 卓也(かたやま たくや) | ソフトウェア・ツール分野テクニカルマーケティング担当, MIPS(米) | |

Andes RISC-Vによる次世代コンピューティングの推進 | フランクウェル・リン | 会長兼最高経営責任者 | アンデス テクノロジーズ(台湾) | |

RISC-Vを活用したカスタムAIアクセラレータ開発事例 | 宮下 悠希(Yuki Miyashita)| フューチャー株式会社 ki-labs | FPGAリード | |

RISC-Vのデバッグ&トレースソリューションTRACE32 | 毛利 裕二 | 日本ローターバッハ株式会社(ドイツ)代表取締役 | |

16:40-17:00 | RISC-V開発を支えるICEデバッグ環境:実機開発で必要なツールと現場課題 | DTSインサイト株式会社(英語表記:DTS INSIGHT Corporation) |

閉会の辞:RISC-Vを活用した我が国のデジタル分野の復興について | 中條 拓伯 | 国立大学法人 東京農工大学大学院 工学研究院 准教授 |

カンファレンス B

| 時間 写真 | 講座題目 | 発表者 |

AIDCにおける先端半導体設計環境の整備と進行中プロジェクト | 内山 邦男 | 国立研究開発法人 産業技術総合研究所(AIST)AIチップ設計ラボ ラボ長(招聘上級研究員) | |

15:10-15:30 | 産総研の先端半導体研究開発の取り組みについて | 昌原 明職(まさはら めいしょく)博士 | 国立研究開発法人 産業技術総合研究所(AIST) |

ハイブリッド・コ・エミュレーションとシフトレフト手法によるRISC-V開発の加速。S2C EDAソリューションは、統合検証エコシステムを提供している。このプラットフォームは、初期段階のマイクロアーキテクチャ解析や仮想モデリングを行うGenesis Architect、スケーラブルなシステム統合とコンプライアンス・テストを担うOmniArkエミュレーション、そして高性能なソフトウェア開発とハードウェア評価のためのProdigy FPGAプロトタイピングという3つの主要な柱に基づいています。本スイートの極めて重要な技術コンポーネントは、QEMUやSystemCのような非RTL仮想モデルとRTLハードウェア設計を同期させるハイブリッド・コ・エミュレーション・ブリッジである。タイミング情報を持たないソフトウェア・トランザクションのためのプロキシ、それらをサイクル精度のハードウェアイベントに変換するトランザクタ、およびシームレスなデータフローを保証する専用通信チャネルで構成される高度なインターフェースによって実現されている。高レベルなアーキテクチャ探索と物理プロトタイピングの間の溝を埋めることで、この技術は最終的なシリコンが製造される前に、開発者がソフトウェアの早期成熟と厳格な認証を達成することを可能にする。 | S2C EDA(上海) | |

正確な仕様を実現するRISC-VおよびアクセラレータIPでイノベーションを加速する | ルカ・テスタ(Luca TESTA)博士 – 共同創設者 兼 COO | Keysom Inc. | |

TenstorrentにおけるRISC-VベースCPUチップレットの開発と性能評価

| 木村 優之(Masayuki Kimura) | シニアスタッフエンジニア | Tenstorrent Japan |

チュートリアル A

| 時間 写真 | 講座題目 | 発表者 |

AI処理を「アーキテクチャ」で高速化 | 河崎 俊平 | 代表理事、一般社団法人RISC-V協会 | |

10:10-10:40 | SiFive第2世代インテリジェンス技術解説 | ジョン・シンプソン(John Simpson)| SiFive Inc. シニア・プリンシパル・アーキテクト |

10:40-11:10 | 招待講演:「RISC-VサーバSoC仕様」(Server SoC Specification) | ヴェドヴィヤス・シャンボーグ(Vedvyas Shanbhogue)| RISC-V命令セット セキュリティ・水平技術委員会 副議長 | コンフィデンシャル・コンピューティングSIG/TG 議長(RISC-Vインターナショナル)| 米メタ(旧Facebook)半導体エンジニア |

11:10-11:40 | 招待講演:AI・クラウド時代の信頼基盤 ― RISC-V 秘匿計算で安全な大規模データ分析を実現 | ラビ サヒタ(Ravi Sahita)| セキュリティエンジニア | 米メタ(旧Facebook) | RVIセキュリティ・水平技術委員会 副議長、コンフィデンシャル・コンピューティングSIG/TG 議長(RISC-V International) |

11:40-12:30 | TEE (Trusted Execution Environment) + Attestation + RoT (Root of Trust) on RISC-V | 須崎有康 (Kuniyasu Suzaki) 情報セキュリティ大学院大学 教授 |

チュートリアル B

| 時間 写真 | 講座題目 | 発表者 |

『Turing Machine を題材とする自前チップ設計試作』講座: | 圓山 宗智(まるやま むねとも) 注)受講者は、以下を習得する:(1) チューリングマシンのアーキテクチャとその RTL 設計 (2) OpenROAD / LibreLane を用いた論理合成・自動配置配線・タイミング解析・DRC/LVS 検証・Tiny Tapeout に提出可能な レイアウトデータGDSII の生成プロセス (3) オープンソースEDAとオープンPDKを活用した「自前チップ試作」の実際当日は、個人 PC(x64 Windows 11 + WSL2)を持参していただき、会場にてWSL イメージを導入して作業を進める。 |

ハーバード大学・歴史科学機器コレクション「Go Ask Alice」展(2012年)に展示されたチューリング・マシン実機モデル。抽象計算モデルであるチューリング・マシンの動作原理を可視化するために制作された教育用展示装置。

写真提供:GabrielF/Wikimedia Commons(CC BY-SA 3.0)

アラン・チューリング(1911-1954)写真提供:Elliott & Fry(1951年撮影)出典:Wikimedia Commons(File:Alan Turing (1951) (crop).jpg)Public Domain

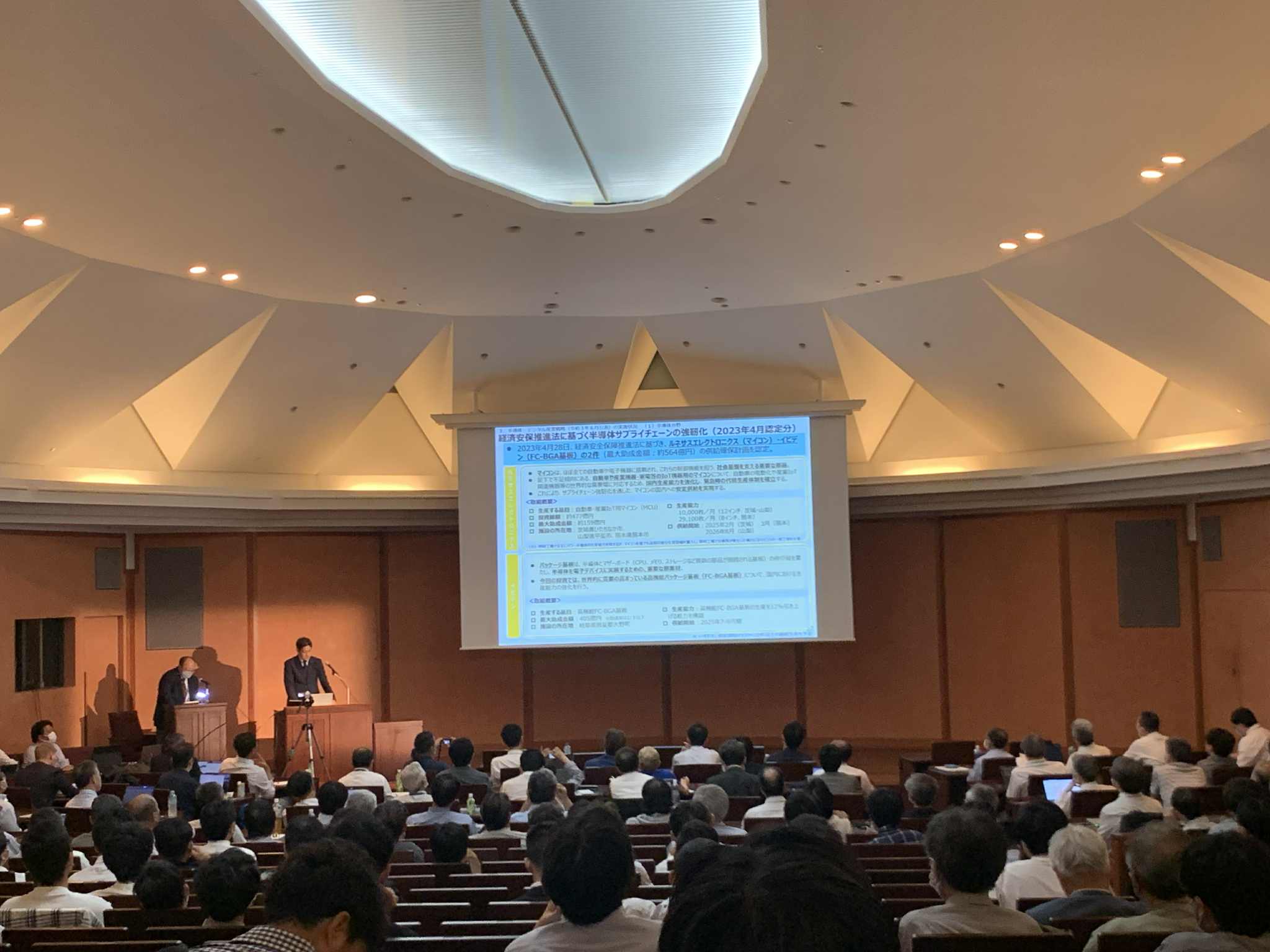

過去のRISC-V Dayからの映像