出典:クリスエドワーズ

2021年6月3日

https://www.newelectronics.co.uk/content/features/democratising-chip-design

3nmプロセスノードが生産準備に近づくにつれ、そのためのチップ開発のコストはさらに一段高くなりました。

チップ設計を民主化する動きが高まっています。それは、プロとアマチュアの両方のエンジニアのより広いコミュニティにそれをもたらすことです。これは不可能な作業のように思われるかもしれませんが、徐々にアクセスしやすくなるにつれて、ムーブメントははるかに古いテクノロジーに取り組んでいます。

大量のチップに関するムーアの法則ほど劇的ではありませんが、シリコンの学習曲線は、成熟したプロセス、特にマスク作成などの初期費用に対しても機能します。導入時に、180nmプロセス用のフルマスクセットは簡単に30万ドルの費用がかかり、130nmで50万ドル以上になりました。今日の状況はまったく異なります。 Global Semiconductor Associationの業界調査によると、過去2年間で、180nmマスクセットの価格は60,000ドル以下であり、130nmセットの場合は80,000ドルを下回ることがよくありました。

成熟したプロセスのマスクの価格が下がる前でさえ、ASICプロトタイピングや少量生産への低コストの方法の1つは、ファウンドリTSMCが好む名前を使用するマルチプロジェクトウェーハ(MPW)または「シャトル」にありました。これは、ほとんどの商用集積回路(IC)のサイズと、リソグラフィツールがウェーハの表面にフィーチャを印刷するために使用するレチクルの面積との差を利用しています。あなたは600平方ミリメートルを測定するかもしれないレチクルで10から平方ミリメートルをとる多くのデザインを得ることができます。一方、受け取ることを選択できるチップの数は数十に制限されている場合がありますが、プロジェクトを外部資金提供がオプションになるまでには十分な可能性があります。

マスクセットは、唯一の先行エンジニアリングコストからはほど遠いです。ツールとIPは、ハイエンドで数百万に達する可能性のある設計に不可欠です。資金不足の設計者にとっての1つの選択肢は、Siemens Digital Industries Software and IPが販売しているTannerスイートなどの低コストのツールにあります。たとえば、Armは今月初めにDesignStartプログラムを再調整し、製造後のロイヤルティだけで、前払いのライセンス料を要求することなく、マイクロコントローラー指向のコアの選択へのアクセスを提供しました。

他のアクティビティは、Eclipseなどのプロジェクトを使用したソフトウェア開発の多くの部分で起こったことを反映しています。オープンソースツールを中心とした設計環境を構築します。多くのチップ設計チームは、モデリング言語SystemCとPythonプログラミング言語を介してすでにオープンソースを使用しています。Pythonプログラミング言語は、RTL検証で使用されるテストハーネスの制御に適しています。

オープンソースイニシアチブ

潜在的に重要なイニシアチブは、より包括的なオープンソース設計ツールのセットを構築することを目的とした、米国の研究機関DARPAのOpenRoadイニシアチブです。カリフォルニア大学サンディエゴ校のAndrew Kahng教授とこのプロジェクトの主任研究員は、機械学習と彼が「極端なパーティショニング」と呼んでいるものを組み合わせることで、さまざまなチップ設計を自動的にレイアウトおよび調整できる環境を構想しています。多くの小さな独立して最適化されたモジュールにチップします。

検証エンジニアはさまざまな形式のオープンソースを採用していますが、その採用の障害は、テープアウトに近づくほど大きくなります。最大の問題は、秘密保持契約によって嫉妬深く保護され、共有を禁止しているファウンドリによって提供されるプロセス設計キット(PDK)にあります。

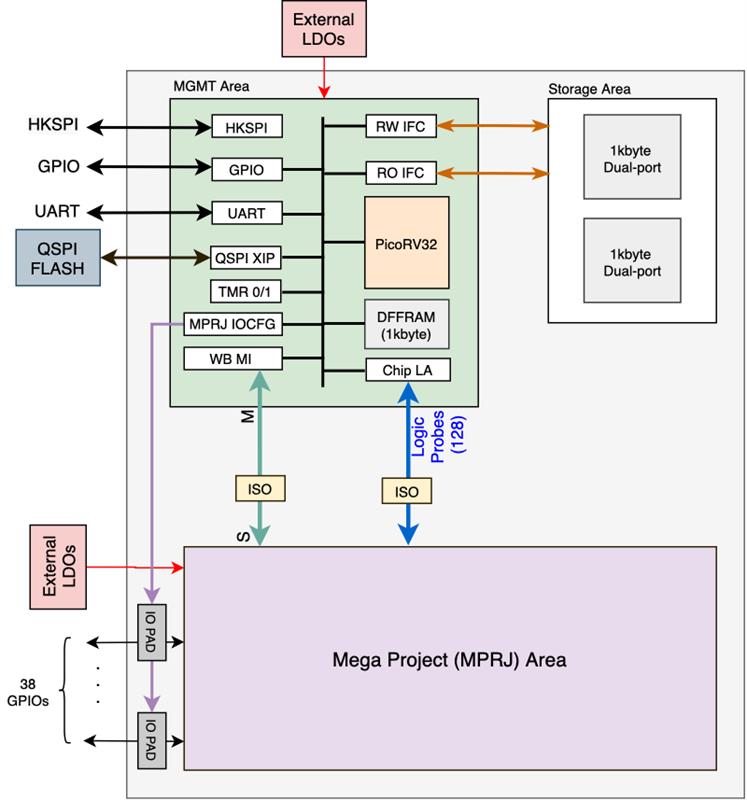

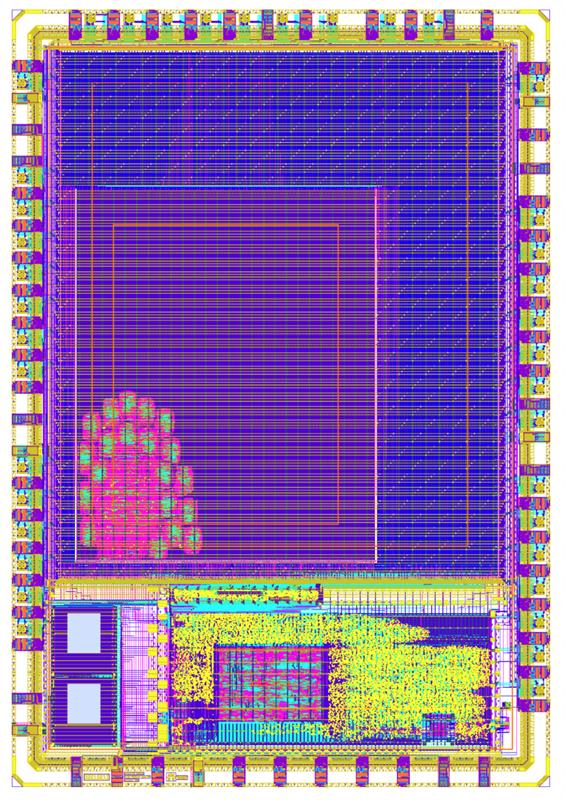

上と下の図:Antmicroによって開発されたCaravelテストインフラストラクチャは、組み込みのRISC-Vコアによって管理されるI/Oとテストポートのリングを提供します

IEEEのSolid-StateCircuitsSocietyが主催するセミナーでの問題の例として、GoogleのソフトウェアエンジニアであるTim Ansellは、オープンな市場を確立しようとしている新興企業であるEfablessが開発したRavennaRISC-Vマイクロコントローラーを指摘しました。ソースIPとシリコン。マイクロコントローラーはX-FabのXH018プロセスで作成されましたが、ファウンドリのPDKとアナログIPを使用する物理的なレイアウトを除いてオープンソース設計です。

「Efablessは完全に再利用可能な結果をリリースできませんでした」とAnsell氏は述べています。 「私のような人は、ゲートに何かがどのように実装されているかを見ることができませんでした。この業界には、共有に関して問題のある態度があります。」

アンセル氏によると、グーグルは一般的に進歩を加速させることに基づいて知識を共有する能力に熱心だという。 「ムーアの法則により、計算に対する需要の高まりに対応するために、新しい革新的なソリューションが必要になります」と彼は付け加えます。

より広いコミュニティにシリコン設計へのアクセスを提供することは、従来の研究開発では実現する可能性が低い、新しい計算方法を作成するための手段を提供する可能性があります。それを前進させるために、AnsellはファウンドリにPDKを開くよう説得しようとし始めました。 「私はファウンドリがたくさん。そして、私は多くの鋳造所に笑われました。」

あるファウンドリがこのアイデアに思いつきました。数年前まで、ミネソタ州でサイプレスセミコンダクターが所有していたファブを運営している会社であるスカイウォーターです。 「私たちは、オープンソースライセンスの下で130nmPDKをリリースすることを許可する合意に達することができました」とAnsell氏は言います。 Githubからダウンロード可能なPDKはApache2.0ライセンスを使用しており、「私の許可を求めたり、Skywaterの許可を求めたりすることなく、すべてのユーザーがクローンを作成できます。オープンソースのPDKは、完全にオープンソースのASICを使用できることを意味します。」

次に、GoogleとeFablessは、ASIC設計の可能性を、ファブから何かを取り戻すために何万ドルもかからない人々に拡張するMPWサービスの構築に着手しました。無料チップの資格を得るには、設計者は自分の設計をオープンソースにするだけでなく、設計とその結果得られるシリコンの操作に関心のあるユーザーにサンプルを提供する準備をする必要があります。 「デザインはGDSに至るまでオープンソースでなければなりません」とAnsell氏は言います。

シャトルは約100のサンプルを返します。これは、ユーザーが要求に応じて他のユーザーにシリコンを提供することを心配せず、オープンソースハードウェアの共有の可能性を提供しようとするのに十分な数であるとAnsellは見なしています。 「オープンソースにより、人々は簡単にコラボレーションできます。これにより、人々は以前はリスクが高すぎると思っていたものを試すことができます。失敗するのは簡単で安価であり、失敗から学ぶことができます。」

制約

さらなる制約は、Antmicroによって開発されたCaravelテストインフラストラクチャを使用するための要件です。これにより、組み込みのRISC-Vコアによって管理されるI/Oおよびテストポートのリングが提供されます。 「最初にテストチップを構築する場合は、このようなものが必要です」と、EfablessのCTO兼共同創設者のMohammed Kassem氏は述べています。このI/Oリングの真ん中には、ユーザーのカスタムシリコン用の10平方ミリメートルの穴があり、支払いなしで何にでも使用できます。

面積は比較的小さいですが、130nmで150万以上のゲートを供給できるため、複雑なデジタル設計が実現可能であるとAnsell氏は言います。 「人々は古いノードのデジタル機能を非常に過小評価しています。なぜなら、それらは最近、低電力およびアナログ設計をターゲットにするために主に使用されているからです」と彼は述べています。

スカイウォーターでの130nmプロセスでの最初の実行の提出は2020年11月に終了し、2回目の提出は6月中旬に終了し、その2回目の実行からプロジェクト所有者に12月初旬に部品が納品されます。 Googleは近い将来6つのシャトルに資金を提供しています。 Efablessは、完全にオープンソースのハードウェアルートにコミットしたくない設計チームに有料のMPWも提供しています。

最初のシャトルには、IBMやQuicklogicなどの企業の設計が含まれていました。

「しかし、最もエキサイティングなことは、設計者の60%がこれまでASICを使用したことがないということでした」とAnsell氏は言います。 「SkyWaterプログラムの成功は、オープンソリューションに対する大きな需要が存在することを示しており、現在、他のファウンドリからの初期の関心があります。」

高度なノードでの作業は設計コストをさらに高くしますが、結果として得られるチップが生産に入ると潜在的に莫大な見返りがありますが、設計の民主化の最先端での作業は、業界の進歩を推進するためにも同様に重要であることがわかります。

サーキュレーション

©Copyright2022Mark Allen Group |イギリスで登録番号02120366