Thursday, February 27, 2025

9:00-18:00 Japan Standard Time JST (UTC+9)

Click Here to Register for the Event

(Abstract Deadline February 17, 2025 Poster Deadline February 19)

| Contents Categories |

| ① RISC-V Solutions |

| ② Special Sessions:Japan’s Semiconductor Strategy 2024 and RISC-V | AI |

| ③ RISC-V Lunch Meetings |

| ④ RISC-V Technical Exhibits |

| ⑤ RISC-V Research and Open Semiconductors |

| ⑥ AI、RISC-V Research Poster Session |

The RISC-V Day Tokyo conference is the largest RISC-V event in Japan. The RISC-V Day Tokyo 2025 Spring conference will be held on Thursday, February 27, 2025 from 9:00-18:00 JST (UTC+9) at the Ito International Research Center, The University of Tokyo. We will bring together excellent RISC-V-related technologies and products, as well as key people and engineers, and provide business opportunities such as increasing product awareness, realizing collaboration between companies, technology exchange, and information gathering. We look forward to your participation on this occasion! A video of the presentation and information on materials will be posted on the website at a later date.

① RISC-V Solutions

② Special: Japan’s Semiconductor Strategy 2025

February 27, 2025 Time: 9:00-18:00

| Time | du-ra-tion | Lang | Presentation Topic | Presenter | Organization | pres-en-ta-tion |

|---|---|---|---|---|---|

9:00- | 30 min | – | Attendees can enter 2nd basement floor and hall. Reception staffs hands out name tags. | Staff sets up recording equipment, audio, and video systems, exhibition booths. | |

| 9:50- 10:00 | 30 min | JE | Welcome Remarks | Hideharu Amano | University of Tokyo | |

| 10:00- 10:35 | 30 min | E | Title: Beyond Innovation: RISC-V’s Path to Mass Adoption with Mature IP Abstract: In the AI hardware market, Tenstorrent is expanding its team and shipping products by targeting development engineers and customers in the early phase of development by providing a low-cost RISC-V-based development system and an open source AI compiler stack. The company recently completed a $693 million Series D round of funding and was selected as one of the top 10 companies in the AI industry. By avoiding expensive components such as high-bandwidth memory and adopting a tensor processor architecture, the company reduces the need for memory bandwidth and achieves cost performance. The company has already secured $150 million in revenue and is aiming for organic growth by focusing on small customers seeking differentiated technology. CEO Jim Keller points out that AI has the potential to significantly transform computing technology over the next 10 years. He says that the collaborative work of hardware, software, and open source will play an important role. He believes that the key to success is to create outstanding products that are centered on use cases, like Steve Jobs. Amid the tense US-China relationship, the company is showing its willingness to respond flexibly to geopolitical changes while adhering to trade regulation rules. (The title and abstract were prepared by the organizer and will be changed as soon as the abstract is prepared by the presenter.) | Wei-Han Lien | Lead CPU Architect, Tenstorrent (USA) | |

10:35– | 30 min | J | Title: RISC-V Leadership in the AI Compute Era Abstract: SiFive’s momentum continues, and the company has recently added to its broad portfolio from embedded solutions to advanced scalar and vector high performance processors. We will introduce our latest products and discuss how our roadmap is driving customers’ rapid innovations in areas like AI, data centers, automotive and the Internet of Things. | Yoshihito Kondo | CEO, SiFive Japan (USA) | |

| 11:10-11:35 | 20 min | TBD | Title: Autonomous platforms driven by MIPS multi-threaded, safety-capable, efficient RISC-V compute solutions Abstract: The drive for generative AI to evolve into physical automotive and industrial applications is pushing software-defined platforms toward zonal architectures. New compute subsystems that excel at fast data processing and precise real-time control with low latency and high efficiency are needed to address the challenges of electrification, autonomous vehicles, and industrial automation. This presentation will describe how safety-capable processor cores with multi-threading, deterministic access, RISC-V profile compatibility, and application-focused performance enhancements for data movement and memory operations are the leading choice to power the next generation of industrial robots, autonomous platforms, and electrified vehicles. | Cheol Kim | Director of Product Marketing, MIPS (USA) | |

11:35– | 10 | – | Break time | ||

11:45-12:10 | 20 min | E | Title: Optimizing Data Transport Architectures in RISC–V SoCs for AI/ML Applications Abstract: This presentation will illustrate the challenges and solutions of data–transport architectures for artificial intelligence/machine learning (AI/ML) in the context of embedded vision architectures and discuss implementation aspects for Networks–on–Chips (NoCs) for RISC–V–based System–on–Chips (SoCs). AI/ML and Embedded Vision architectures present unique challenges in data transport architectures to procure all relevant data from off–chip DRAMs and efficiently store and transport them in caches to allow efficient computing on SoCs and systems of chiplets. These challenges directly translate into specific requirements for NoC implementation, impacting performance, power consumption, and cost, efficiently addressing the challenges posed by what the industry calls the “memory wall” – the much faster improvement of processor vs. DRAM memory access speed. In addition, for the automotive and industrial application domains, special considerations regarding safety and resilience need to be considered to allow for ISO26262 and related certifications. Arteris, Inc. is a technology company headquartered at Campbell, California. The company specializes in the development of network-on-chip (NoC) interconnect IP and system-on-chip (SoC) integrated automation software that are used in a variety of devices, particularly in automotive electronics, artificial intelligence/machine learning, and consumer markets. Their flagship product, FlexNoC, has been integrated into over 3 billion devices as of 2022. Additionally, Arteris offers products like Ncore, a cache-coherent interconnect IP, and CodaCache, a last-level cache IP. (Title and abstract will be prepared by the organizer and will be changed as soon as the presenter’s abstract is ready.) | Michal Siwinski | Arteris (USA) | |

12:10-12:45 | 30 min | E | Title: Introducing ARC-V Processor IP, Optimized Implementations of the RISC-V ISA Abstract: Synopsys ARC-V Processor IP is based on the RISC-V ISA. The ARC-V processor family includes the ARC-V RMX, an ultra-low power, control and signal processing-optimized processor for embedded applications; the ARC-V RHX, a 32-bit real-time multi-core processor with coherent hardware accelerator and virtualization support; and the 64 bit “ARC-V RPX” for SoC host applications. The RPX family includes L3 cache and a RISC-V compliant MMU and supports rich operating systems such as Linux. Synopsys’ ARC-V FS processors meet the ASIL-D level of ISO 26262 (functional safety standard) and are developed based on an ISO 9001 certified quality management system. These processors have integrated hardware safety features to detect system errors and ensure safety. In addition, it is compliant with ISO 21434 (Automotive Cyber Security Standard). Synopsys’ “MetaWare Development Toolkit” is provided to assist with program development, debugging, and optimization. ARC-V licensees can leverage Synopsys’ “ARC Access” partners and the tools and software of the growing RISC-V ecosystem to shorten development schedules and bring products to market faster. | Satoshi Tanabe, Staff Application Engineer, IP Group | Synopsys (USA) | Video |

12:45-13:00 | 15 min | Introduction of Poster Session Presenters: Participants in the poster session will be awarded prizes. Presenters will be asked to take to the stage in the hall. | Hironori Nakajo | Professor, Department of Intelligent Information Systems Engineering, Tokyo University of Agriculture and Technology (Japan) | Video | |

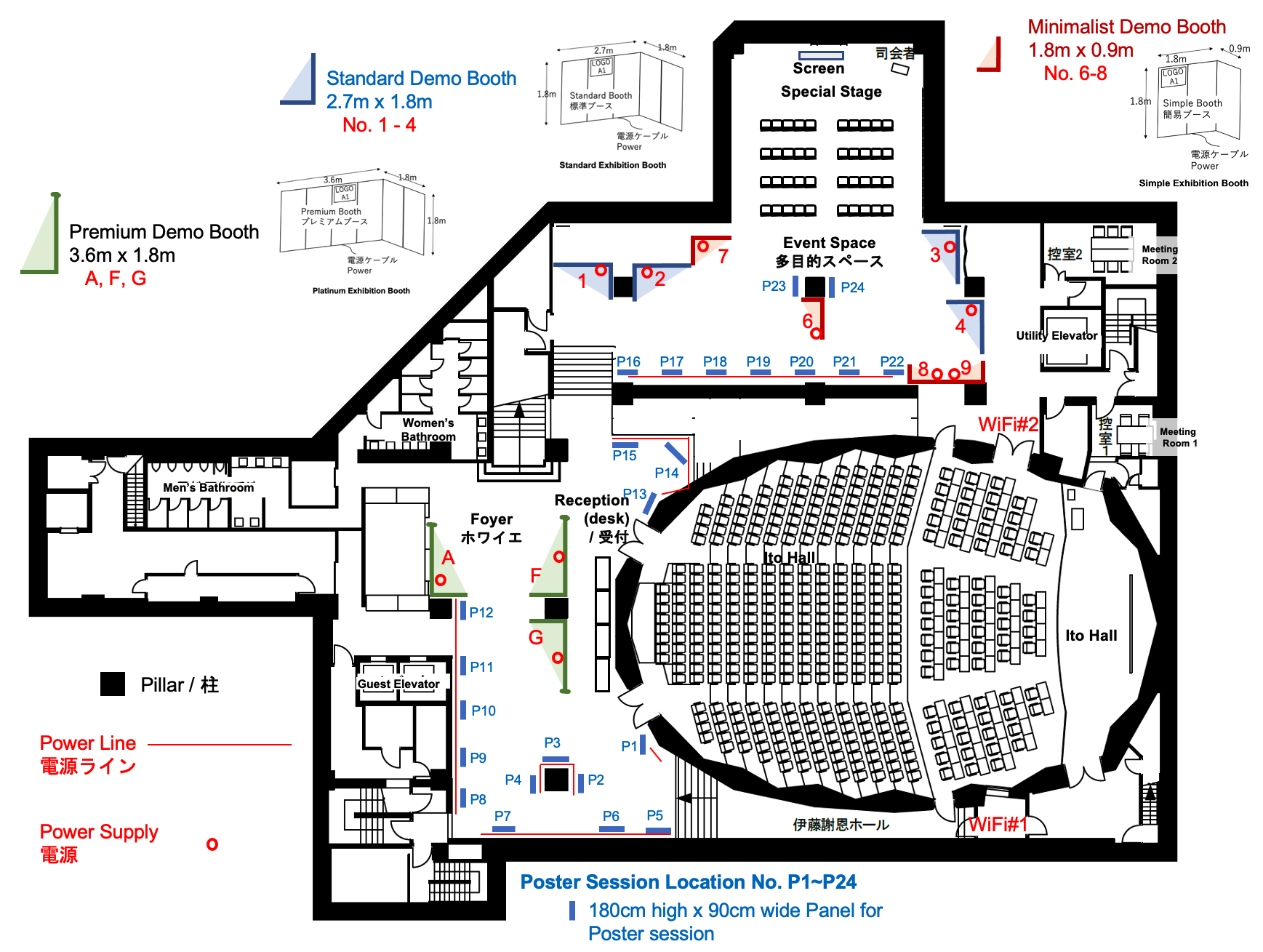

13:00-15:30 | 150 min | Poster presentation takes place at the south foyer of Ito Hall, B2. Please refer to the floor plan maps and look for poster panel locations P1 through P10. | Poster Presenters | ||

13:00-14:00 | 60 min | – | {Lunchtime}: RISC-V Lunch Networking Session | Staff will provide a simple lunch. If staff does not reach you, please collect your lunch pack at the reception. | |

14:00-14:35 | 30 min | E | Transforming Modern Computing With RISC-V Abstract: RISC-V has rapidly gained traction across a wide range of applications. For example, Andes customers span sectors such as AI/ML for Cloud and Edge, Automotive, 5G/Networking, MCU/MPU, Multimedia, Storage, Sensor Processing, Wearables, and Wireless Connectivity, with AI/ML from edge to cloud being particularly prominent. As the RISC-V ecosystem matures for Linux and Android, there is a growing demand to use RISC-V cores as primary CPUs in personal computing devices and servers. These advancements position RISC-V to significantly enhance its market presence in the computing industry in the coming years. | Charlie Hong-Men Su 蘇泓萌 | CTO and President, Andes Technology | |

14:35-15:00 | 30 min | Title: Advanced MCU MD6605 for power electronics control, utilizing a RISC-V CPU core, 22nm ultra-low leakage process, and ReRAM non-volatile memory technology Abstract: Sanken Electric is a semiconductor manufacturer whose main products are power electronics control devices. Recently, Sanken had developed the MD6605, an MCU (Microcontroller Unit) for power electronics control, which utilizes a RISC-V CPU core, 22nm ultra-low leakage process, and ReRAM non-volatile memory technology for advanced power control systems. | Takanaga Yamazaki | Sanken Electric, Senior Meister, Power Device Development Division, Technology Development Headquarters (Japan) | ||

15:00-15:30 | 30 min | {Intermission} Demo Booths are Open |

| ||

15:30-16:10 | 30分 | The Future of RISC-V Development Paved by Kubuds: Cross Toolchain and Optimization Technology Abstract: Kubuds provides comprehensive software toolchains and full-stack solutions for embedded systems and PCs to support the development of the RISC-V ecosystem. The company’s strengths lie in the creation of highly efficient development environments using the latest cross-compilation tools (GCC, LLVM), in addition to open source real-time operating systems (RTOS) and optimization for Linux. In providing cross-compilation toolchains, the company has established an environment where developers can seamlessly build and run applications across different platforms, and it can be widely applied from embedded systems to PCs. In addition, the company is also focusing on the development of debugging environments, providing advanced debugging functions using tools such as GDB and OpenOCD to improve development productivity. In terms of support for integrated development environments (IDEs), the company has achieved smooth integration into mainstream IDEs such as VS Code and Eclipse, and has established an environment where developers can develop and optimize RISC-V-based applications while maintaining their existing workflow. This makes it possible to accommodate a wide range of developers, from beginners to experienced engineers. Performance optimization for RISC-V-based embedded devices provides tuning for specific applications and designs that emphasize power efficiency, and we are working to develop advanced development environments for IoT devices and industrial equipment. (The title and abstract will be created by the organizer and will be changed as soon as the abstract is prepared by the presenter.) | Wei Wu | Shanghai Kubuds Technology Co., Ltd. | ||

| 16:10-16:20 | 10 min | E | Poster session review and award winners announcement: Participants in the poster session will be awarded. Prize winners will be selected and awarded for their excellent presentations. | Hironori Nakajo | Professor, Department of Intelligent Information Systems Engineering, Tokyo University of Agriculture and Technology (Japan) | |

16:20-16:50 | 20 min | J | Japan’s Semiconductor and Digital Industrial Strategy: Semiconductors are a key technology for Japan’s future in terms of digital transformation (DX) and green transformation (GX). The Ministry of Economy, Trade and Industry has responded to domestic and international technological innovations and market trends based on the “Semiconductor and Digital Industry Strategy” formulated in 2021. In June 2023, in the face of increasing geopolitical risks and the importance of economic security, the strategy was revised to focus on strengthening the semiconductor supply chain, expanding the domestic manufacturing base, and developing human resources. In this presentation, we will explain the updates based on the contents of the Semiconductor and Digital Industry Strategy Review Meeting held last December. | Hisashi Saito | Deputy Director, IT industry division, Commerce and Information Policy Bureau, Ministry Economy, Trade and Industry | Video |

16:50-17:00 | 10 min | J | Next-generation semiconductor engineer training program in collaboration with d.lab at the University of Tokyo and Tenstorrent Abstract: The System Design Research Center (d.lab) at the University of Tokyo is collaborating with Tenstorrent, a US AI chip startup, to train semiconductor engineers. As part of the Technology Research Association’s Leading Semiconductor Technology Center (LSTC), this initiative will see Japanese engineers dispatched to Tenstorrent in 2024 to work on designing semiconductors for AI. The expected dispatch period is one to two years, and after returning to Japan, they are expected to play an active role in telecommunications and automotive-related companies and research institutes. The program aims to train 200 engineers over five years. d.lab will lead the University of Tokyo’s inter-departmental education program “Semiconductor Education Program (SPIRIT)” from April 2024, and is working to produce human resources with a wide range of semiconductor knowledge. This aims to train human resources who can take on design using advanced devices. (Title and abstract will be prepared by the organizer and will be changed as soon as the presenter’s abstract is ready.) | Makoto Ikeda | The University of Tokyo (Japan) | Video |

17:00-17:10 | 10 min | J | Introduction to Tenstorrent’s Advanced Digital SoC Design Training Program / Advanced Course: Abstract: Under the NEDO “Post-5G Information and Communication System Infrastructure Enhancement R&D Project / Human Resource Development / Advanced Digital SoC Design Training”, Tenstorrent USA, Inc. has been selected, in collaboration with the Leading-edge Semiconductor Technology Center (LSTC), to participate in the project. As part of this initiative, Tenstorrent will conduct an advanced semiconductor design training course focused on single-nanometer semiconductor design. The program will primarily involve On-the-Job Training (OJT) in Silicon Valley, providing practical experience in cutting-edge semiconductor design. In this session, we will introduce Tenstorrent’s company profile, an overview of our RISC-V CPU and AI accelerators, and provide details about the human resource development project. | Mamoru Nakano | President & CEO, Tenstorrent Japan Inc. (USA) | Video |

17:10-17:20 | 10 min | J | Value of RISC-V That Empowers ISO26262 Certified Chip Abstract: In SHD Group 2024 survey report, RISC-V based SoC shipping quantity was forecasted to be higher than 16B pieces in 2030, in same survey Andes was ranked as the leading RISC-V IP vendor with more than 30% market share. In reviewing Andes own statistics analysis, automotive application is in high growth for recent three years, its importance is growing. Andes had long preparation period to get whole company ISO26262 ASIL-D certified in 2020 with its robust functional safety RISC-V processor IP development and quality assurance flow. In this speech, presenter will showcase Andes’ functional safety RISC-V processor certified with ISO26262 ASIL-B and ASIL-D, customers successful story, and roadmap for coming years. As automotive application is in high growing stage nowadays, applying RISC-V in validating various automotive standard specification for new generation vehicles, new energy vehicles are also trend of automotive industry. ISO26262 certified RISC-V processor IP can been seen as a key to turn on value proposition of SoC design. | Frankwell Jyh-Ming Lin | CEO and Chairman, Andes Technology (Taiwan) | |

17:20-17:30 | 10 min | J | RISC-V Day Tokyo 2025 Autumn Information | Shumpei Kawasaki | Chairman, RISC-V Alliance Japan (Japan) | Video |

| 17:30-18:00 | 30 min | J | Withdrawal |

| – |

③ RISC-V Lunch

The bento supplier will be closing down at the end of February this year. If you have a favorite bento, please take note of its four-digit number. We will make sure boxes are clearly identified.

2376 Yamabuki – A bento featuring teriyaki chicken and seasonal simmered dishes.

2377 Inari Assortment – A light meal bento with inari sushi and simmered side dishes.

2375 Takamori – A popular bento featuring maitake mushroom rice from Takamori and fried chicken, highlighting the natural flavors of the ingredients.

2374 Tomato Burger & Vegetable Deli – A colorful bento with a tomato-flavored hamburger steak and a selection of vegetable deli dishes.

2237 Grilled Salted Salmon & Chikuwa Tempura – A bento featuring a popular combination of grilled fish and fried side dishes.

2373 Maruyama – A bento with rich, fatty grilled fish and seasonal simmered dishes.

2371 Two-Color Soboro Bento – A soboro rice bento with seasoned ground chicken and a refreshing spring rain salad, offering a perfect flavor balance.

Thank you to the bento vendor for your long-standing service. Bento plans for Summer 2025 have not yet been decided.

④ RISC-V RISC-V Technology Exhibition

February 27, 2025 11:00-16:30

B2F Foyer, multipurpose space

Please note that exhibitors and content are subject to change.

| ブース番号 | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| A | 11:00-16:30 | New CPU cores will be announced and updated, and details of enhanced versions of existing vector processors such as NX27V and NX45 MPV, as well as new out-of-order application processors (X66/X67) will be introduced. Examples of AI/ML, HPC, and 5G/6G communications utilizing the latest technology for vector extensions (RVV) may be shown. In-vehicle solutions and enhanced security will also be important themes. Andes offers processors certified by ISO 26262, and enhanced functional safety (FuSa) support and new IP for the automotive market may be exhibited. In addition, the company will mention the progress of RISC-V support in Android and Linux environments, highlighting the strengthening of its ecosystem. In addition, it is expected to exhibit unique AI/ML optimization examples using custom instructions (ACE: Andes Custom Extension), secure boot, and TEE (Trusted Execution Environment). The development tools and ecosystem will also be emphasized. As with SiFive, enhanced IDEs (integrated development environments), compiler optimizations, and simulators for developers may be announced. In addition, new evaluation boards and examples of joint development with partner companies will be exhibited, showing that Andes’ RISC-V solutions are being put to practical use in a variety of fields. (The above is an explanation from the organizers) | Andes Technology (Taiwan) | |

F | 11:00-16:30 | RISC-V Innovations: New CPU Cores, AI Enhancements, and Ecosystem Expansion Overview: This exhibition will introduce a diverse product lineup centered on RISC-V-based processor IP, as well as the latest CPU cores and roadmaps. Pay particular attention to updates to high-performance cores and the latest trends in vector expansion support for AI and DSP. Efforts in large-scale systems, such as functional safety support for automotive applications and multi-core configurations for servers and HPC, will be shown. The exhibition will also cover the evolution of development tools and software stacks. Integrated development environments (IDEs), Linux/Android support, security features, and new evaluation development boards will also be exhibited. SiFive is expected to strengthen the ecosystem in these fields and promote the spread of the RISC-V architecture. (The above is the organizer’s explanation.) | SiFive | |

| G | 11:00-16:30 | Tenstorrent Latest AI Hardware Showcase Overview: At the Tenstorrent exhibition booth, we will showcase our latest AI hardware and solutions. A MacBook Air and a 27-inch display will be set up for product explanations and live demonstrations, providing visitors with an interactive experience. As part of the exhibit, we will feature our AI product “QuietBox” and the PCI card “N300”, allowing attendees to witness Tenstorrent’s cutting-edge technology firsthand. Additionally, product catalogs for “Ascalon IP,” “Galaxy,” “Workstation,” and “Wormhole” will be available, offering detailed insights into each product. To further illustrate our innovations, we will display banners focusing on our CPU technology and Tensix architecture, highlighting Tenstorrent’s latest advancements and key initiatives. Our live demonstration will showcase “TT-Studio” running AI models such as “Llama” or “DeepSeek 3.1-70B”, demonstrating the power and efficiency of Tenstorrent’s AI inference capabilities in real-time. We warmly invite you to visit the Tenstorrent booth and experience the future of AI computing firsthand. | Tenstorrent |

| ブース番号 | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| 1 | 11:00-16:30 | Development environment for embedded software developers, including JTAG debuggers, compilers, and real-time OS (RTOS) development platforms | Kyoto Microcomputer Co., Ltd.(京都マイクロコンピュータ株式会社)(日本) | |

| 2 | 11:00-16:30 | Theme: DTS Insight’s Next-Generation Development Tools for RISC-V : Advanced Debugging, ICE, and IDE Solutions Overview: DTS Insight is actively involved in the development of tools and solutions for both RISC-V and Arm architectures. Their offerings include In-Circuit Emulators (ICE), Integrated Development Environments (IDE), and other development tools tailored to support engineers working with these platforms. | DTS Insight | |

| 4 | 11:00-16:30 | JASA chip pre-evaluation demo, Chisel learning VGA display | Japan Embedded Systems Technology Association (JASA) RISC-V Working Group, Technology Headquarters Hardware Committee (Japan) | |

6 | 11:00-16:30 | Open Source Semiconductor | ISHI-Kai (Japan) | |

7 | 11:00-16:30 | RISC-V CPU IP Products and Solutions: Nuclei Studio IDE, NI900 Series for AI Applications, and More | Nuclei System Technology(芯来科技)(China) | |

8 | 11:00-16:30 | RISC-V Open Source Security IP Demo | The University of Electro-Communications (Japan) |

⑤ RISC-V research and Open Silicon

February 27, 2025

The lecture name, lecture content and time are provisional and subject to change depending on the situation.

| Time | du-ra-tion | Lang | Presentation Topic | Presenter | Affiliation (click for details) | Materials |

|---|---|---|---|---|---|

13:00- | 10 min | E | Words of Welcome | Hideharu Amano | Graduate School of Information Science and Technology, The University of Tokyo | |

| 13:10- 13:40 | 20 min | E | Linux on RISC-V Software Ecosystem: Abstract: The presenter will discuss (1) The status of Fedora/CentOS on RISC-V including the repo status and software supported RISC-V dev boards (10 min) | Wei Fu (傅 煒)| Principal Software Engineer, Platform Enablement, Red Hat Software (Beijing) Co.,Ltd. | RISC-V Ambassador @ RISC-V Foundation | Video |

13:45- | 20 min | E | Technical Deep Dive: The Innovation features of RV64ILP32 Linux V3 patches Abstract: Guided by the RISC-V Profiles, the market has witnessed a surge in RVA(B) Profiles-based SoCs and CPU IPs deployed in resource-constrained environments with limited TCM, cache, and memory. Adopting the legacy LP64 ABI poses significant challenges in real-time responsiveness, performance, and cost control. Hence, we implemented RV64ILP32 Linux to help these chips’ productization. Compared to history implementations, this version gives out full functionality Linux porting. Such as support 64lp64 applications, and a lot of rv64 specific features. We would give out the demo during the presentation and welcome to join the project. | Guo Ren | Staff Engineer, linux cpu subsystem, T-Head Semi (Alibaba Group) | Linux csky Maintainer (China) | Video |

| 14:10- 14:30 | 20 min | E | OpenEuler for 2025: The Beginning of a RISC-V Server Platform Distro Abstract: The Institute of Software, Chinese Academy of Sciences (ISCAS) has demonstrated significant advancements in RISC-V ecosystem development since 2022. The OERV team led by ISCAS has achieved comprehensive support for the RISC-V architecture within the openEuler operating system, ensuring compatibility with diverse hardware platforms. In the first half of 2024, OERV reached a critical milestone by releasing the openEuler RISC-V 24.03LTS, which formally elevated RISC-V to Tier-1 architecture status within openEuler. Concurrently, through collaborations with industry partners, OERV introduced pioneering solutions, including the inaugural RISC-V-powered “RuYi Book” laptop and RISC-V ROS robotic systems, both operating on the openEuler RISC-V platform. Looking ahead to 2025, OERV will focus on aligning with the RISC-V Server Platform specification to develop standardized server systems, strategically positioning itself to address the emerging demands of the RISC-V server market. | JingWei Wang | openEuler Technical Committee & RISC-V SIG Maintainer / Engineer of ISCAS / RISC-V Advocate @ RVI | Video |

| 14:35-14:55 | 20 min | Interface of the Pulp project for RISC-V core Abstract: | Hideharu AMANO, Takuya KOJIMA | Graduate School of Information Science and Technology, The University of Tokyo, Morihiro KUGA | Department of Computer Science and Electrical Engineering, Kumamoto University, Hayate OKUHARA | Department of Electrical and Computer Engineering, National University of Singapore, and Masahiro IIDA | Department of Computer Science and Electrical Engineering, Kumamoto University (Japan) | ||

15:00-15:20 | 20 min | J | Development of a library characterizer for utilizing self-made cell libraries in open semiconductor design Abstract: Many open semiconductor designs and the open EDA and design environments that support them have been proposed, but these environments are based on the premise that circuit design will be performed using cell libraries provided by specific fabs. To load a self-created cell library into these environments, a characterizer is required, which is an EDA that characterizes the cell library by extracting its delay and power characteristics and creating a library. Here, we report on the current development status of the open source implementation of the characterizer that we are developing. | Shinichi Nishizawa | Waseda University / “ISHI-KAI “ | Video |

| 15:20– 15:30 | 10 min | E | {Intermission} Bio Break |

| – |

| 15:30-15:40 | 10 min | J | CHERI ALLIANCE 101 | Takaaki Akashi | Country Manager – Japan, Codasip GmbH (Germany) | Video |

| 15:40- 16:00 | 20 min | E | Title: CHERI alliance: embedding improved security in electronic systems Abstract: Bio: | Presentor: Dr Marno van der Maas, Principal Hardware Engineer, lowRISC C.I.C. (UK) | |

| 16:05- 16:25 | 20 min | E | Title: CHERI – Architectural memory safety and compartmentalisation full-steam ahead to commercialisation Abstract: The CHERI Task Group was formed within RISC-V International to propose extensions supporting CHERI in the RISC-V ISA. The motivation of these extensions is to enhance RISC-V with features to address memory safety issues which account for over 70% of software vulnerabilities according to Microsoft’s Security Response Center (MSRC). In this presentation, we will provide an overview of the CHERI TG’s present and future work as well as the status of the specifications of the CHERI extensions. Bio: Dr Jonathan Woodruff is a Senior Research Associate with expertise in processor architecture and microarchitecture as well as low-level software optimisation. Specialising in capability processor design, he has pushed into full-system optimisations including cache hierarchy, core timing, and multi-core designs as well as explorations into major security approaches including control flow integrity and private execution. | Dr Jonathan Woodruff | Senior Research Associate, University of Cambridge (United Kingdom) | |

| 16:30- 16:50 | 20 min | E | Title: Standardization of CHERI_RISC-V Abstract: This presentation explains the trend of CHERI RISC-V standardization work. (TBU) Bio: Tariq Kurd has over 20 years of CPU architecture, design and verification, mainly in the embedded space. I’ve worked on VLIW, multi-threaded, out-of-order cores, security and DSP style cores. I’ve been at Codasip 3+ years, and previously was at Huawei UK, Broadcom and Nvidia. Tariq was the chair of the Zfinx and Code Size Reduction Task Group of RISC-V International. | Presentator: Tariq Kurd | Distinguished Engineer and Lead IP Architect, Codasip Design Center (United Kingdom) | Video |

| 16:55- 17:15 | 20 min | E | Title: CHERI – How it works Abstract: This presentation will show how CHERI works with the Codasip X730 RISC-V Core FPGA Evaluation Kit in a storyboard format. Bio: Successfully evangelized Verilog (IEEE std. 1364-1995) at Cadence at the start of the 1990s, and SystemVerilog (IEEE std. 1800-2005) and VMM, which is the archetype of UVM at Synopsys in the early 2000s, as a member of the JEITA (formerly EIAJ) standardization committee. Involved in semiconductor design in Japan for about 30 years. Four years as Codasip’s Country Manager – Japan. | Takaaki Akashi | Country Manager – Japan, Codasip GmbH (Germany) | Video |

| 17:15- 18:00 | 45 min | E |

|

⑥ AI, RISC-V research poster presentation

February 27, 2025 10:30-15:30

B2F Foyer

Technology exhibition location: Location No. Please refer to the layout diagram for RISC-V poster exhibition (Foyer).

技術展示場所 :Location No. Please refer to the layout diagram for the RISC-V poster exhibit.

| 枠 | 発表時間 | 言語 | 出展テーマ | 発表者 | 所属機関 | ポスター | |

|---|---|---|---|---|---|---|

| P1 | 13:00-15:30 | E | SAIL-RISCV Memory Model Refactor Abstract: Sail-RISCV has been identified as the optimal model for the RISC-V ISA. However, it is important to note that the memory model of Sail-RISCV is subject to two primary limitations. Firstly, there is an absence of 34-bit physical address support in RV32, and secondly, there is ambiguity between physical and virtual memory. To address these deficiencies, a reconstruction of the Sail-RISCV memory model has been undertaken. Specifically, we employed new type constructs to distinguish physical and virtual memory, and enabled 34-bit physical address support by allowing arbitrary-width address mappings to Sail supported address types. We refined the communication mechanism with Sail’s simulated memory to accommodate arbitrary-width physical addresses, which are then mapped to corresponding Sail memory model addresses. Through experimentation, involving varying address widths, we validated the efficacy of this approach, demonstrating its correct handling of 34-bit addresses. The results of the study indicated enhanced type safety and improved model accuracy. A comparison of our implementation with alternative methods demonstrated that it offers greater flexibility, reducing the coupling risk between physical and virtual memory and providing a more precise memory abstraction for the Sail-RISCV model. For example, utilizing new type constructs ensures compile-time memory type safety. Experimental results confirmed our success in resolving type-safety concerns and extending Sail-RISCV’s support for 34-bit physical addresses. This enhancement, we believe, strengthens the accuracy of Sail-RISCV as a golden model for RISC-V. | Mingzhu Yan, Shuo Huang, Jian Guan, Yunxiang Luo | Programming Language and Compiler Technology Lab, ISCAS (China) | – | |

| P2 | 13:00-15:30 | E | RuyiSDK – A Integrated and Customizable Toolkit for RISC-V Software Development Abstract: The RISC-V instruction set’s design has given rise to a highly diverse ecosystem. However, the introduction of vendor-defined extensions has the potential to lead to fragmentation, creating challenges for developers in managing toolchains and adapting software. This paper presents RuyiSDK which is a comprehensive solution tailored for RISC-V developers. It is designed to address these challenges by integrating existing foundational software, promoting the adaptation of unsupported applications, and cultivating a vibrant developer community. RuyiSDK offers a package index that consolidates toolchains, emulators, and more, along with profile files that describe how to perform cross-platform builds, as well as software and RISC-V boards co-development. A key component of RuyiSDK is the Package Manager, which not only inherits the capabilities of traditional package managers but also incorporates advanced features such as virtual environment creation, device provisioning, and plugin support. The Package Manager transparently applies virtual environment profiles to the corresponding toolchains by reading the package index. Users only need to specify the target development board, without needing to manage toolchain differences manually. The device provisioning feature provides interactive guidance for keeping system images up to date for specific development boards, while test reports offer a certain level of quality assurance. The plugin system enables vendors and users to extend the Package Manager with custom features, thereby making it adaptable to various workflows. By providing a flexible, efficient, and transparent cross-platform development environment, RuyiSDK empowers developers to focus on innovation, thereby unlocking the full potential of RISC-V hardware while mitigating ecosystem fragmentation. | Weilin Cai, Yilin Chen, Yunxiang Luo | Programming Language and Compiler Technology Lab, Institute of Software, Chinese Academy of Sciences (ISCAS) (China) | – | |

| P3 | 13:00-15:30 | E | Engaging the Next Generation: ISCAS’s RISC-V Education Through Short Video: Abstract: At the Institute of Software, Chinese Academy of Sciences, the internship program is dedicated to enhancing the education and promotion of RISC-V technology through innovative short video content. Projects like the “Understanding RISC-V” series simplify complex concepts and make them accessible, while hands-on demonstrations on platforms such as MilkV Duo and LicheePi engage a wide audience, including students, educators, and aspiring engineers.The process begins with interns conducting thorough research to identify gaps in existing RISC-V content. This groundwork informs the scripting and production phases, where interns blend technical information with practical demonstrations. These videos not only explain theoretical aspects but also highlight RISC-V technology’s practical applications, helps demystify subjects that can be intimidating to newcomers.Audience feedback plays a vital role in improving videos, ensuring they effectively meet the audience’s learning needs. This iterative process helps to crop content that is both informative and engaging.These videos serve as a stepping stone, guiding learners from basic principles to complex applications and fostering a deep understanding of RISC-V. This progression allows learners to advance at their own pace and explore in-depth topics as they grow more confident.This initiative supports ISCAS’s mission to integrate cutting-edge technologies like RISC-V into core educational curricula and promote active engagement with these technologies. By translating complex engineering concepts into accessible educational content, PLCT Lab is shaping a generation of engineers to thrive in a rapidly evolving technological environment and driving global adoption of RISC-V.

| Fuyuan Zhang, Tianwei Jiang, Yunxiang Luo | Programming Language and Compiler Technology Lab, Institute of Software, Chinese Academy of Sciences (ISCAS) (China) | – | |

| P4 | 13:00-15:30 | UnityChip Verification Open-Source RISC-V verification at Abstract: The growing open-source hardware ecosystem presents a new opportunity to enhance hardware verification efficiency by involving a broader range of verification participants. As the software testing ecosystem has benefited from various tools and methods developed by its large community, this success offers a promising future for scaling out hardware verification by incorporating software testing developers. To support software developers in hardware verification, we propose three techniques to facilitate this integration: (1) providing state machine abstractions (cycle-accurate and looselytimed), (2) encapsulating hardware designs into software packages in multiple programming languages, and (3) introducing socket data transport and bidirectional direct function calls. These techniques are implemented on the CollabChip Verification (CCV) platform, enabling software developers and tools to engage in hardware verification workflows and collaborate with hardware engineers using hardware frameworks. We evaluate our methods on the XiangShan processor, demonstrating CCV’s effectiveness through case studies: software developers without hardware backgrounds uncover 11 bugs in two months. Zero-experience developers submit valid verification cases in 20 hours, and reducing average initiation time by 77% and enhancing existing verification environment with Python, accelerating the process by 16.6% and reducing lines of code by 12% | Xu An | Beijing Institute of Open Source Chip, Yunlong Xie, Zhicheng Yao | ” Institute of Computing Technology (ICT), Chinese Academy of Sciences (CAS)” | |||

| P5 | 13:00-15:30 | E | RISC-V Board and OS Support Matrix: A Comprehensive Resource for RISC-V Developers Abstract: The current market offers a plethora of RISC-V boards, with numerous operating systems (OSes) available from both the boards’ manufacturers and the community. However, newcomers to RISC-V may encounter difficulties accessing current information regarding RISC-V boards and their OS support status.To address this need, this paper has initiated a support matrix project to assist RISC-V developers and enthusiasts. The RISC-V Board and OS Support Matrix is an open-source initiative that catalogues the compatibility between RISC-V development boards and operating systems, thereby responding to the growing requirement for a well-organised, readily accessible database to guide developers in selecting compatible software for their RISC-V hardware platforms. The initiative highlights areas requiring community assistance, such as configurations marked as “”Call for Help”” (CFH), “”Call for Testing”” (CFT), and “”Work in Progress”” (WIP).Additionally, it includes tools for metadata parsing and SVG generation, helping to maintain and visualize compatibility data.This initiative is part of the broader RuyiSDK project, which aims to provide a full-stack development environment for RISC-V. The initiative integrates tools such as a package manager and a graphical integrated development environment (IDE).By offering up-to-date hardware and software compatibility data, the initiative simplifies decision-making for developers and researchers in the RISC-V ecosystem. The RISC-V Board and OS Support Matrix has been developed to facilitate the installation of operating systems and software on RISC-V boards, thereby reducing the complexity of the process for novices and promoting the development of the RISC-V software ecosystem. | Jingkun Zheng, Yunxiang Luo | Programming Language and Compiler Technology Lab, Institute of Software, Chinese Academy of Sciences (ISCAS) (China) | – | |

| P6 | 13:00-15:30 | E | RISC-V Appeal: The Growth Path from Students to Engineers Abstract: With the implementation of various large AI models, optimizing AI model training and inference has become an increasingly important task. As the interface between high-level programs and low-level chip execution, the assembly instruction set plays a critical role in optimization and often becomes both a bottleneck and a breakthrough point in the process. RISC-V offers unique advantages in this area: it is an open-source instruction set, highly scalable, and has special support for vector computations. Therefore, leveraging the deployment environment of AI models can accelerate the development of the RISC-V ecosystem.Now, it is essential to raise awareness about the unique advantages of the RISC-V instruction set.First, we will promote the characteristics of RISC-V to the student community through various channels. By taking advantage of students’ enthusiasm for following trends, we will integrate modern online elements into video production to lower the learning threshold and increase engagement. These videos will be widely disseminated through social platforms and online education channels, quickly attracting student attention.Next, as students’ interest in the RISC-V instruction set grows, they will actively search for related technical videos. During this process, the in-depth technical content provided by PLCT will help students and engineers further understand the details and applications of RISC-V. Particularly, developing a RISC-V simulator will allow learners to intuitively grasp the fundamental principles of computer architecture and understand the process of hardware instruction execution. By guiding more students to participate in actual development, we can deepen their understanding of RISC-V and effectively boost the activity of the technical community, creating a **virtuous cycle** that will attract more young engineers to join the RISC-V ecosystem.Ultimately, this will foster a young, vibrant community of engineers who are passionate about RISC-V. | Xirui Hao, Fuyuan Zhang, Yunxiang Luo | Programming Language and Compiler Technology Lab, Institute of Software at the Chinese Academy of Science (China) | – | |

| P7 | 13:00-15:30 | E | FCVT support for ACT through RISCOF Abstract: As the number of RISC-V processor models continues to increase, verifying whether a RISC-V processor complies with the ISA specification has become an important issue. As the official testing tool used for ACT testing, RISCOF can leverage the Sail-RISCV model as a reference to check whether the tested model conforms to the specification. However, the ACT test repository used by RISCOF lacks support for many test instructions and extensions, including several test cases for the zfh extension, such as `fcvt.d.h`. Therefore, we will add new test instruction support to RISCOF to address this issue.RISCOF relies on multiple testing tools for test development. These include RISCV-CTG for generating test cases and RISCV-ISAC for coverage testing. To support new test instructions, we need to add YAML nodes for the test instructions in RISC-V CTG to define them and write corresponding CGF files for the instructions. Next, we will add the relevant instruction checks to the decoder in ISAC to support the coverage detection of the new instructions. Afterward, we will run RISCOF with the generated test cases, and the results will show that the test outcomes are accurate.By adding support for test instructions to ACT via RISCOF, we can provide greater flexibility for testing, further advancing the comprehensiveness and accuracy of ACT testing.

| Zhu Xuchang, Luo Yunxiang | Programming Language and Compiler Technology Lab, Institute of Software, Chinese Academy of Sciences (ISCAS) (China) |

| |

| P8 | 13:00-15:30 | E | RISC-V in Education:Empowering the Next Generation of Engineers through Open-Source Learning Platforms Abstract: With the rapid development of computer technology,training a new generation of engineers has become an important task in the field of education.Traditional educational models often fail to provide students with a comprehensive understanding of the interaction between hardware and software.Therefore,introducing the open-source architecture of RISC-V can offer students a more practical and innovative learning platform to quickly grasp the core knowledge of computer architecture.This paper adopts the RISC-V open-source architecture as an educational tool and apply it to the teaching of computer architecture and hardware design.The open-source nature of RISC-V allows students to directly engage with the design of computer hardware and quickly understand the interaction and communication mechanisms between the lower and upper layers.As a result,through the study of cross-compilation,operating systems,and related knowledge,students can gain a better understanding of compilers and other relevant content.By introducing RISC-V into the educational field,engineers provide students with an efficient and open learning platform to help them quickly master the key skills of computer architecture and hardware design.This educational initiative not only enhances students’technical capabilities but also provides strong support for training a new generation of engineers,laying a solid foundation for future technological innovation and industry development. | Zhi Li, Fuyuan Zhang, Yunxiang Luo | Programming Language and Compiler Technology Lab, Institute of Software, Chinese Academy of Sciences (ISCAS) | – | |

| P9 | 13:00-15:30 | Open Source Hardware and RISC-V:Bridging the Digital Divide and Advancing Social Equity through Cost Reduction and Innovation Abstract: With the rapid development of computer technology,training a new generation of engineers has become an important task in the field of education.Traditional educational models often fail to provide students with a comprehensive understanding of the interaction between hardware and software.Therefore,introducing the open-source architecture of RISC-V can offer students a more practical and innovative learning platform to quickly grasp the core knowledge of computer architecture.This paper adopts the RISC-V open-source architecture as an educational tool and apply it to the teaching of computer architecture and hardware design.The open-source nature of RISC-V allows students to directly engage with the design of computer hardware and quickly understand the interaction and communication mechanisms between the lower and upper layers.As a result,through the study of cross-compilation,operating systems,and related knowledge,students can gain a better understanding of compilers and other relevant content.By introducing RISC-V into the educational field,engineers provide students with an efficient and open learning platform to help them quickly master the key skills of computer architecture and hardware design.This educational initiative not only enhances students’technical capabilities but also provides strong support for training a new generation of engineers,laying a solid foundation for future technological innovation and industry development. | Zhi Li, Fuyuan Zhang, | – | ||

| P10 | 13:00-15:30 | E | Comparative Analysis of Compiler Performance for RISC-V on SPECCPU2017 Abstact: Using instruction count as a metric, we employed SPEC CPU 2017 to compare the performance of programs compiled with GCC and LLVM on RISC-V, with a particular focus on the RISC-V vector extension. Benchmarks were run in parallel using QEMU, enabling large-scale testing. The analysis showed that tests compiled with LLVM executed more instructions than those compiled with GCC for both INT Rate and FP Rate. After enabling the vector extension, the gap in FP Rate narrowed significantly, suggesting that LLVM’s auto-vectorization performs better in certain scenarios.

| Yongtai Li, Chunyu Liao | – | |

| P11 | 13:00-15:30 | E | V8 for RISC-V in 2024: What’s new Abstract: This poster summarizes the progress of the Chromium V8 JavaScript engine for RISC-V architecture in 2024. PLCT Lab, the maintainer of the V8’s RISC-V backend, contributed over 17,000 lines of code in a total of 173 patches, which has the 5th rank among all the contribution teams. First, new JavaScript and WebAssembly (Wasm) language features were added, including managed objects and garbage collection for Wasm, enhanced API calls, and improved stack management. Second, general performance enhancements were achieved through pointer compression, a new just-in-time compiler (Maglev), optimized indirect calls in Wasm, and security features like a configurable sandbox and Control Flow Integrity (CFI). Thirdly, significant optimizations were implemented, leveraging RISC-V ISA extensions to improve jump and builtin code generation, and reduce code size. Finally, support for SV39/SV48 configurations and multicore environments was added, including I-cache flushing. Benchmark results demonstrate the notable performance improvements. Future work includes continuously tracking upstream and expanding support for features like LeapTiering and Maglev. | Yahan Lu, Ji Qiu | Programming Language and Compiler Technology (PLCT) Lab, Institute of Software Chinese Academic of Sciences |

| |

| P12 | 13:00-15:30 | Optimizing Data Transport Architectures in RISC-V SoCs for AI/ML Applications Abstract: This presentation will illustrate the challenges and solutions of data-transport architectures for artificial intelligence/machine learning (AI/ML) in the context of embedded vision architectures and discuss implementation aspects for Networks-on-Chips (NoCs) for RISC-V-based System-on-Chips (SoCs). AI/ML and Embedded Vision architectures present unique challenges in data transport architectures to procure all relevant data from off-chip DRAMs and efficiently store and transport them in caches to allow efficient computing on SoCs and systems of chiplets. These challenges directly translate into specific requirements for NoC implementation, impacting performance, power consumption, and cost, efficiently addressing the challenges posed by what the industry calls the “”memory wall”” – the much faster improvement of processor vs. DRAM memory access speed. In addition, for the automotive and industrial application domains, special considerations regarding safety and resilience need to be considered to allow for ISO26262 and related certifications.

| Michal Siwinski, Guillaume Boillet, John Min | Arteris (USA) |

| ||

| P13 | 13:00-15:30 | Development of a System for Easy Utilization of RISC-V Extensions Using Hypervisor Technology Abstract: In RISC-V, modular specifications called “extensions” are being developed one after another. However, many of these extensions remain unutilized because hardware implementations have not kept pace, leaving them in a suspended state. | Norimasa Takana, Yoshihiro Oyama | University of Tsukuba (Japan) |

| ||

| P14 | 13:00-15:30 | The choice and dilemma of integrated GPU solutions for RISC-V platform Abstract: This time, I will focus on the business development of Imagination, a major IP provider in the field of integrated GPUs for RISC-V platforms, the trends for developers and their clients, the difficulties in adapting Linux distributions, and IMG’s most criticized technical support. I will also bring you information about the “Nijigasaki High School Imagination Club” hosted by us. | Jingyu Pu | PLCT Lab (Programming Languages and Compilation Technologies Lab) (China) |

| ||

| P15 | 13:00-15:30 | E | RevyOS: Optimizing Debian for XuanTie Chip Ecosystem – Challenges and Achievements in RISC-V Adaptation Abstract: RevyOS is a tailored Debian-based distribution specifically optimized for the XuanTie chip ecosystem, developed and maintained by the RevyOS team, a subgroup within the RuyiSDK team. This presentation will explore the challenges and methodologies involved in adapting Linux distributions for diverse RISC-V hardware platforms, and introduce the current accomplishments of RevyOS. | Han Gao, Xuan Chen | PLCT Lab |

| |

| P16 | 13:00-15:30 | E | From Vector to Matrix: The Future of RISC-V Matrix Extensions Abstract: The idea of accelerating the emerging matrix workloads from artificial intelligence and machine learning has been implemented in general-purpose ISA including x86-64 (AMX) and ARMv9.2 (SME), and accelerators including NVIDIA Tensor Cores. RISC-V, as an open-source ISA, has followed this trend a multiple matrix extension drafts and implementations available. In this poster, we’ll introduce the Integrated matrix extension from Spacemit and the Attached Matrix Extension from Xuantie, Stream Computing, and SiFive (Zvma). We’ll focus on the tradeoff between “”Integrated”” and “”Attached””, the relationship between existing V extension and matrix extension, and the potential hardware implementation of RISC-V matrix acceleration in this poster. | Yan Lu | University of Tokyo |

| |

| P17 | 13:00-15:30 | E | Efficient Transposed Matrix Multiplication in DNN Training Using Custom RISC-V Vector Extensions Abstract: In Deep Neural Networks (DNNs), optimizing matrix operations is crucial for enhancing performance and energy efficiency. The open-source RISC-V instruction set architecture (ISA) supports vector extensions that accelerate data-parallel algorithms. In this work, we propose a new approach for efficient transposed matrix multiplication in DNN training by introducing a dot-product instruction alongside existing vector multiply-add instructions in RISC-V. During backpropagation, the matrix from the forward pass must be transposed. Although it is possible to perform transposition by accessing data in a different order without actually moving data in memory, this typically requires vector loads from non-contiguous addresses, making latency hiding more difficult compared to contiguous vector loads. We therefore focus on how matrix elements are oriented in registers for vector multiply-add and dot-product operations, thereby enabling the execution of transposed matrix multiplication in backpropagation while using only contiguous-address vector loads. The hardware resources for the proposed method were evaluated through an FPGA implementation, demonstrating that the same functional units can be shared by both vector multiply-add and dot-product operations. The result of multiplying a row-major matrix by a column-major matrix using the implemented core showed that the dot-product approach reduced the required number of cycles compared to combining vector multiply and vector reduction-sum instructions, while also reducing memory accesses compared to the vector multiply-add approach. These findings highlight the potential of dot-product instructions to optimize DNN workloads on RISC-V vector processors. | Riku Ando | Kawahara Laboratory, Department of Electrical Engineering, |

| |

| P18 | 13:00-15:30 | E | RISC-V based AI Accelerator design using approximate arithmetic processing elements Abstract: Research and development (R&D) on Artificial Intelligence (AI) has increased exponentially in recent years. Along with this, power demand for AI tasks has also been growing at an unprecedented rate, which has led to an increase in R&D efforts in hardware dedicated to AI applications. This poster and demonstration present an artificial intelligence (AI) accelerator design using approximate arithmetic processing elements (PEs), in collaboration with Cassia.ai with their approximate arithmetic technology and systolic array implementation, to perform hand-written digit recognition tasks using the LeNet convolutional neural network (CNN). Instead of using traditional, absolute arithmetic for PEs within the systolic array, this design proposed adapting approximate arithmetic for these PEs. This proposal is based on the fact that most AI and deep learning implementations use approximate calculations to reduce the complexity of the model, such as regularization, feature selection, and dropout, thus reducing power consumption. This design employs UC Berkeley’s Chipyard design framework and UC Berkeley’s Gemmini systolic array as the technology base to demonstrate approximate arithmetic technology. Preliminary tests with the LeNet model have shown no significant reduction in prediction accuracy, as well as performance when compared with the original Gemmini systolic array design. | Ngoc Lam Nguyen, Trong-Thuc Hoang, Cong-Kha Pham | University of Electro-Communication |

| |

| P19 | 13:00-15:30 | E | An Extension of Ripes RISC-V Simulator Abstract: Ripes is a graphical processor simulator In this project, we focus on the software-hardware We have added a tab for the stack in Ripes to In addition to the original execution control buttons, | Hitoshi Oi, Daichi Higashi | The University of Aizu |

| |

| P20 | 13:00-15:30 | E | RISC-V-based Multicore Processor for Multi-threading: Hardware to Software Design Perspective Abstract: This research explores the design of a RISC-V-based multicore processor system tailored for the data-centric era, bridging the gap between general-purpose and special-purpose architectures. Recognizing the limitations of traditional approaches in handling big data, the research emphasizes a co-design approach involving both hardware and software. The proposed architecture features a high-performance core that generates threads distributed to other cores via a thread queue. Private working spaces and bi-directional private buses minimize shared resource contention and data movement overhead. A key innovation is the integration of near-cache processing capabilities through a hybrid L1 cache, functioning as both cache and local/shared memory for tightly-coupled accelerators. This allows data to be processed closer to memory, maximizing bandwidth utilization. Benchmark results on matrix multiplication achieve a 4-6x speedup with a four-core configuration and a 6-18x speedup with an eight-core configuration. The tightly-coupled accelerators, leveraging the hybrid L1 cache, achieve remarkable speedups ranging from 24x to over 177x compared to a single core. | Binh Kieu-Do-Nguyen, Khai-Duy Nguyen, Cong-Kha Pham, Trong-Thuc Hoang | |

| |

| P21 | 13:00-15:30 | E | An evaluation of multi-core and V extension RISC-V processor Abstract: The multi-core processor architecture has been ubiquitous as the computing workload becomes more complex, especially on well established systems based on ARM or x86. The servers, PCs and even mobile devices have already adopted parallelism for improved performance since the early 2000s to improve performance on various workloads such as 3D Rendering and video transcoding. There are two approaches to parallelism on a CPU processor, namely multi-core and SIMD (Single-Instruction-Multiple-Data). RISC-V is an open instruction-set architecture which supports both multi-core and SIMD via V extension. However, there is a shortage in the number of benchmarks that target parallelism approaches on RISC-V based system, making comparison between the implementations difficult. Therefore, a method to evaluate the scalability of a RISC-V system is crucial. This work aims to perform performance evaluation on these on both multi-core and V extension enabled RISC-V based system. For the multi-core system, RV32IMAC (1-16 cores) and RV64GC (1-8 cores) Rocket Core are generated using the Chipyard framework on Xilinx VC707 FPGA platform. Under Linux software environment, a synthetic benchmark suggests that it achieves linear performance speedup as the number of cores increase, however, for a more specific workload such as graph coloring, the speedup is only 8.32x for 16-cores RV32IMAC configuration and 5.84x for 8-cores RV64GC configuration, respectively, compared to the single core variants. On the other hand, for a RISC-V core with V extension Zve32x with VLEN 128, the initial benchmark shows that it can benefit image processing workload at a speedup of up to 20x compared to the scalar core. | The-Binh Nguyen, Trong-Thuc Hoang, Cong-Kha Pham | University of Electro-Communications (UEC), Tokyo, Japan |

| |

| P22 | 13:00-15:30 | E | Development of a library characterizer for utilizing self-made cell libraries in open semiconductor design Abstract: Many open semiconductor designs and the open EDA and design environments that support them have been proposed, but these environments are based on the premise that circuit design will be performed using cell libraries provided by specific fabs. In order to load a self-created cell library into these environments, a characterizer is required, which is an EDA that characterizes the cell library by extracting its delay and power characteristics and creating a library. Here, we report on the current development status of the open source implementation of the characterizer that we are developing. | Shinichi Nishizawa | Waseda University/ISHI-KAI |

| |

⑧ RISC-V related Japanese publications

Click on the book photo to purchase

Digital Circuit Design and Computer Architecture [RISC-V Edition] (00) Large book – June 7, 2022

Computer Architecture [6th Edition] Quantitative Approach Paperback – 2019/9/25 ¥8,800

Learning RISC-V and Chisel: Building your own CPU for the first time – The first step towards implementing a custom CPU using an open source instruction set Paperback (soft cover) – 2021/8/25 ¥3,520

A must-read book for those who want to start Chisel Paperback – August 28, 2020 ¥2,750

Getting Started with FPGA Electronics with Chisel Paperback – 2022/1/9 ¥2,750

RISC-V related Japanese publications