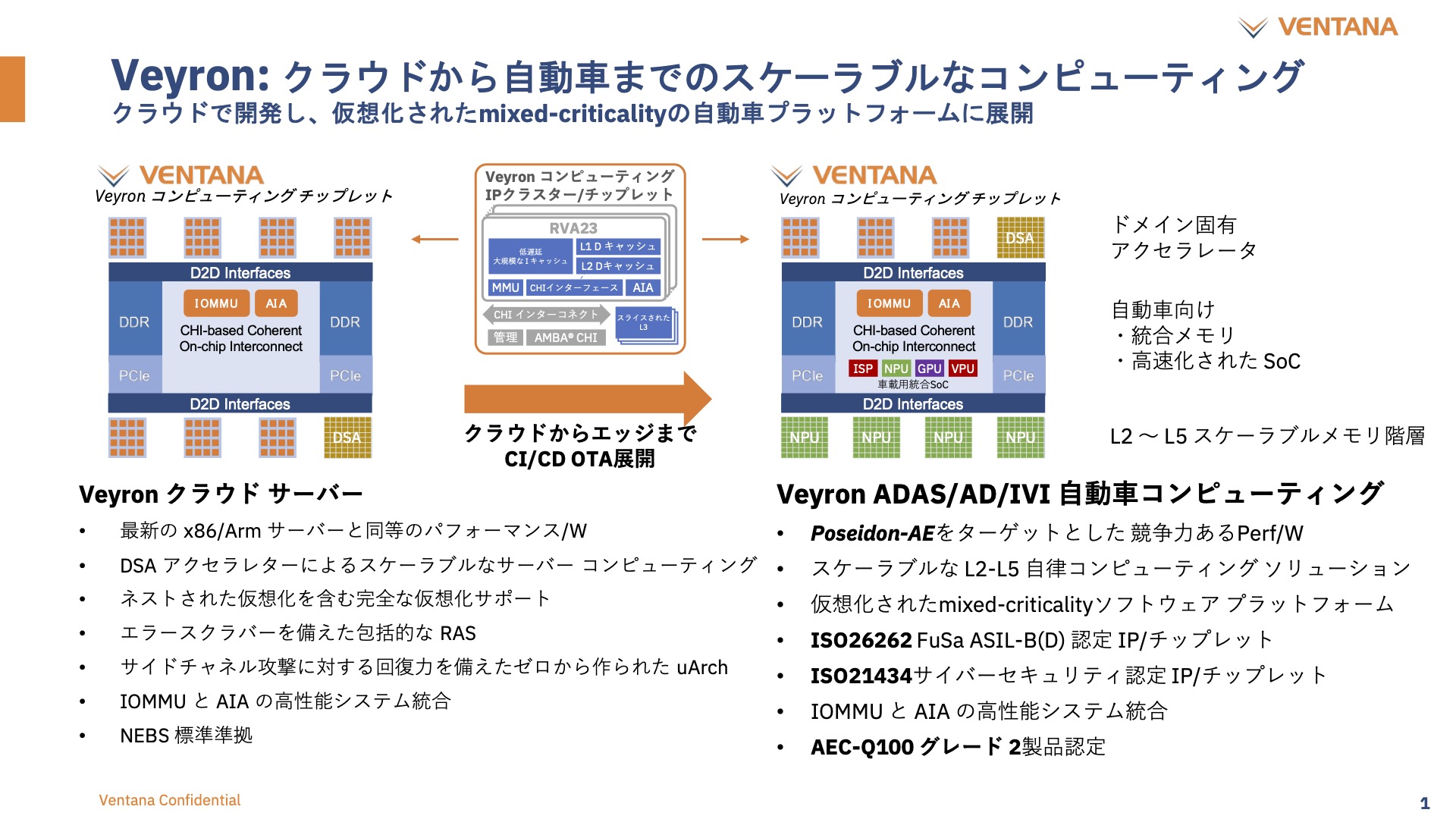

題:Ventana社のVeyron: クラウドから自動車までのスケーラブルなコンピューティング :クラウドで開発し、仮想化されたmixed-criticalityの自動車プラットフォームに展開

以下の説明は、RISC-V協会が、RISC-Vサミットから得られた情報を基に、作成したもので、必ずしも正しくない場合もあります。正確な情報は、以下のレクチャーを聴講して取得してください。

| プログラム | 月日 | 時間 | プレゼンテーション題名 | 発表者 | 所属機関 (詳細はクリック) | 場所 |

|---|---|---|---|---|---|

| ① RISC-V ソリューション | 2024年1月16日 | 10:10-10:40 | データセンタ応用に向けた高性能RISC-Vとドメイン固有アクセラレーション (DSA)導入について(仮題) | トラビス・レニア | ベンタナ・マイクロシステムズ(米国) | 地下2階 伊藤謝恩ホール |

| ② RISC-V 開発 | 2024年1月16日 | 15:45-16:05 | ベンタナマイクロシステムズ システム紹介 | 山口さとる | ベンタナ マイクロシステムズ ジャパン | 地下1階ギャラリー1 |

| ⑤ RISC-V 展示ブース | 2024年1月16日 | 12:00 – 17:00 | ベンタナ マイクロシステムズ 製品紹介 | ベンタナ マイクロシステムズ | 地下2階 ホワイエ |

Ventana Micro Systems Inc.

Ventana Micro Systems Inc.は、データセンタークラスのRISC-VプロセッサであるVeyronシリーズを開発しました。このシリーズの最初の製品であるVeyron V1は、データセンター、自動車、5G、AI、クライアントアプリケーションなど様々な分野で競争力のあるシングルスレッド性能を提供することを目指しています。Veyron V1には、アグレッシブなアウトオブオーダー・パイプライン、3.6GHzの周波数、5nmプロセス技術などの特徴があります。

その後、Veyron V2が導入され、パフォーマンスと効率性が大幅に向上しました。V2モデルは、マイクロアーキテクチャの強化、高性能プロセッサファブリックアーキテクチャの改善、キャッシュ階層の拡張、高性能ベクトルプロセッサの追加により、最大40%の性能向上を実現しています。これには、15ワイドのアグレッシブなアウトオブオーダー・パイプライン、3.6GHzの周波数、4nmプロセス技術が含まれ、最大192コアまでスケーラブルです。

Ventana Micro SystemsとImagination Technologiesはパートナーシップを結び、それぞれのCPUとGPU技術を組み合わせて、高性能でカスタマイズ可能なIPを提供することを目指しています。このコラボレーションは、特にデータセンター、自動車、5G、AI、クライアントアプリケーションなどの分野で、SoC(システムオンアチップ)やディスクリートチップ/カードの形で統合されます。

このパートナーシップは、RISC-V CPUとGPU技術の統合を通じて、様々な市場におけるRISC-Vの採用を加速することを目的としています。VentanaのVeyron RISC-V CPUプロセッサとImaginationのGPU IPの組み合わせは、モバイルや自動車市場でのクライアントオペレーティングシステムの効率的な動作を示し、業界にとってリスク低減と市場投入時間の短縮をもたらすことが期待されています。

要約すると、VentanaのVeyron製品は、高性能かつ効率的なRISC-Vベースのプロセッサを代表し、Imagination Technologiesとのパートナーシップは、業界に統合されたCPUとGPUソリューションを提供するための前進です。

Veyron:

Veyronアーキテクチャは、Ventana Microsystemsが開発した半導体設計の先駆的な進歩を代表しており、特に先進運転支援システム(ADAS)、自動運転(AD)、車載情報エンターテイメント(IVI)の分野で急速に成長する自動車産業のニーズに応えるために設計されました。Veyronは、x86およびArmサーバープラットフォームの両方との互換性を持ち、多様な技術エコシステムへの統合能力を強調しています。

データストリーミングアーキテクチャ(DSA)を取り入れることで、Veyronプラットフォームは現代の車両に必要な複雑な計算を行うための大量データの処理を容易にします。Coherent Hub Interface(CHI)ベースの一貫したオンチップ相互接続を使用し、統合されたコンポーネント間の効率的な通信を確保しています。この設計は、高度な入出力メモリ管理ユニット(IOMMU)を通じた直接メモリアクセス(DMA)の利用によってさらに強化され、大規模なデータセットを安全かつ迅速に管理するシステムの能力を高めています。

信頼性、可用性、およびサービス性(RAS)はVeyronの設計理念の中心にあり、システムの障害を予測して緩和するメカニズムを統合することで、自動車アプリケーションにとって不可欠な連続運転を確保しています。ネットワーク機器ビルディングシステム(NEBS)基準への準拠は、さまざまな環境条件での堅牢で信頼性の高いパフォーマンスに対するVeyronの取り組みを示しています。

Veyronライン内のPoseidon-AEモデルは、アーキテクチャの適応性と性能効率、特に「AE」という指定が示す「Automotive Enhanced(自動車向け強化)」への対応を証明しています。エネルギー効率が直接的にバッテリー寿命の延長と環境への影響の軽減につながる自動車アプリケーションにおいて、性能当たりのワット数(Perf/W)という重要な指標で高性能を提供するように設計されています。

Poseidon-AEの層状アーキテクチャは、部分自動化から完全自動運転機能まで、自動運転操作のスペクトルをサポートする準備ができていることを示し、L2からL5の自動運転レベルまでスケーラブルです。ISO 26262およびISO 21434基準への準拠は、モデルが最高の安全性とサイバーセキュリティベンチマークと整合していることを強調しており、Poseidon-AEが性能だけでなく、自動車コンピューティングの安全性と信頼性を提供する分野でもリードしていることを確認します。

結論として、VeyronアーキテクチャおよびそのPoseidon-AEモデルは、Ventana Microsystemsが自動車半導体ソリューションに対して革新的なアプローチを取り入れ、知能車の時代におけるパフォーマンス、安全性、および信頼性の新しい業界基準を設定することを目指していることを体現しています。

「DSA アクセラレーターによるスケーラブルなサーバー コンピューティング」

「DSA アクセラレーターによるスケーラブルなサーバー コンピューティング」というのは、特定のドメイン(分野)に特化した加速器(Domain Specific Accelerator、DSA)を用いて、サーバーのコンピューティング性能を向上させることを指します。DSAは、特定の計算作業やアルゴリズムに特化して設計されており、その結果、サーバーの処理能力や効率が大幅に向上します。このアプローチにより、サーバーシステムはより多くのデータや複雑な処理を高速に実行できるようになり、スケーラビリティが向上します。

技術的には、Apache Kafka, Apache Storm, Apache Flink, Google Pub/Sub などのツールやプラットフォームがこの種のアーキテクチャをサポートするために広く使用されています。

「クラウドからエッジまで CI/CD OTA展開」

「クラウドからエッジまで CI/CD OTA展開」というフレーズは、ソフトウェア開発と配布に関連する概念を指しています。CI/CDは「継続的インテグレーション(Continuous Integration)/継続的デリバリー(Continuous Delivery)」を意味し、これはソフトウェア開発のプロセスで、コードの変更を自動的にテストし、頻繁にアプリケーションに統合する手法です。OTAは「Over-The-Air」の略で、特にワイヤレス経由でソフトウェアの更新を配信する方法を指します。したがって、このフレーズは、クラウドからエッジコンピューティング環境に至るまで、CI/CDプロセスを通じてソフトウェア更新をOTAで配布することを意味しています。これにより、デバイスやアプリケーションが最新状態に保たれ、効率的に管理されます。

車載用統合SoC(System on Chip)の一部として組み込まれることがあり、各種の高度な処理機能を提供します。車載用統合SoCは、複数の処理ユニットを一つのチップに統合し、自動運転や車載エンターテイメントなどの高度な機能をサポートします。

ISP: Image Signal Processor。画像信号処理に特化したプロセッサで、カメラからの生データを高品質な画像に変換します。

NPU: Neural Processing Unit。人工知能(AI)と機械学習(ML)タスクの高速処理に特化したプロセッサです。

GPU: Graphics Processing Unit。画像とビデオ処理に特化したプロセッサで、3Dグラフィックスや画像レンダリングに使用されます。

VPU: Visual Processing Unit。ビジュアルデータの処理に特化したプロセッサで、画像認識やビデオ解析などに用いられます。

Coherent Hub Interface(CHI)

Coherent Hub Interface(CHI)は、ARMが開発したインタフェース規格で、特にARMv8-Aアーキテクチャで使用されます。これは、プロセッサ、キャッシュ、メモリ、他のインターフェース間のデータの移動とコヒーレンシー(一貫性)を管理するためのプロトコルです。

CHIは、システムオンチップ(SoC)内のコンポーネント間の効率的な通信を可能にすることで、高性能コンピューティングアプリケーションにおけるデータ処理と伝送の最適化を目指しています。これには以下のような特徴があります:

スケーラビリティ: CHIは、多数のコア、キャッシュ、メモリエレメントが互いに効率的に通信できるように設計されています。

高スループットと低レイテンシ: このプロトコルは、データの高速伝送と低遅延通信をサポートしており、特に大規模な計算タスクに適しています。

コヒーレンシーの管理: CHIは、システム全体でのデータの一貫性を維持するためのメカニズムを提供します。これは、複数のプロセッサやキャッシュ間でのデータの同期を意味します。

省電力設計: 効率的な通信メカニズムにより、エネルギー消費を最小限に抑えることができます。

CHIは、ARMアーキテクチャに基づくシステムの開発者にとって重要な概念であり、特にエンタープライズレベルのアプリケーションやデータセンター、高性能計算環境での使用が想定されています。

ニューラルプロセッシングユニット(NPU)

Ventana Micro Systemsが開発したRISC-VプロセッサのVeyronシリーズ、特にVeyron V1については、ニューラルプロセッシングユニット(NPU)に関する具体的な言及はありません。Veyronプロセッサは、データセンター用途に高い性能を提供することに焦点を当てており、効率的なマイクロアーキテクチャ、高いシングルソケット性能、領域固有の加速などの特徴があります。これらのプロセッサは、データセンター、自動車、5G、AI、クライアントアプリケーションなどの用途での性能最適化と効率性に重点を置いて設計されています。

ミックスド・クリティカリティ(Mixed-Criticality)

ミックスド・クリティカリティ(Mixed-Criticality)は、複数の異なる安全レベルを要求されるソフトウェアを単一のチップ上で実行することを意味します。自動車におけるミックスド・クリティカリティシステムは、例えば、ラジオの音量調整(低リスク)と電動ステアリング制御(高リスク)のように、異なる安全性が求められる機能を同一のプロセッサで制御することを指します。安全性に関しては、ISO 26262という自動車業界の機能安全規格があり、Automotive Safety Integrity Level(ASIL)にはAからDまでのリスクレベルが定義されています。

ミックスド・クリティカリティシステムを実装する際の主なトレンドとして、車両内のECU(エンジンコントロールユニット)の機能をドメインコントローラーや高性能コンピューティングプラットフォームに統合しようとする動きがあります。これにより、異なる安全レベルを持つモジュールが組み合わされることが多くなります。また、ソフトウェア定義車両(SDV)のコンセプトが普及するにつれて、消費者が求める機能をソフトウェアアップデートによって提供し、車両の柔軟性を高めるために、ミックスド・クリティカリティのアプローチが必要になってきています。

ミックスド・クリティカリティを単純化する技術的な解決策として、機能安全認証を受けたハイパーバイザーがあります。これは、システムオンチップ(SoC)のハードウェア機能を活用して、ソフトウェアを異なる、隔離された空間に分割します。ハイパーバイザーベースの設計では、各異なる空間内のソフトウェアが単一のASILレベルであると想定されていますが、システム全体としては複数のASIL指定を持つソフトウェアを含むことができ、それぞれが保護された「仮想化」された空間内に収容されます。

このアプローチにより、将来のアップデートや修正がソフトウェアのみで完了し、工場を出てからハードウェアを変更することなく、新しい機能を安全に組み込むことが可能になります。このため、ミックスド・クリティカリティは、今日および将来の自動車ソフトウェアの新しいパラダイムを作り出す要因となっています【37†出典】。

Aptivの記事によると、ADASとコックピットドメインを単一の高性能コンピューティングプラットフォームに融合させることは、効率を向上させ、車両のアーキテクチャを簡素化することによって、OEMがコストを最適化し、多機能なシステムを実現

Poseidon-AE

Poseidon-AEは、NVIDIAの新しい自動車用スーパーチップ「DRIVE Thor」に含まれています。このシステムオンチップ(SoC)は、Arm Neoverse Poseidon Platformの自動車向け強化バージョン(AE)を利用しています。DRIVE Thorは、すべてのインテリジェントな車両機能を単一のAIコンピューターに集約し、安全で確実な自動運転車に必要な十分なパワーを備えています。これには、先進運転支援システム(ADAS)や車載情報エンターテインメント(IVI)の機能が含まれます。

DRIVE Thorは、Poseidon AEコアを使用した業界で最も高性能なプロセッサーの一つとして、NVIDIAのプロモーション資料で引用されています。このチップはマルチドメインコンピューティングが可能であり、自動運転と車載情報エンターテインメントのためのタスクを分割できます。これは、同じプラットフォーム上で同時に実行される時間に敏感なプロセスを中断することなく実行できるということで、特に重要です。

DRIVE Thorスーパーチップはスケーラブルなアーキテクチャに基づいて構築されており、開発者は以前のソフトウェア開発を最新のプラットフォームに容易に移行できます。自動車アプリケーションの安全性のための最高ランクのASIL-D機能安全に設計されています。

さらに、このSoCは自動車向けの新しいデータタイプを8ビット浮動小数点(FP8)精度で導入しています。これにより、開発者は精度を損なうことなくデータタイプを管理できます。これは、従来の32ビット浮動小数点から8ビット整数データ形式への移行時に精度が落ちるという自動運転車のコンピューティングにおける重要な特徴です。

NVIDIAの目標は、車両内の多数の電子制御ユニット(ECU)を単一のコンピューターに置き換えることで、センサーフュージョンから実際の自動運転アルゴリズムまで、車両のすべての計算ニーズを処理することです。DRIVE Thorは2025年モデルの自動車メーカーに供給される予定です。

ここで提示された情報は、NVIDIAのブログとAnandTechのNVIDIA発表のカバレッジから要約されたものです。