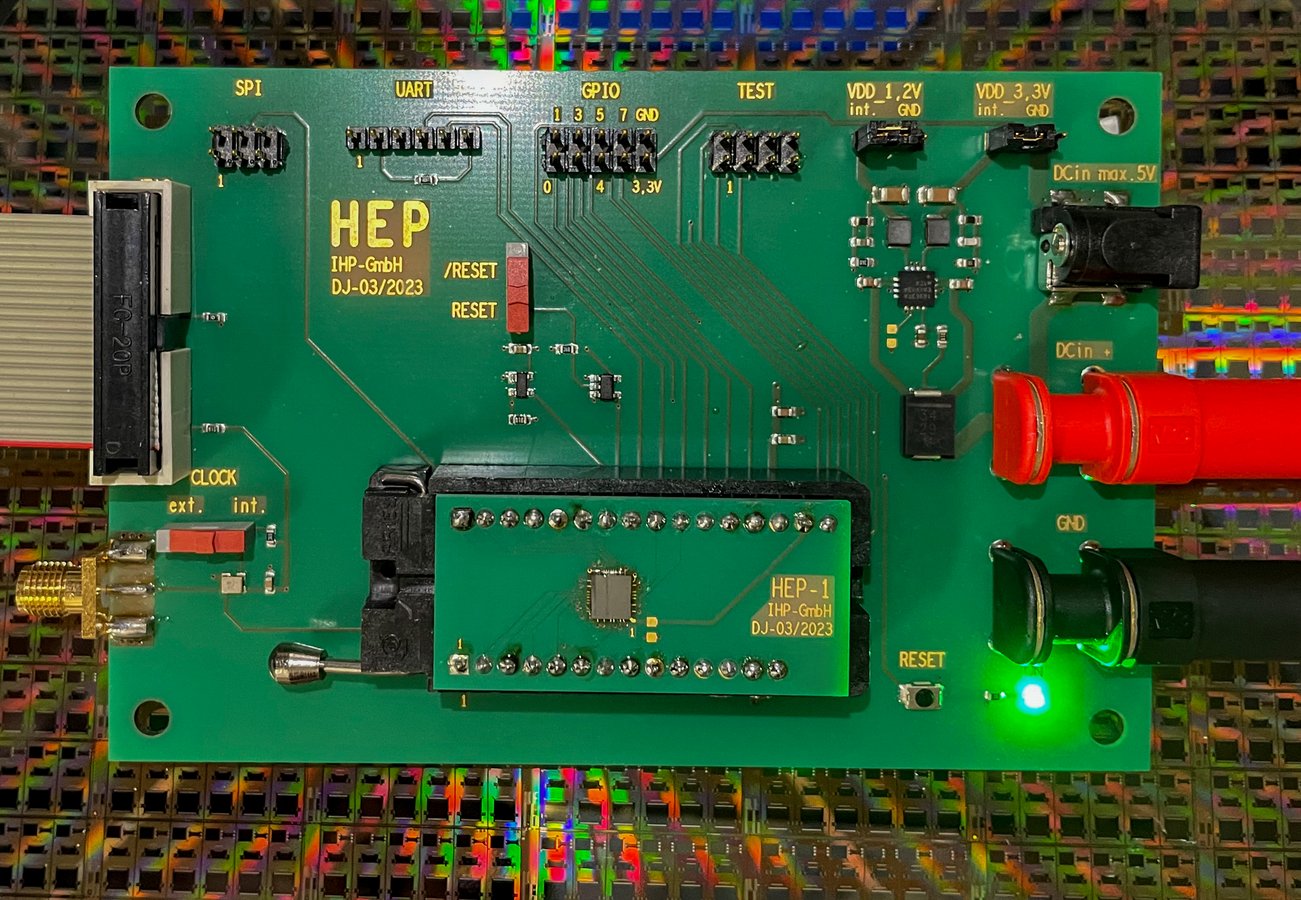

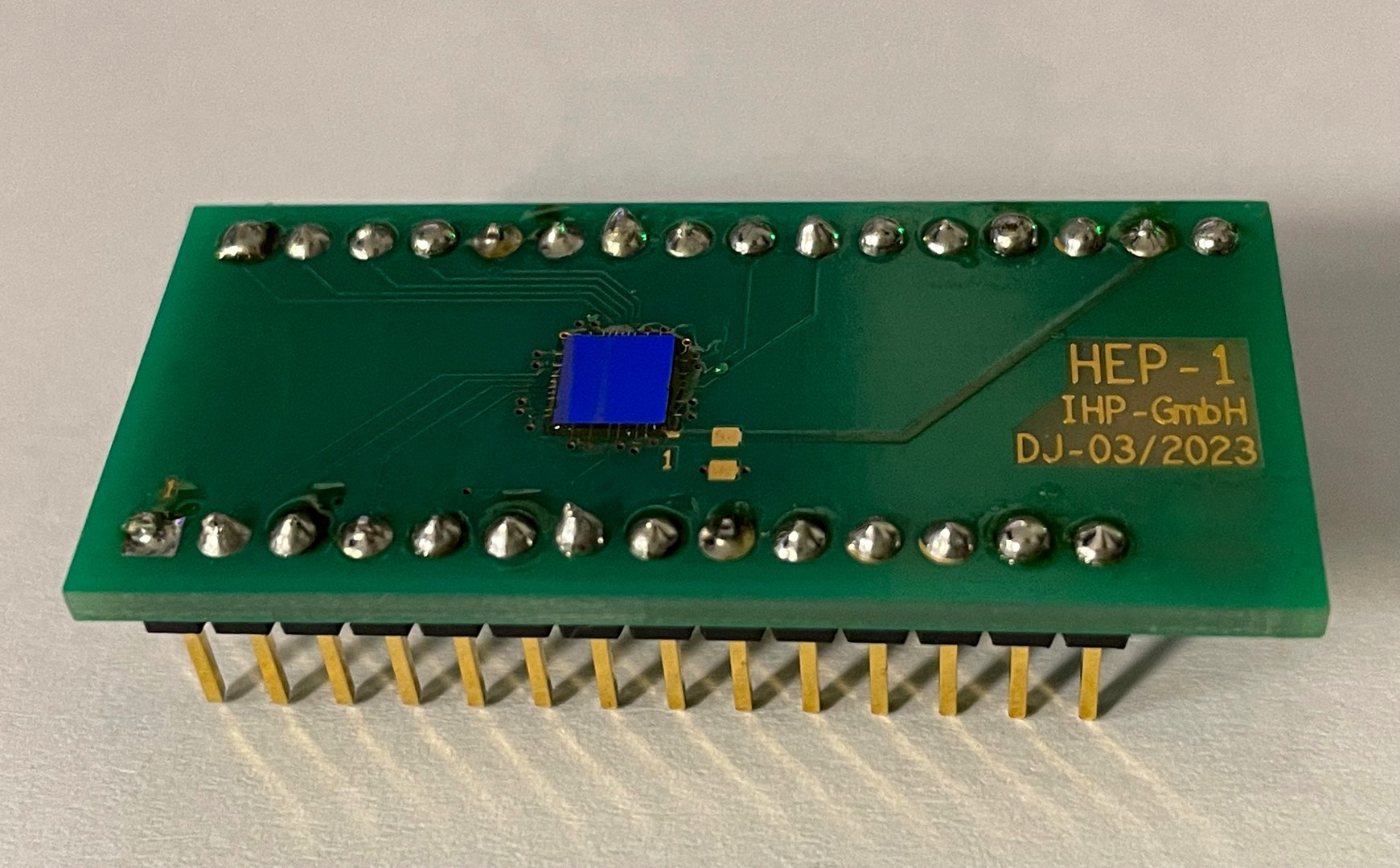

セキュリティ チップ (底部中央) は補助ボード上のフリップチップ技術で組み込まれており、メインボードの標準ソケットに差し込まれます。 メインボードは他のコンポーネントとの通信を処理します。 © IHP 2023/フランツィスカ・ウェグナー

使用したツールと設計により、研究コンソーシアムは 2 年以内にプロトタイプのセキュリティ チップを定義、設計、製造することができました。 このようにして作成されたハードウェア セキュリティ モジュール (HSM) は、とりわけ暗号アクセラレータと耐改ざんセキュリティ機能を提供します。 このプロセスで使用される開発ツールは共通の開発環境に統合され、不足している機能を含めるように拡張されました。 Google 主導の Open Titan プロジェクトも同様ですが、HEP はヨーロッパ初のプロジェクトです。 HEP は特に開発サイクルが非常に短いことが特徴です。

セキュリティ チップは、小型の個人用デバイスから自動車に至るまで、電子デバイスの多くのサプライヤーにとって不可欠です。 これらは暗号操作を実行し、改ざん、誤動作、事故を防ぐことを目的としています。 これらのチップは、オープンで柔軟に適応でき、可能な限り安全であることが数学的に証明されている必要があります。 多数のプレーヤーが関与する世界的なバリューチェーンを考えると、このようなコスト効率の高いコンポーネントの供給は大きな課題です。 いわゆるソースコードがサードパーティのレビューのために公開されるオープンソース設計は、回路設計ツール (EDA) でセキュリティが確保できる限り、多用途の代替手段を提供します。 研究コンソーシアムは、「Trustworthy Electronics」イニシアチブ (Vertrauenswürdige Elektronik) の一環として BMBF から資金提供を受けている HEP プロジェクトでこれに取り組んでいます。

詳細には、次の結果が HEP プロジェクト内で開発および実装されました。

SpinalHDL 言語の拡張: 研究コンソーシアムは、セキュリティ プロパティの半自動実装を可能にするために、オープン ハードウェア記述言語 SpinalHDL を拡張しました。 これにより、後続のチップ設計ステップ中にセキュリティ関連のステップが不必要として削除されるのを防ぎます。

VexRiscv プロセッサの正式な検証: RISC-V 設計である VexRiscv プロセッサの正しい機能は、正式な検証方法を使用することで数学的にほぼ証明されています。

オープンソースの暗号アクセラレータの開発: オープンソースの暗号アクセラレータの開発により、プロセッサのセキュリティとパフォーマンスが強化されました。

オープン マスキングの開発: 暗号計算は電力消費などのサイド チャネルを通じて追跡できる可能性があり、そこから鍵を計算することができます。 これは、新しく開発された半自動のオープン マスキング ツールで対処されます。

ヨーロッパで製造可能な IHP の実際のプロセス固有データ (PDK) を Openlane に統合: Openlane は、ハードウェア記述を 3 次元チップ設計に変換するために、独立系開発者、Google、efabless、そして当初は DARPA によって推進されているオープン ツール チェーンです。 。 Openlane の一部は、Yosys や Klayout などのヨーロッパのオープン ツールで構成されています。 ただし、チップが適切に機能するには、Openlane の結果を工場固有のプロセスに適合させる必要があります。 これらの仕様は、いわゆるPDK(Process Design Kit)に記述されています。 HEP は初めて、オープン Openlane を備えたヨーロッパの PDK を使用しました。後者はこの目的のために改良されました。

HEP プロジェクトの取り組みにより、オープン ツール専用に設計された初のヨーロッパ PDK の基礎が築かれました。

ハードウェア セキュリティ モジュールの管理を Autosar (AUTomotive Open System ARchitecture) の暗号ドライバーに統合します。

これらの成果をセキュリティ チップに実装することで、研究者らはオープン ハードウェアのセキュリティと開発サイクルの新しい基準を設定しました。

プロジェクト パートナーである Elektrobit の Detlef Boeck 氏: 「業界パートナーとして、HEP プロジェクトで開発されたコンポーネントを EB tresos の Autosar 環境に統合することが重要でした。」

プロジェクト パートナー IAV の René Rathfelder 氏: 「システムの複雑さの増大によってもたらされるリスクと脅威は、より洗練されています。 私たちは、オープンなサイバーセキュリティの開発に早い段階で取り組む機会を活用し、将来的にはすべての活動分野にオープンなサイバーセキュリティを組み込んでいきたいと考えています。」

Dr.-Ing. IHP の Norbert Herfurth 氏: 「プロジェクト コーディネーターとして、私たちの非常に意欲的で有能なコンソーシアムに非常に感謝しています。 全員が自分の仕事に情熱を注ぐと、これほど短期間で何が達成できるかは印象的です。」

製造されたセキュリティ チップは機能しますが、設計オープン セキュリティ製品に関しては、オープンな不揮発性メモリとオープンな物理乱数発生器が現在まだ不足しており、プロジェクト パートナーは両方のソリューションに取り組んでいます。 FPGA にインストールするためのコードは公開されています。 実証されたこのフローは、オープン ツールを使用したマイクロチップの設計がアクセス可能で、低コストで、学生、中小企業、産業界など、誰にとってもすぐに使用できることを示しています。

プロジェクトについて:

HEP プロジェクトは、IHP – Innovations for High Performance Microelectronics によって主導されています。

その他のパートナーには次のようなものがあります。

IAV GmbH Ingenieursgesellschaft Auto und Verkehr

エレクトロビット オートモーティブ GmbH

Deutsches Forschungszentrum für Künstliche Intelligenz GmbH

フラウンホーファー情報技術研究所 SIT

ラインマイン大学

ルール大学ボーフム校、セキュリティ工学教育機関

ベルリン工科大学電気通信セキュリティ学科

関連パートナーは次のとおりです。

CARIAD SE(フォルクスワーゲングループ会社)

ヘンソルト サイバー GmbH

ハイパーストーンGmbH

ロバート・ボッシュGmbH

スイスビット ドイツ AG

資金参照番号: ME1ZEUS012。

さらに詳しい情報:

http://hep-alliance.org/プロジェクト/

https://github.com/VE-HEP/VE-HEP-HW-SW

https://github.com/IHP-GmbH/IHP-Open-PDK