RISC-VがAIに突入→機械学習の需要により、RISC-Vチップはどこでも必要です。

https://spectrum.ieee.org/risc-v-ai

SAMUELK.MOORE著

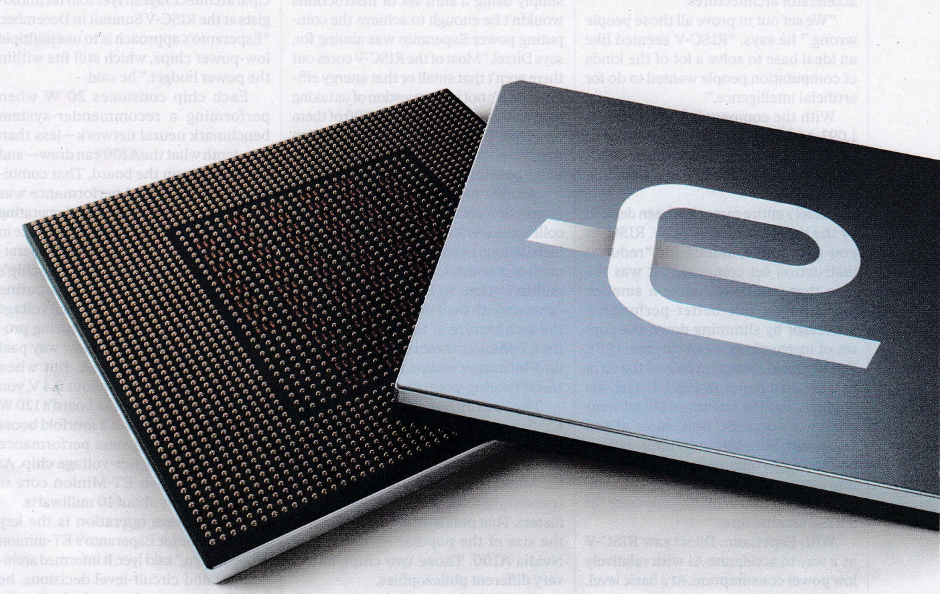

ESPERANTO TECHNOLOGIES

ET-SoC-1は、わずか20ワットを消費するシリコンに1.000を超えるRISC-Vコアを搭載しています。

2010年に最初に導入された無料のオープンソースコンピュータ命令セットアーキテクチャであるRISC-Vの採用は、ロケットのように始まっています。そして、このロケットの燃料の多くは、AIと機械学習の需要から来ています。 Semico Research Corp.によると、少なくとも一部のRISC-Vテクノロジを含むチップの数は2027年まで年間73.6%増加し、約250億のAIチップが生産され、2,910億米ドルの収益を占めます。ほんの数年前のまだ始まったばかりのアイデアから今日までの増加は印象的ですが、AIにとっては、それは海の変化のようなものでもあります、とDaveDitzelは言います。 Ditzelの会社であるEsperantoTechnologiesは、AI推奨システムで強力なGPUと競合することを目的とした最初の高性能RISC-VAIプロセッサを作成しました。 Ditzelによると、機械学習とAIの初期のマニアの間、人々は汎用のコンピューターアーキテクチャ(x86とArm)がGPUやより専用のアクセラレータアーキテクチャに追いつくことは決してないだろうと考えていました。 「私たちはそれらすべての人々が間違っていることを証明するために着手しました」と彼は言います。 「RISC-Vは、人工知能のために人々がやりたいと思っていた多くの種類の計算を解決するための理想的なベースのように見えました。」同社の最初のシリコンである1,092コアのAIプロセッサが、一連の初期のパートナーとIntelとの主要な開発契約の手に渡ったことで、彼はすぐに正しいことが証明されるかもしれません。 Ditzelのキャリア全体は、RISC-Vの背後にある理論によって定義されています。ご存知かもしれませんが、RISCは「縮小命令セットコンピュータ」の略です。実行できる命令のコアセットをスリム化することで、より小さく、低電力でありながらパフォーマンスの高いプロセッサを作成できるという考えでした。 IEEEフェローのDavidPattersonは、1980年に独創的な論文でこの用語を作り出しました。彼の学生であるDitzelは共著者でした。 Ditzelは、Transmetaを共同設立する前に、BellLabsとSunMicrosystemsでRISCプロセッサの開発に取り組みました。これにより、RISCアーキテクチャ用にx86コードを変換することで、Intelと競合することを目的とした低電力プロセッサが作成されました。エスペラントでは、DitzelはRISC-Vを比較的低い消費電力でAIを加速する方法と見なしていました。基本的なレベルでは、より複雑な命令セットアーキテクチャは、プロセッサを構成するためにシリコン上にさらに多くのトランジスタが必要であることを意味します。各トランジスタは、オフのときに少しの電流をリークし、状態を切り替えるときに電力を消費します。 「それがRISC-Vの魅力でした」と彼は言います。 「簡単な命令セットがありました。」

RISC-Vのコアは、わずか47個の命令のセットです。 x86命令の実際の数を列挙するのは奇妙なことに困難ですが、1,000に近い可能性があります。 Armの命令セットは、RISC-Vよりもはるかに小さいと考えられていますが、それでもかなり大きいです。しかし、エスペラントが目指していた計算能力を達成するには、スリムな一連の命令を使用するだけでは十分ではない、とDitzel氏は言います。 「そこにあるRISC-Vコアのほとんどは、それほど小さくもエネルギー効率も良くありません。したがって、RISC-Vコアを取り出して、チップ上で1,000個を叩くだけの問題ではありません。完全に再設計する必要がありました。これらの非常に厳しい制約に適合するようにCPUを使用します。」 Ditzelと彼の同僚が作業を開始したときのRISC-V命令セットには、行列の乗算などの機械学習の数学を効率的に実行するために必要な「ベクトル」命令が特に欠けていました。そこで、エスペラントのエンジニアが独自の技術を考案しました。プロセッサコアであるET-Minionのアーキテクチャで具体化されているように、これらには、8ビット整数ベクトルと32ビットおよび16ビット浮動小数点ベクトルの両方を実行するユニットが含まれていました。結果として得られるシステムオンチップET-SoC-1は、1,088個のET-Minionコアと、Minionsの作業を管理するのに役立つET-Maxionsと呼ばれる4つのコアで構成されています。チップの240億個のトランジスタは570平方メートルを占めます。これにより、人気のAIアクセラレーターであるNvidia A100の約3分の2のサイズになります。これらの2つのチップは、非常に異なる哲学に従います。 ET-SoC-1は、すでにインストールされているサーバーのペリフェラルコンポーネントインターコネクトエクスプレス(PCIe)スロットに収まるボードの中心にある電力に制約のあるデータセンターでAIを高速化するように設計されています。つまり、ボードには120ワットの電力しか使用できませんでしたが、価値があるには、1秒あたり少なくとも100兆回の動作を提供する必要があります。エスペラントは、そのパワーエンベロープで800以上のトリリオンを管理しました。ほとんどのAIアクセラレータは、ボードの電力バジェットの大部分を使用する単一のチップを中心に構築されていると、エスペラントのプリンシパルアーキテクトであるJayeshIyerは12月のRISC-Vサミットで技術者に語った。 「エスペラントのアプローチは、複数の低電力チップを使用することですが、それでも電力予算の範囲内に収まります」と彼は言いました。レコメンダーシステムのベンチマークニューラルネットワークを実行する場合、各チップは20 Wを消費します(A100が描画できる量の10分の1未満)。ボードには6つあります。電力とパフォーマンスの組み合わせは、期待されるパフォーマンスの犠牲なしにチップの動作電圧を下げることによって達成されました。 (一般に、動作電圧が高いということは、チップのクロックをより速く実行し、より複雑な命令セットアーキテクチャと新しい拡張機能を取得できることを意味し、2021年12月に100を超えるベクトル命令のセットを承認しました。ベクトル拡張機能を使用しても、マシンを促進します。統治機関のCTOであるMarkHimelsteinは、学習は依然としてRISC-Vコミュニティの最優先事項であると述べています。RISC-Vのマシン学習拡張機能の開発のほとんどは、マシンと統合された組織のグラフィックス特別利益グループで行われています。 -学習グループは「同じことを望んでいたため」と彼は言いますが、高性能やデータセンターコンピューティングに関心のあるグループなど、他のグループも機械学習の拡張機能に焦点を当てています。 RISC-Vの成功、Armは、多くの新しいAI機能が追加されている多くの市場のマーケットリーダーであり、RISC-Vが約15%を含む可能性がある5年後もそうなる可能性があります。トットのパーセントCPUコア設計の総収益は、Semicoprinci-palアナリストのRich Wawrzyniak氏によると。 「50%ではありませんが、5%でもありません。RISC-Vがどのくらいの期間使用されているかを考えると、それはかなり急速な成長です。」■