Google社|eFabless社 が 提供する オープンソースシャトルを使用し SHコンサルティング株式会社は、システム ASICを試作しようとしています。

マーモット RISC-V ASIC

SHコンサルティング株式会社 www.swhwc.com 2022年3月30日 作成

ウエブURL:https://platform.efabless.com/projects/759

概要:特定応用ニーズに基づき、RISC-VマイクロコントローラMARMOT ASICを、概念からGDSまで30日間で開発しました。OpenLaneツールは、事前知識なしに開発着手できます。MARMOTは、マルウェア、障害物、改ざんに対して自律的な耐性を持つマイクロコントローラです。IP知財は、Rocket SoCジェネレータから調達し、Sky130プロセス開発キットを使い、カラベルハーネス上に、OpenLaneツールを使いデジタル回路を開発しました。 IoT電源の電源電流をセンシング回路に接続されたアナログ-デジタルコンバータを高周波数でサンプリングしデータをキャプチャします。そして、ソフトウェアで各チップの電力消費を分析制御し動的に節電と動作を両立し、システムの物理電子的劣化をモニタし、マルウェア、クローン作成、およびインプラントハードウエアを検出、安全なシステムを実現します。

MARMOT ASIC

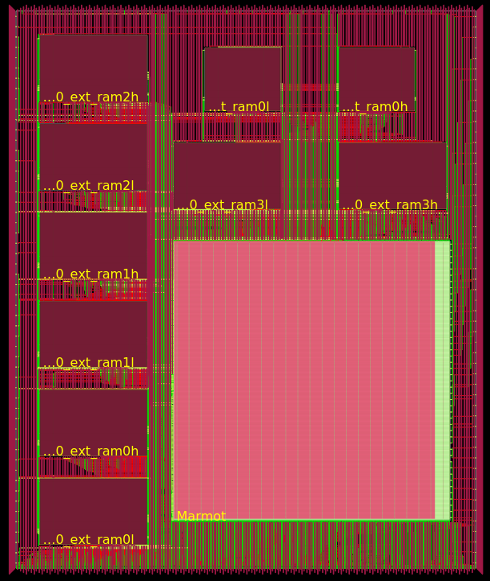

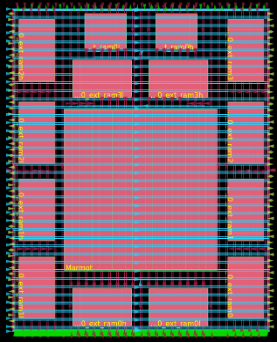

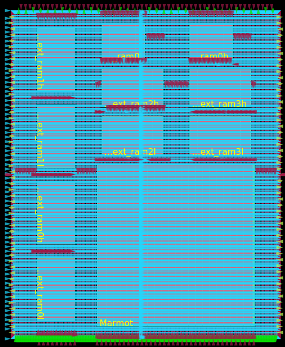

図1にMARMOTASICのチップレイアウトを示します。図1のMarmotブロックには、コアコンプレックスロジックとペリフェラルコンプレックスロジックが含まれています。 0_ext_ram01、0_ext_ram0h、0_ext_ram1l、0_ext_ram1h、0_ext_ram2l、0_ext_ram2h、0_ext_ram3l、0_ext_ram3hは、I-Cacheデータ配列を示します。 t_ram01とt_ram0hはタグRAMを示します。

図1.MARMOT ASIC

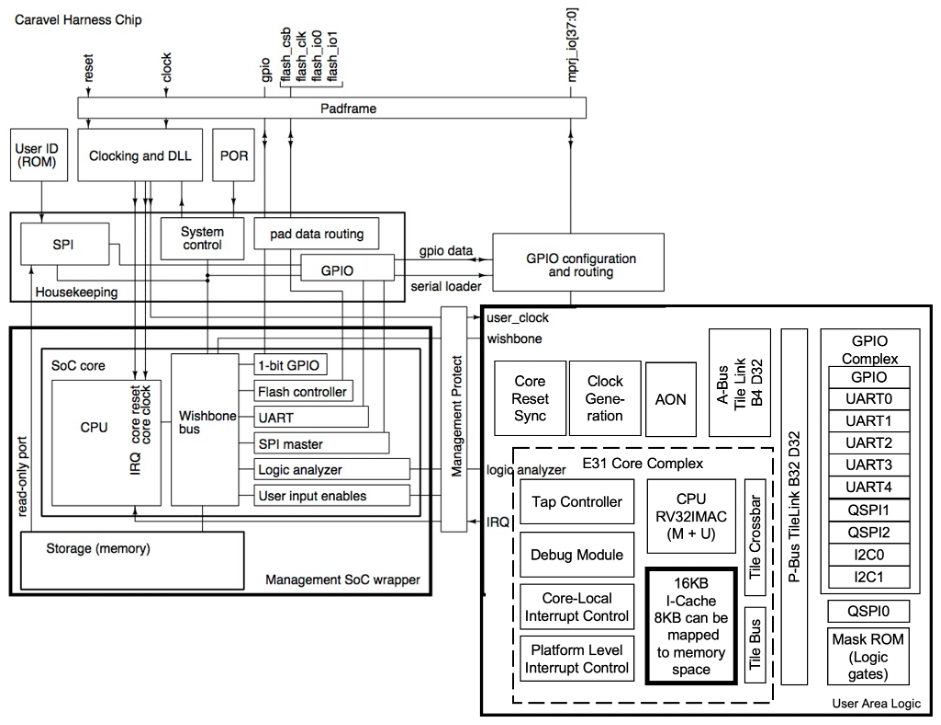

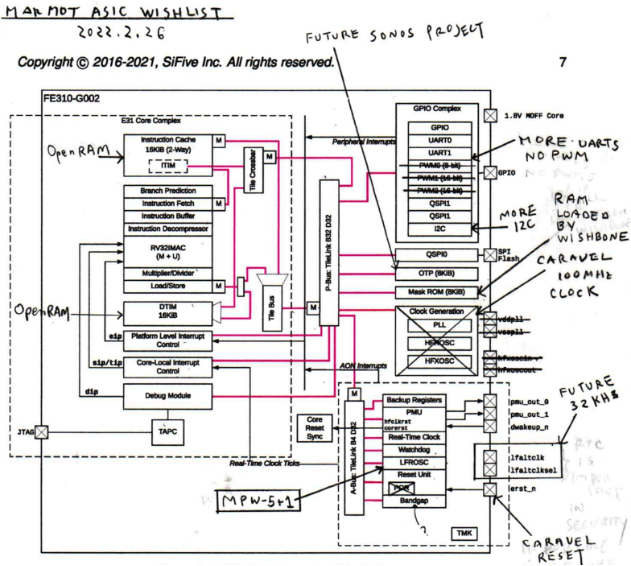

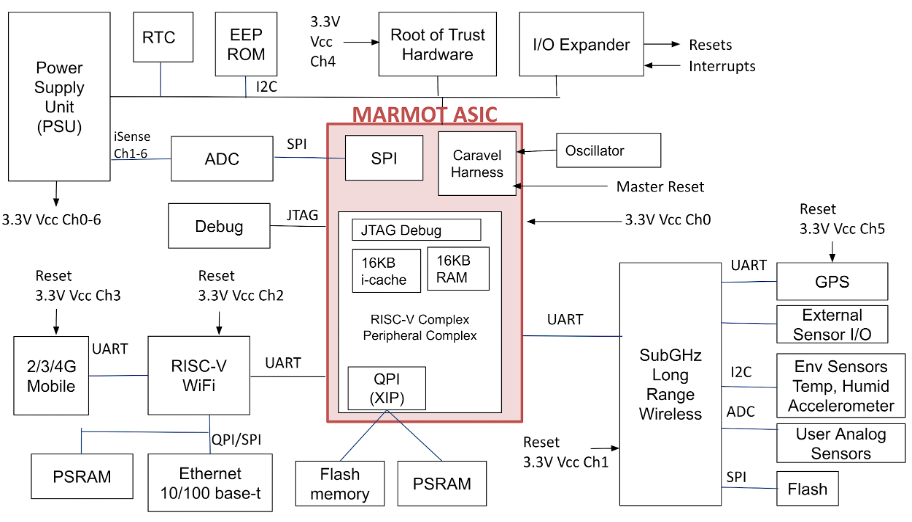

図2.キャラベルハーネスとロケットE31コンプレックスのブロック図

Rocket SoCジェネレーターは、16KBのI-Cacheと一連の周辺機器を備えたVerilog RV32IMAC命令を備えるRISC-V SoCを生成しました。 Rocket SoCで生成されたロジックは、Caravelハーネスに結合するように設計されており、I-CacheはOpenRAMにマップされていました。 I-Cacheの8KBの部分は、アドレスマップに表示されるRAMであるInstruction Tightly Integrated Memory(ITIM)として使用できます。 ITIMは、命令とデータの両方を保持できます。クロック周波数は約25MHzに制限されているようで、低速ですが、多くの組み込みアプリケーションに役立ちます。論理ゲートで実装されたブートROMは、SPIフラッシュの最初のアドレスにジャンプします。その後、プログラマーはSPIフラッシュのプログラムから必要なことを実行できます。たとえば、SPIフラッシュをデフォルトのシングルSPIからクアッドSPIに変更し、ルーチンをITIMにコピーして、実行にジャンプするなどです。

なぜロケットSoCジェネレーターを使ったのか?

チップ設計つまり、CPU、QPIインターフェイスをフラッシュメモリ、PSRAM、UARTのアレイ、I2C、SPIに接続するために、設計工数と検証工数の最大70%を費やします。 Rocket SoCジェネレーターは、サブサーキットのメタ定義から派生した最上階層のRTLを自動的に生成します。自動的にSoC論理回路を生成する技術の背後には、Chiselと呼ばれる新世代のデジタル設計言語の力があります。 Chiselは、オブジェクト指向言語や関数型言語などのソフトウェアエンジニアリングをデジタルデザインに取り入れます。 Chiselを使用すると、レジスタ転送レベルでハードウェアを表現もできますが、ハードウェアジェネレータを作成できます。

Rocket SoC GeneratorとOpenLaneを使用し1月で行ったテープアウト

エンジニアは日中の仕事を続け、仕事は時間と週末の後に行われました。明らかに、テープアウト後も作業しなくてはなりません。デザインをソフトで検証するには、デジタル回路を含んだFPGAを作成する必要があります。

2022年2月25日:マルチプロジェクトウェーハファイブ(MPW-5)に参加することが決定されました

2月26日:MARMOTASICウィッシュリストが作成されました。

3月16日:ロケットSoCの生成とロジックシミュレーションが完了しました。 OpenLane論理合成ジョブが途中でエラーをスローしました。

3月17日:もう1人のエンジニアがエラーを再現しようとしましたが、さまざまなエラーが発生しました。エラーはメモリ不足が原因であると結論付けられました。 64GBのRAMを搭載した2台の新しいデスクトップPCを急いで購入しました。

3月19日:OpenLaneネットリスト合成が完了しました。メッセージは、ツールが35GBのメモリを消費したことを示しています。 Rocket SoCジェネレーターが出力するロジックの規模とOpenLaneロジックシンセサイザーの動作により、35GBを超えるRAMが消費されました。ホールドタイミング違反に対処するために、さらに何回か反復が行われました。1回の論理生成処理の実行には3時間かかりました。 OpenLaneレイアウトはDRCエラーをスローします。

3月20日:Slack#openlaneとGitHubIssueのコミュニティは、寛大で明確なヒントを提供しました。 DRCエラーは抑制されました。同様の方法でLVSエラーが解決されました。

3月21日:OpenLaneルーティングツールは「ルーティング輻輳」エラーをスローしましたが、それ以上の分析はありませんでした。混雑エリア情報を取得する方法が提案されましたが、役に立ちませんでした。 MPW-5の期限は、日本時間帯で3月22日に容赦なく過ぎました。

2022年3月27日:試行錯誤の末、GDSが作成されました。デザインはローカルプリチェックをパスしました。

2022年の2月は28日しかありませんでした。従って、プロジェクトはちょうど30日でテープアウトできたことになります。

フロアプランと自動ルーティング

チップフロアプランは、チップの物理的なレイアウトを設計するエンジニアリングタスクです。チップのフロアプランには、物理設計エンジニアによるレイアウトの作成の努力が必要です。

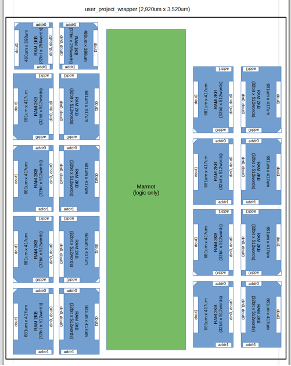

図3.マーモットASICのフロアプランの進化

図3の左側の最初の平面図は最初に作成されました。 これは「ウィッシュリスト」に基づいています。 配線の混雑が予想されましたが、私たちはOpenLaneデジタル設計プロセスを進めました。設計が進むにつれて1つの「ウイッシュ」が取り除かれました。削除されたのは、DTIMメモリです。

図4.マーモットASICの「ウィッシュリスト」願い事表

今回は時間を節約するために、最初に「ウィッシュリスト」を作成しました。「ウィッシュリスト」は、技術性がないと軽んじられます。プロジェクトの中でのプライオリティを技術者に伝える重要なドキュメントです。初心を大切にすることは重要なことです。 最初の願い事には、その中に製品の目的のすべてが含まれ、多くの潜在的可能性を含んでいるものです。さらに開発プロジェクトが右往左往した時に立て直すためのレベレージポイントになります。 「ウィッシュリスト」が専門家に移管された後、それより広い概念が議論されることも、それより良いリストが策定される可能性は経験的には少ないです。 後日、専門家が行う技術方向性の判断は、確実性をますが、最初にあるいはプロジェクト途上で認識されたニーズに応えるための妨げになることもあるからです。

なぜLinuxではなくRTOSなのか?

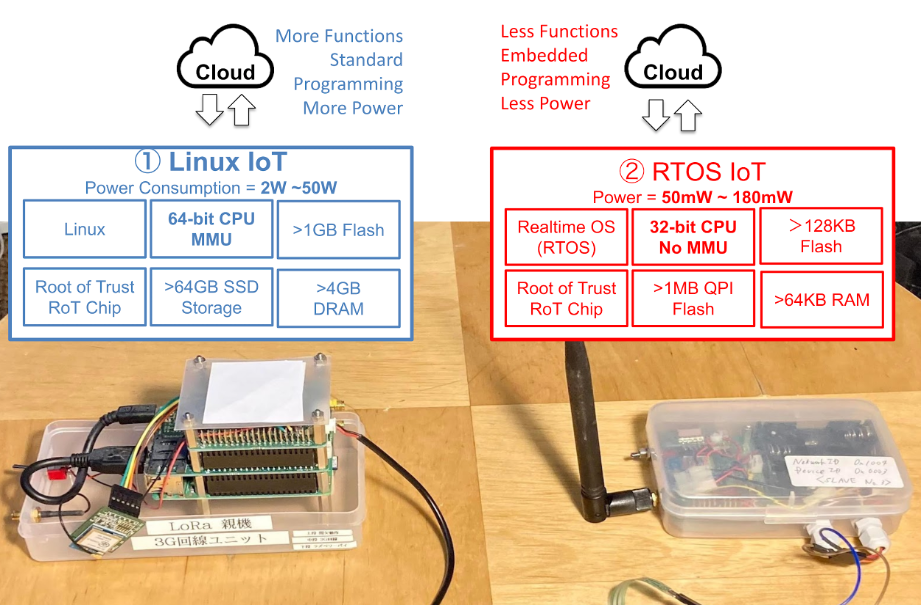

図5.Linux型IoTとRTOS型IoTにおける、機能、性能、および電力性能の利害特質

図5は、LinuxIoTとRTOSIoTの長所と短所を示しています。 Linux IoTは、プログラミングを容易にするために、より多くの機能、標準化されたプログラミング環境、および一貫した線形計画メモリスペースを提供します。 RTOSシステムは複数のマイクロコントローラに分割されているため、デバイスのプログラミングが複雑になります。 一方、RTOS IoTは、その時点で使用されていないシステムの一部をオフにする場合があります。 Linux IoTは休止状態になる可能性がありますが、システムが休止状態の場合でも、DRAMリフレッシュ電力を消費します。

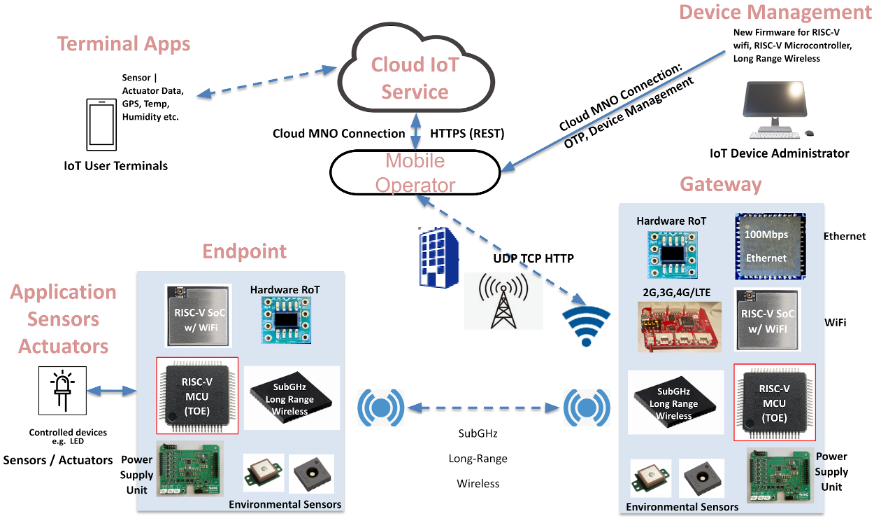

図6.マーモットASICを適用するIoTシステムの例

図6に、IoTシステムの例を示します。 エンドポイントとゲートウェイは、恒久的な電源から解放されて、何年にもわたってソーラーパネル上で動作します。

IoT電源ユニット

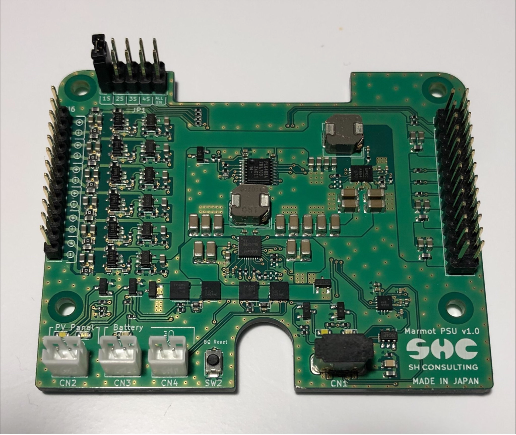

図7. RTOS IoT用電源ユニット(PSU)の写真

図7の電源ユニット(PSU)は、複数の電源から電力を受け取ります。 ソーラー、リチウムイオン、可変DC電圧(例:2.6V-20V)、およびUSB-C。 PSUは7つの独立した電源レールを提供し、そのうち6つはI2Cコマンドを使用してオンとオフを切り替えることができます。 PSUは、IoTの動作中に、各電源レールの電流を測定できます。 測定回路が電流測定を行わない場合に大きな電力損失を引き起こさないように設計されています。 IoTサービスプロバイダーは、IoTデバイスが改ざん、複製、移植された時期を知る必要があります。 IoTデバイスのリモート電源分析により、クローン作成、埋め込み、マルウェアなど、デバイスの物理的、構造的、および電気的劣化が明らかになる可能性があります。

図8.RTOS IoTのブロック図と電源チャンネルの配置例

図8は、MARMOT ASICが統合されているシステムにおける電源チャンネルの詳細例を示しています。 ディスクリートADCは、標準のマイクロコントローラよりも高いサンプルレートを実現します。 キャプチャされた大きなサンプルデータはPSRAMに保存されます。 16MB。汎用入力および出力(GPIO)は、リセットピンと割り込みピンを交差させるために拡張されています。

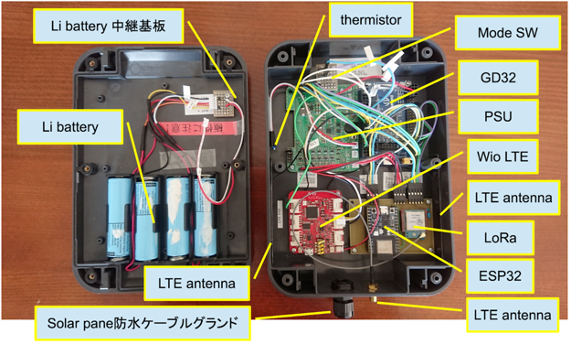

図9.RTOS型IoTの写真

図9に、MARMOT ASICのシステム例を示します。 複数のワイヤレスチップセットに注意してください。 これらのチップは、データ/制御交換のためにUARTを介して相互に接続されています。 UARTは、IoTアプリケーションだけでなく、無線ファームウェアアップグレード(OTA)にも使用されます。 I2Cは、センサーとルートオブトラスト(RoT)ハードウェアのインターフェースに必要です。

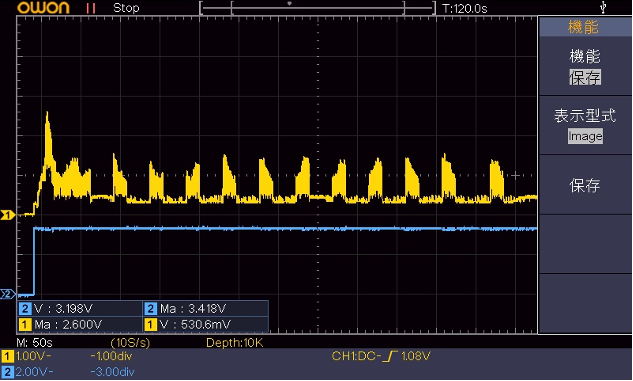

図10. PSUにより測定した2G/ 3G/4G-LTE電源チャンネルのIccおよびVcc波形

図10は、電力線からの波形例を示しています。電流は黄色、電圧は青色で、この場合はLTEワイヤレスチップセットからのものです。 電源投入後、初期化処理が完了すると、30秒ごとに電力を消費する処理が行われます。

結論

Rocket SoCジェネレーターとCaravelハーネスを活用するASICを組み合わせて、130ナノメータのSky130プロセスを使い、実用的なマイクロコントローラASICを開発するという着想は、初めから良いものに見えました。1ヶ月経った今もそう思います。 技術的アプローチは、より気の長い調査が必要です。オープンソースEDAツールとプロセス開発キットの技術から具現化できるものを明確にするため、多くの時間を費やすことになると思います。ムーア法則が消えても、半導体デジタル回路で、飛躍的なミニチュアリゼーションが可能で、PC基板に比較し半導体が格段の信頼性を提供することは変わりません。マイコンASICを設計する能力を、システムメーカがほぼ無償で得ることにより、その商売に潜在的な競争力をもたらします。日本に存在するレガシー半導体ファブも存続するだけでなく、将来に、大きなビジネスポテンシャルを持つことができます。

謝辞

この成果は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の委託業務(JPNP16007)の結果得られたものです。