ジョン・ペディ著01.27.2021 0

https://www.eetimes.com/rv64x-a-free-open-source-gpu-for-risc-v/

愛好家のグループは、3Dグラフィックスとメディア処理用に設計されたグラフィックス命令の新しいセットを提案しています。これらの新しい命令は、RISC-Vベースベクトル命令セットに基づいて構築されています。階層化された拡張機能としてグラフィック固有の新しいデータ型のサポートが追加されます。コアRISC-V命令セットアーキテクチャ(ISA)の精神に基づいています。ベクトル、超越数学、ピクセル、テクスチャ、およびZ /フレームバッファ操作がサポートされています。融合したCPU-GPUISAにすることができます。命令は64ビット長になるため、グループはこれをRV64Xと呼んでいます(堅牢なISAをサポートするには32ビットでは不十分です)。

なぜ今なのか?

世界には選択できるGPUがたくさんありますが、なぜこれなのですか?グループによると、商用GPUは、デュアルフェーズ3D錐台クリッピング、適応可能なHPC(任意のビット深度FFT)、ハードウェアSLAMなどの異常なニーズを満たすにはあまり効果的ではありません。コラボレーションは柔軟な基準を提供し、他の方法で必要とされる10〜20人年の労力を削減し、ミスを回避するための相互検証に役立ちます。

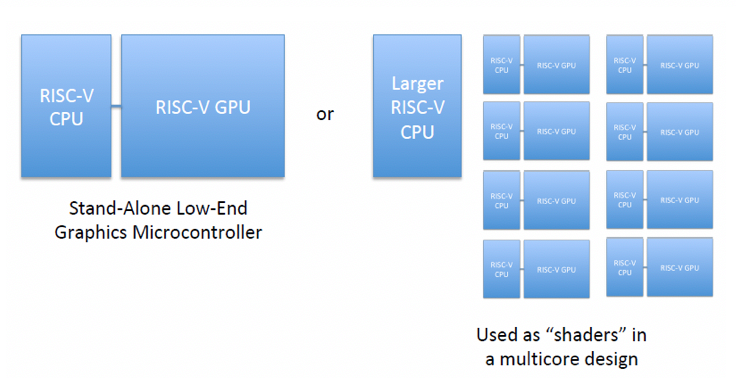

チームは、彼らの動機と目標は、カスタムのプログラム可能性と拡張性を備えた、小さくて面積効率の高い設計を作成したいという願望によって推進されていると述べています。低コストのIP所有権と開発を提供し、商用製品と競合してはなりません。 FPGAおよびASICターゲットに実装でき、無料でオープンソースになります。初期設計は、低電力マイクロコントローラーを対象としています。 Khronos Vulkanに準拠し、時間の経過とともに他のAPI(OpenGL、DirectXなど)をサポートします。

ソフトウェア開発を変革したオープンソース運動は、ハードウェア開発者の間で注目を集めています。 RISC-Vアーキテクチャを中心とした初期の取り組みが先導しています。今後のオープンソース特別プロジェクトでは、オープンハードウェア開発の可能性と落とし穴を探ります。

最終的なハードウェアは、GPU機能ユニットを備えたRISC-Vコアになります。プログラマーにとっては、64ビット長の命令がスカラー命令としてコーディングされた単一のハードウェアのように見えます。プログラミングモデルは明らかなSIMDです。つまり、3Dを送信するためにRPC / IPC呼び出しメカニズムは必要ありません。これには、可変発行、述語SIMDバックエンド、ベクトルフロントエンド、正確な例外、ブランチシャドウイングなどが含まれます。未使用のCPUメモリスペースからGPUメモリスペースへのAPI呼び出し、またはその逆のAPI呼び出し、とチームは言います。また、16ビットの固定小数点(FPGAに最適)および32ビットの浮動小数点(ASICまたはFPGA)として利用できるようになります。

設計では、Vblock形式(Libre GPUの取り組みによる)を採用します。

それは少し似たVLIWです(実際にはそうではありません)

命令のブロックには、ブロック内のスカラー命令に追加のコンテキストを与えるレジスタタグが前に付けられています

サブブロックには、ベクトルの長さ、スウィズリング、ベクトル/幅のオーバーライド、および予測が含まれます。

これはすべてスカラーオペコードに追加されます

ベクトルオペコードはありません(そして必要ありません)

ベクトルコンテキストでは、次のようになります。レジスタがスカラーオペコードによって使用され、レジスタがベクトルコンテキストにリストされている場合、ベクトルモードがアクティブになります。

アクティブ化すると、ハードウェアレベルのforループが(1つだけではなく)複数の連続したスカラー演算を発行します。

実装者は、SIMD、複数発行、単一実行など、希望する方法でループを自由に実装できます。

この設計では、スカラー(8ビット、16ビット、24ビット、および32ビットの固定および浮動小数点)と、超越関数(sincos、atan、pow、exp、log、rcp、rsq、sqrtなど)を使用します。ベクトル(RV32-V)は、2〜4要素(8、16、または32ビット/要素)のベクトル操作と、ポイント、ピクセル、テクセル(基本的には特別なベクトル)の一般的な3Dグラフィックスレンダリングパイプラインの特殊な命令をサポートします。 )

XYZWポイント(64ビットおよび128ビットの固定および浮動小数点)

RGBAピクセル(8、16、24、および32ビットピクセル)

UVWテクセル(コンポーネントあたり8ビット、16ビット)

ライトとマテリアル(Ia、ka、Id、kd、Is、ks…)

行列は2×2、3×3、および4×4の行列で、属性ベクトルをサポートするメモリ構造とともにネイティブデータ型としてサポートされ、基本的に4×4の行列で表されます。

融合CPU-GPUISAの利点の中には、マイクロコードで標準のグラフィックパイプラインを実装し、カスタムシェーダーのサポートを提供し、レイトレーシング拡張機能を実装する機能があります。また、AIおよび機械学習用の8ビット整数データ型を使用した数値シミュレーション用のベクトルもサポートしています。

スプライン、サブディビジョンサーフェス、パッチなどのカスタムラスターライザーを実装できます。

設計は、カスタムパイプラインステージ、カスタムジオメトリ/ピクセル/フレームバッファステージ、カスタムテッセレータ、およびカスタムインスタンス化操作を実装できるほど十分に柔軟です。

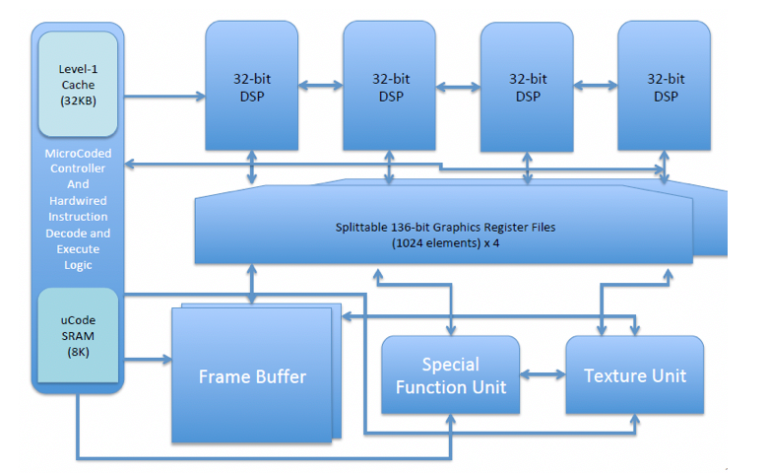

RV64Xのブロック図

RV64Xリファレンス実装には次のものが含まれます。

命令/データSRAMキャッシュ(32KB)

マイクロコードSRAM(8KB)

デュアル機能命令デコーダ

RV32VおよびXを実装するハードワイヤード

マイクロコード化された命令デコーダ