Apr. 22・23, 2021 / 9:00 〜 17:00 Japan Standard Time (GMT+9)

RISC-V Days Tokyo is Japan’s largest live online RISC-V event, featuring presentations, virtual demo booths, and an online press conference. RISC-V Days Tokyo aims to bring together leading RISC-V technologies and products, key persons and engineers, and to provide business opportunities for product recognition, collaboration among companies, technology exchange and information gathering. Last year’s Day Tokyo 2020 attracted a total of 1,053 participants from 11 countries (Japan, Sweden, the United States, Taiwan, France, China, Russia, the United Kingdom, Switzerland, Vietnam, and Denmark).

Supporter

Schedule

DAY 1 : April 22nd (Thu), 2021 / 9:00 〜 17:00 JST (GMT+9)

DAY 2 : April 23rd (Fri), 2021 / 9:00 〜 17:00 JST (GMT+9)

- We are offering “ Virtual Demo Booth ” as a new attempt to hold online. Interactive demos and Q & A sessions through live streams, as well as individual “private talks (Emails)”, are possible. Please experience this new attempt at RISC-V Day Tokyo!

DAY 1 : April 22nd (Thursday), 2021 / 9:00 〜 17:00 JST (GMT+9)

Schedule in Japan Standard Time (GMT+9) Please note that the speakers and contents are subject to change, and the schedule may change on the day of the event due to various reasons.

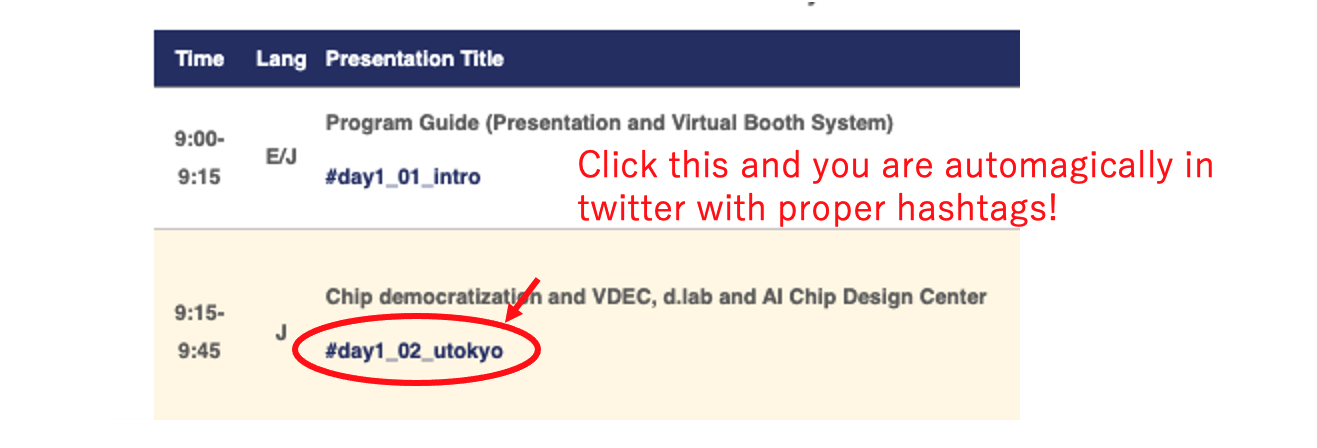

| Time | Lang | Presentation Title | Speaker | Affiliation | Media |

|---|---|---|---|---|

| 9:00-9:15 | E/J | Program Guide (Presentation and Virtual Booth System) by an MC | Eiji Kasahara | Esperanto Technologies | |

| 9:15-9:45 | J | Chip democratization and VDEC, d.lab and AI Chip Design Center | Makoto Ikeda | University of Tokyo, School of Engineering, Dept. of EE and IS, Computing and Communication System Course, Professor | |

| 9:45-10:15 | J | AI Chip Design Center | Kunio Uchiyama | Chief Executive Officer, AI Chip Design Center, NEDO Project, AIST | |

| 10:15-10:45 | J | Implementation of RISC-V based AI Accelerator by ASIP Designer | Mitsuru Tomono | Senior Application Engineer, Solutions Group, Processor & Security IP solutions, Synopsis | |

| 10:45-11:15 | J | Global standard IDE will support your software development on RISC-V | Naoki Matsuda | Sales team Account manager, IAR Systems | |

| 11:15-12:05 | J | Japanese customer announced AI Chip SiFive RISC-V inside! Introducing the forefront technology of SiFive | Atsushi Ishii | SiFive, Inc. / Representative in Japan | |

| 12:05-13:00 | E/J | 2020 RISC-V highlight collection video broadcast | Video | |

| 13:00-13:30 | E | Introducing the ESP32-C3, a RISC-V-based WiFi/BTLE SoC | Jeroen Domburg | Senior Software & Technical Marketing Manager, Espressif Shanghai | |

| 13:30-14:00 | E | RISC-V Everywhere: Why and How | Florian Wohlrab | Head of Sales EMEA and Japan, Andes Technology | |

| 14:00-14:30 | J | Introducing the GD32VF103 RISC-V based MCU | Ken Kageyama | Marketing Director, GigaDevice Japan | |

| 14:30-15:00 | J | Accelerate Edge Computing with RISC-V in Efinix FPGA | Ikuo Nakanishi | Country Manager, Japan, Effinix | |

| 15:00-15:30 | E | Use cases for RISC-V processor IP Commercial cores for real life applications#day1_11_cloudbear | Alexander Kozlov | CTO, CloudBEAR | |

| 15:30-16:00 | J | RISC-V SoC Development on C2RTL System-Level Design Verification Framework | Tsuyoshi Isshiki | New System Vision Research and Development Institute, President / Dept. Information and Communications Engineering,Tokyo Institute of Technology, Professor | |

| 16:00-16:30 | E | Syntacore open-source and commercial RISC-V solutions | Alexander Redkin | CEO, Syntacore | |

| 16:30-17:00 | J | RISC-V and open source, FPGA, semiconductor products | Shumpei Kawasaki | SH Consulting K.K. | |

| 17:00-17:15 | E/J | Foundation of RISC-V Alliance Japan | RISC-V Alliance Japan |

DAY 2 : April 23rd (Friday), 2021 / 9:00 〜 17:00 JST (GMT+9)

Schedule in Japan Standard Time (GMT+9) Please note that the speakers and contents are subject to change, and the time may change on the day of the event due to various reasons.

| Time | Lang | Presentation Title | Speaker | Affiliation | Media |

|---|---|---|---|---|

| 9:00-9:15 | E/J | Program Guide (Presentation and Virtual Booth System) Explanation by an MC | Eiji Kasahara | Esperanto Technologies | |

| 9:15-9:45 | J | Linux boot with RISC-V processor on Cadence emulator | Fumio Arakawa | The University of Tokyo, Designate Researcher | |

| 9:45-10:15 | J | Realization of Simultaneous Multi-Threading in RISC-V Architecture | Keita Nagaoka | Tokyo University of Agriculture and Technology, 1st-year master student | |

| 10:15-10:45 | J | Tiny Low-Power Processor for IoT Edge Devices | Yuko Hara-Azumi | Tokyo Institute of Technology, Associate Professor | |

| 10:45-11:15 | J | Out-of-order superscalar processor RSD and SIMT accelerator HORNET | Ryota Shioya | The University of Tokyo, Associate Professor | |

| 11:15-11:45 | J | An easy-to-use Linux-compatible RISC-V personal computer on an FPGA starter board | Kise Kenji | Professor, Tokyo Institute of Technology | |

| 11:45-12:15 | J | Trusted RV: 64bit RISC-V TEE with Secure Coprocessor and software on them | Kuniyasu Suzaki | Technology Research Association of Secure IoT Edge application based on RISC-V Open architecture (TRASIO), Researcher / National Institute of Advanced Industrial Science and Technology (AIST), Senior Researcher | |

| 12:15-13:30 | E/J | 2020 RISC-V highlight collection video broadcast | Video | |

| 13:30-14:00 | E | Pineapple ONE: homemade 32 bit RISC-V CPU made only out of basic logic components and memories – no FPGA or microcontrollers | Filip Szkandera | Higher School and Secondary School of Electrotechnical Engineering in Olomouc, Czech Republic | |

| 14:00-14:30 | J | The potential of RVfpga for computer education | Hideharu Amano | Professor, Department of Information and Computer Science, Keio University / The Imagination University Programme | |

| 14:30-15:00 | J | Open Source EDA Tools Training Course (tentative title) | Takahiro Kitayama | Kamake no Susume, Shumpei Kawasaki | SH Consulting K.K. | PDF1 |

| 15:00-15:30 | J | LSI Development by Open Source EDA software for Democratization LSI business #day2_11_logicresearch | Tadaaki Tsuchiya | Logic Research, President | |

| 15:30-16:00 | J | OSEDA servers for Open Hardware Developments | Seijiro Moriyama | President, Anagix Corporation | |

| 16:00-16:30 | J | Design and Fabrication of Custom RISC-V Chip using Open Source EDA; A Case of LED Blink | Junichi Akita | Professor, Kanazawa University | |

| 16:30-16:45 | E/J | Ending Remarks from RISC-V Alliance and Announcements for RISC-V Days Tokyo 2021 Fall | RISC-V Alliance Japan |

Virtual Demo Booth

The virtual demo booth provides opportunities for visitors to “see” demos and ask questions through a live streaming.

Schedule in Japan Standard Time (GMT+9) Subject to change

| Time | Title | Company / Organization | Media |

|---|---|---|---|

| 4/22 9:00 〜 18:00 4/23 9:00 〜 18:00 | SiFive Update | LSI Design Service Dept. Members | DTS INSIGHT, Corp. | Site |

| 4/22 15:00-17:00 4/23 15:00-17:00 | 「RVfpga」- The Complete Course in Understanding Computer Architecture, Japanese version available now! | Guanyang He | Imagination University Programme, Marketing and Business Assistant | |

| 4/22 N/A 4/23 N/A | Ariel IoT SoC Development Platform Featuring Andes N25F RISC-V Core | Florian Wohlrab | Head of Sales EMEA and Japan, Andes Technology | |

| 4/22 15:00-16:00 4/23 15:00-16:00 | Quantum Accelerator with RISC-V | Ikuo Nakanishi | Country Manager, Japan, Efinix | |

| 4/22 13:00-16:00 4/23 13:00-16:00 | Andes Corvette F1 RoT with AWS IoT Core | Hoan Huynh | Senior Software Engineer, SH Consulting Vietnam Company Limited |