(Abstract Deadline July 20, 2024)

Thursday, August 1, 2024

8:00-18:00 Japan Standard Time JST (UTC+9)

Click Here to Register for the Event

Ito International Research Center, The University of Tokyo

| Contents Categories |

| ① RISC-V Solutions |

| ② Special Sessions:Japan’s Semiconductor Strategy 2024 and RISC-V |

| ③ RISC-V Lunch Meetings |

| ④ RISC-V Technical Exhibits |

| ⑤ RISC-V Research and Open Semiconductors |

| ⑥ AI、RISC-V Research Poster Session |

The RISC-V Day Tokyo conference is the largest RISC-V event in Japan. The RISC-V Day Tokyo 2024 Winter conference will be held on Tuesday, August 1, 2024 from 9:00-18:00 JST (UTC+9) at the Ito International Research Center, The University of Tokyo. We will bring together excellent RISC-V-related technologies and products, as well as key people and engineers, and provide business opportunities such as increasing product awareness, realizing collaboration between companies, technology exchange, and information gathering. We look forward to your participation on this occasion! A video of the presentation and information on materials will be posted on the website at a later date.

① RISC-V Solutions ② Special Event: Japan’s Semiconductor Strategy 2024 & RISC-V ③ RISC-V Lunch Party

August 1, 2024 Time: 9:00-18:00

Chair: SH Consulting, Haruyuki Tago

| Time | du-ra-tion | Lang | Presentation Topic | Presenter | Organization | pres-en-ta-tion |

|---|---|---|---|---|---|

9:00- | 30 min | – | Attendees can enter 2nd basement floor and hall. Reception staffs hands out name tags, bottled tea, and take free order for “Japan’s Semiconductor Strategy 2024 1/2”. | Staff sets up recording equipment, audio, and video systems, exhibition booths. | |

| 9:30- 9:40 | 30 min | JE | Opening Remarks: From “Japan’s Semiconductor Strategy 2024+1/2” | Haruyuki Tago | Editor of the book “Reading Japan’s Semiconductor Strategy 2024,” SH Consulting | – |

| 9:45- 10:15 | 30 min | E | KEYNOTE: Empowering AI Innovation with Versatile and Open-source RISC-V Processor: Tenstorrent empowers AI innovation using versatile and open-source RISC-V processors. Our scalable AI accelerators, based on the Tensix core, utilize RISC-V for efficient control flow and data movement. Specialized vector and matrix engines enhance AI computation. The high-performance Ascalon RISC-V processor, with advanced features, supports heterogeneous computing, making it ideal for AI and server tasks. This open and modular approach enables high adaptability, performance, and efficiency across various AI applications, fostering innovation and meeting diverse computational needs. | Wei-Han Lien | Chief CPU architect and Senior Fellow in Architecture, Tenstorrent (Canada) | Video |

10:20– | 30 min | E | Predictive maintenance by AI anomaly detection with ultra-low power custom RISC-V processor: We will introduce Codasip’s next-generation processor architecture technology, the new 100/700 RISC-V processor family, the new Codasip Studio Fusion, the new Bounded Custom concept, high performance and flexibility in edge IoT, AI, and sensor fusion applications, as well as CHERI, a safety technology that halves vulnerabilities. In the second half, we will demonstrate predictive maintenance based on the low-power L110 RISC-V core. This is an example of optimizing and customizing the processor for AI anomaly detection, lowering the clock to 1/4 while maintaining performance equal to or better than the base core, and achieving ultra-low power consumption. | Brett Cline // CCO (Chief Commercial Officer), Zdenek Prikryl // CTO (Chief Technical Officer) | Codasip (Germany) | Video |

10:50– | 340 | – | Break time: Participants can visit the booths during this break. | Exhibitors will set up their booths before this time. | |

11:00-11:30 | 30 min | E | Leverage RISC-V to Win Your Success: RISC-V’ s new, no burden characteristic makes it special; it is invisible, and it encourages innovation. It may help you and your team to achieve success through innovation. Andes provides RISC-V cores IP to help you to gain control in using RISC-V cores in building System On Chip (SoC) designs. In this presentation, Andes new RISC-V CPU IP products will be reported, roadmap plan will also revealed. This will include Out of Order RISC-V processors, RISC-V Vector processors and ISO-26262 automotive grade RISC-V processors. AI accelerator solutions will be introduced, and Andes Custom Extension electronic design automation tools will be reported as well. | Frankwell Jyh-Ming Lin | CEO and Chairman, Andes Technology (Taiwan) | Video |

11:35-12:00 | 15 min | E | Introduction of Poster Session Presenters: Professor Nakajo explains the poster submissions. Each presenter gives a one-minute explanation of their poster on stage. Participation in the poster session is open to academics, individuals, and companies alike, provided that the submitted content meets the criteria outlined in the call for applications and is deemed to have valuable applications or research significance. Participants are required to submit an abstract and, upon approval, bring their A0-sized poster at their own expense. Panels and demonstration tables will be provided by the organizers. | Video | |

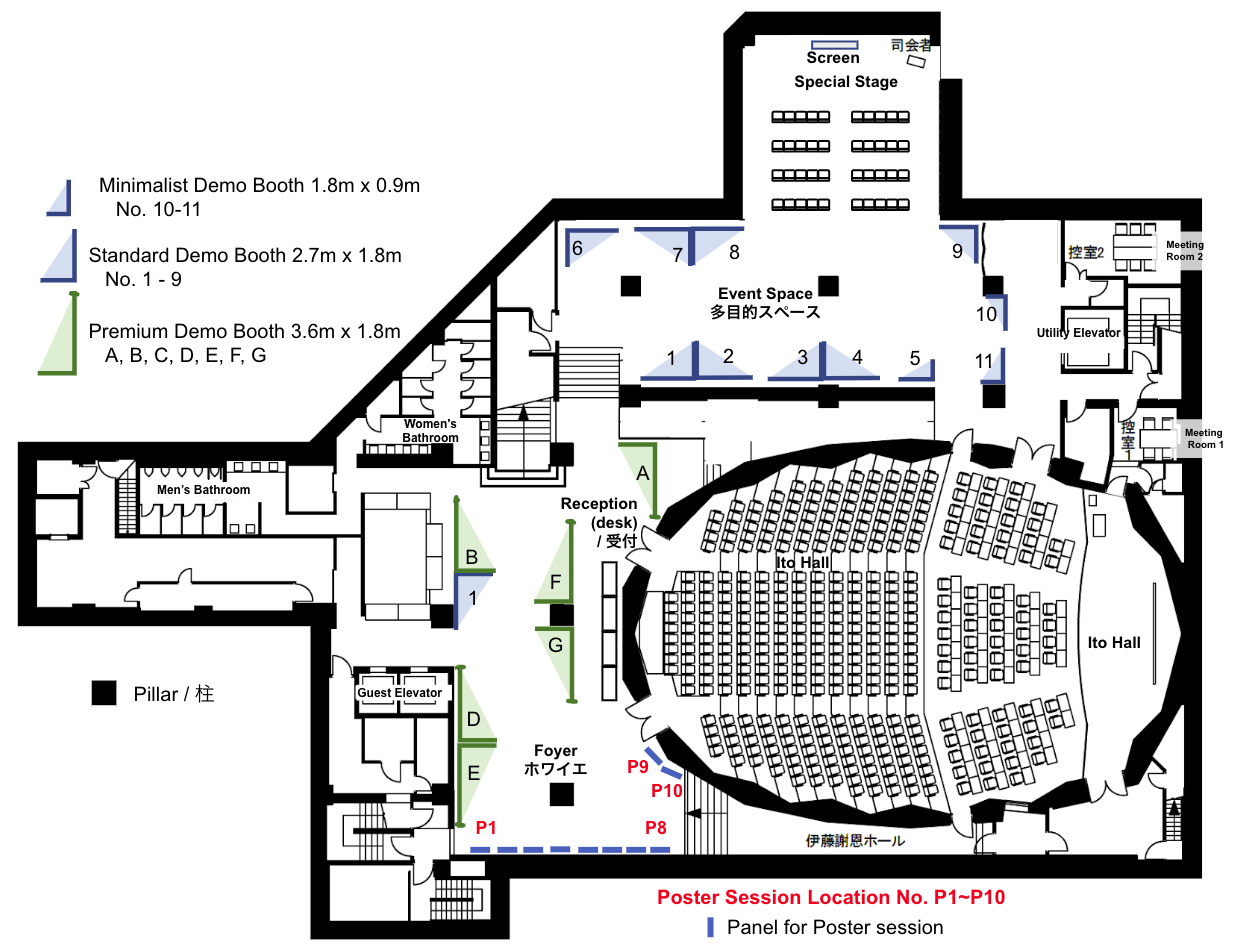

12:00-15:00 | 180 min | E | Poster presentation takes place at the south foyer of Ito Hall, B2. Please refer to the floor plan maps and look for poster panel locations P1 through P10. | One-to-one presentations by selected poster presenters | – |

| 12:00-14:30 | 120 min | – | The Beginning {Lunchtime Reception}: The lunch networking session at RISC-V aims to facilitate interaction between the specialized, segmented fields of the semiconductor industry. From business, application, and technological perspectives, participants will discuss how Japan’s semiconductor industry can build a strong position and achieve high competitiveness within the global supply chain. It is essential for each participant to create and share their vision for the revival of Japan’s semiconductor industry, fostering a collaborative environment that identifies common challenges and individual contributions. | Staff will provide a simple lunch, courtesy of Ventana Microsystems, and drink to attendees. If staff does not reach you, please collect your lunch pack at the reception. | – |

| 12:15-12:25 | 10 min | J | {Special Feature: Japan’s Semiconductor Strategy 2024 1/2} | Shumpei | An Author of “Reading Japan’s Semiconductor Strategy 2024”, SH Consulting K.K. | Video |

12:30-13:00 | 30 min | J | Japan’s Semiconductor and Digital Industry Strategy (Invited Speaker): Semiconductors are key technologies that are extremely important from the perspectives of DX (Digital Transformation) and GX (Green Transformation). The Ministry of Economy, Trade and Industry formulated the “Semiconductor and Digital Industry Strategy” in 2021. Two years have passed, and the global situation has significantly changed, making it more urgent to address economic security risks, strengthen the semiconductor supply chain, and respond to digitalization and green initiatives. In light of these circumstances, we revised the strategy for the first time in two years in June 2023. In this presentation, I will introduce specific strategies and initiatives, focusing primarily on an overview of semiconductor-related policies and human resource development measures, including subsequent updates. | Hisashi Saito | Deputy Director, IT industry division, Commerce and Information Policy Bureau, Ministry Economy, Trade and Industry | Video |

13:05-13:15 | 10 min | J | Advanced Semiconductor Education: Fostering Future Engineers with VLSI Design and Education Center (VDEC): This presentation highlights VDEC’s role in fostering future engineers through its extensive support in VLSI design education, utilizing advanced CAD tools, and practical VLSI chip fabrication services. | Makoto Ikeda | University of Tokyo VLSI Design and Education Center (VDEC) and Systems Design Research Center (d.lab) | Video |

13:20-13:30 | 10 min | J | Overview and Activities of Leading-edge Semiconductor Technology Center (LSTC): Leading-edge Semiconductor Technology Center (LSTC) was established in December 2022 as a platform for the sustainable and autonomous development of Japanese semiconductor industry through research and development of cutting-edge semiconductor technology and human resource development. Currently, 14 institutions, including Rapidus Corporation, 3 national research institutes, an inter-university research institute corporation, and 9 national universities, participate in the organization, which leads Japanese cutting-edge semiconductor research and human resource development. | Masahiko Mori | Executive Director | Leading-edge Semiconductor Technology Center (LSTC) | Video |

| 13:35-13:45 | 10 min | J | Tenstorrent’s Collaborations with the Japanese Industry: For Tenstorrent, Japan holds a significant position globally. This presentation highlights Tenstorrent’s engagement with the Japanese economy and industry. This presentation plans to introduce Tenstorrent’s role for the Research and Development Project for Enhanced Infrastructures in Post-5G Information and Communication Systems, funded by NEDO. | Yasuo Ishii | Chief Architect, RISC-V Products, Tenstorrent (Canada) | Video |

| 13:50-14:00 | 10 min | J | 10-minute position statement in the Japanese region: Andes worldwide position in RISC-V industry will first be reported. With Andes’ leading position, we aim to bring our competitive RISC-V solutions to the Japanese market, helping various Japanese industries—including system, machinery, communication, software, semiconductor, chip, and IC design service industries—achieve success. We will share “what” and “how” proposals in this regard. | Frankwell Jyh-Ming Lin | CEO and Chairman, Andes Technology (Taiwan) | Video |

| 14:05-14:15 | 10 min | J | Expectations for SoCs and Processors in Automotive Systems – For the Advancement of Embedded Systems: Automotive systems have contributed to safer and more comfortable transportation by realizing more advanced control through various means, from mechanical control to hydraulics, electricity, and electronics. Now, the focus is shifting to more advanced computing technologies, including data-driven approaches, as the next method. This text discusses the background of the growing attention to these computing technologies and the expectations for SoCs and their essential component, processors, as key enablers. | Hideki Sugimoto, Project Director, Semiconductor-Originated Key Technologies R&D Div., | Video |

| 14:20-14:30 | 10 min | JE | The End {Special Feature: Japan’s Semiconductor Strategy 2024 1/2} | Shumpei Kawasaki | An Author of “Reading Japan’s Semiconductor Strategy 2024”, SH Consulting K.K. | |

| 12:00-14:30 | 120 min | – | The End {Lunchtime Reception}: Lunch will be provided courtesy of Ventana Microsystems. Reflecting on last year’s experience where a significant number of dinner bento boxes remained unused, we are aiming to reduce food waste this year. Until 2 PM, we will strive to distribute one bento box per person. After 2 PM, any remaining bento boxes will be offered to those who still have an appetite. As we will prepare only the necessary amount, we appreciate your cooperation to ensure everyone receives their share. Thank you for your understanding. | After the lunch reception ends at 2PM, the remaining lunches and drinks, courtesy of Ventana Microsystems, will be distributed. If you would like more, please visit the reception to receive additional servings. | |

14:30-14:50 | 20 min | J | Simplifying Debugging for RISC-V Based Chips: From Simple Microcontrollers to Complex Multi-Core SoCs: Improving the debugging process for RISC-V architecture enhances development efficiency and system reliability. This document introduces solutions for debugging cores with a modular RISC-V instruction set and extensions, as well as Lauterbach’s modular TRACE32 system. It explains the role of debuggers in embedded system development and the importance of reliability in industries like automotive and aerospace. By introducing TRACE32® PowerView software and hardware modules, it offers an integrated debugging approach for RISC-V systems. | Yuji Mouri | CEO, Lauterbach Japan KK | Video |

14:55-15:15 | 20 min | J | Building a RISC-V Ecosystem to Promote Innovation in Heterogeneous Computing: This presentation focuses on integrating VeriSilicon’s Image Signal Processor (ISP) IP ISP8000, DeWarp Processor IP DW200, and 2.5D Graphics Processor Unit (GPU) IP GCNanoV into Canaan’s K230 chip, emphasizing the creation of high-precision, low-latency edge AIoT solutions. It explains the benefits for applications in large-model and multimodal input edge terminals, 3D-structured light recognition modules, and interactive robots. | Nob Moriwaki | VP of Sales, Japan | VeriSilicon Corporation | Video |

| 15:15-15:45 | 30 min | J | General-Purpose RISC-V Flash Microcontroller “R9A02G021”, 64-bit General-Purpose Microprocessor “RZ/Five”, RISC-V 32-bit ASSP for Voice and Motor Control: Renesas Electronics presents three innovative RISC-V products: the versatile R9A02G021 flash microcontroller for various embedded systems, the powerful RZ/Five 64-bit microprocessor for complex tasks, and the specialized 32-bit ASSP for voice and motor control. These products enhance performance and capabilities across applications, demonstrating Renesas’s commitment to technological advancement and innovative solutions. | Kimiharu Eto | Vice President of the Embedded Processing IC Development Division, Head of Musashi Site | Video |

| 15:50-16:10 | 20 min | E | All-in-one RISC-V AI Compute Engine for Software Defined Everything:AI has evolved from academic research to real-time applications, spanning data centers to embedded systems like mobile phones, cars, and cameras. The development of specialized NPUs for AI tasks faced a paradigm shift with the rise of Transformers, demanding new designs and architectures. The recent emergence of Generative AI like in Meta’s Llama2, has extended the need for powerful edge processing. This evolution necessitates a flexible, scalable, and open processing solution. Semidynamics’ “All-in-one” RISC-V AI Compute Engine, integrates Llama2, exemplifies the benefits of the RISC-V open ISA and open AI software frameworks, offering a future-proof and software-friendly approach. This presentation will explore the advanced AI models in embedded environments. | Volker Politz | Chief Sales Officer, Semidynamics | Video |

| 16:15-16:35 | 20 min | E | Introducing the Veyron V2: Ventana Micro Systems’ High-Performance Data Center-Class RISC-V Processor for Diverse Applications: This presentation outlines the features and applications of Ventana Microsystems’ latest RISC-V processor, “Veyron V2.” Designed for data centers, the Veyron V2 boasts high scalability, advanced interrupt architecture, and comprehensive security features. It enhances performance across diverse applications including AI, 5G, and automotive sectors. Through real-world case studies, the presentation demonstrates the processor’s effectiveness and practical benefits. | Travis Lanier | Vice President of Marketing & Product at Ventana Micro Systems. | Video |

| 16:40-16:55 | 20 min | JE | Evaluation and Award Announcement for the Poster Session: Participants in the poster session will be eligible for awards. On the day of the event, winners will be selected for their outstanding presentations and will be invited to the stage in the hall to receive their recognition. Certificates of award will be sent to the winners at a later date. | Hironori Nakajo | Professor, Department of Intelligent Information Systems Engineering, Tokyo University of Agriculture and Technology (Japan) | Video |

| 17:00-17:30 | 30 min | J | Detailed Protocol for Integrating 2nm Product Designs into Rapidus Corporation’s Foundry Services (Tentative): This presentation outlines the comprehensive protocol for integrating 2nm product designs into Rapidus Corporation’s advanced foundry services. It focuses on acceptance criteria, process flow, and technical requirements, including the necessary IPs such as standard libraries, volatile and non-volatile memory, and high-speed I/O interfaces required to construct digital logic. The protocol also covers design validation, compatibility assessment of IPs and standard libraries, and adherence to industry standards. Additionally, it analyzes Rapidus Corporation’s cutting-edge facilities and techniques supporting 2nm technology manufacturing, including DMCO and RUMS. | Koki Tsurusaki | Director, Design and PDK Technology Department, Rapidus Corporation | Video |

| 17:30-17:40 | 10 min | JE | Today’s Summary: Host: Haruyuki Tago | Haruyuki Tago | Editor of “Reading Japan’s Semiconductor Strategy 2024”, SH Consulting K.K. |

|

| 17:40-18:00 | 20 min | – | taAll staff and attendees leaves the premise of Ito Hall premises and heads home: All staff and attendees leave the Ito Hall premises and return home. Staff remove recording equipment and WiFi systems from the hall, place trash in collection bags and load them into vehicles, and return facility furniture to its original location. Participants, staff, and all belongings leaves from the second basement floor. |

| – |

④ RISC-V RISC-V Technology Exhibition

August 1, 2024 10:00-15:30

B2F Foyer, multipurpose space

Please note that exhibitors and content are subject to change.

| ブース番号 | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| A | 10:50- | Andes Technology | Andes Technology | |

| B | 10:50- 16:30 | Codasip | Codasip | |

| D | 10:50- 16:30 | Renesas General Purpose RISC-V Flash MCU “R9A02G021”, 64-bit general-purpose microprocessor “RZ/Five”, 32-bit ASSP for Voice control, 32-bit ASSP for Motor Control, etc. | Renesas Electronics Corporation | |

| E | 10:50- 16:30 | TBD | TBD | |

F | 10:50- 16:30 | Tentorrent AI Products | Tenstorrent | |

| G | 10:50- | RISC-V General-Purpose CPU Akaria NS Family: Addressing the thermal and cost constraints of edge devices and embedded systems with the compact, low-power NS11A, the NS31A for control microcontrollers, and the NS72 for applications. The NS31A is a RISC-V CPU designed for AUTOSAR platforms, complying with ISO 26262 ASIL D functional safety requirements, featuring ECC for memory, and a dual-core lockstep architecture to ensure high reliability and safety. | DENSO Corporation |

| ブース番号 | Time | Booth Title (with URL) | Company (with URL) | Note |

|---|---|---|---|---|

| 1 | 10:30- 16:30 | Kyoto Microcomputer | Kyoto Microcomputer | |

| 2 | 10:30- 16:30 | eFabless / OpenMPW chip / TinyTapeout Metallurgical microscope projection of chip, Kyushu Institute of Technology chip, OpenMPW8 inch wafer, inverter puzzle, etc. | ISHI-KAI | |

| 3 | 10:30- 16:30 | TBD | TBD | |

| 4 | 10:30- 16:30 | DTS Insight’s RISC-V ICE Solution | DTS Insight | |

5 | 10:30- 16:30 | TBD | TBD | |

6 | 10:30- 16:30 | VeriSilicon IP Solutions and Services | VeriSilicon K.K. | |

7 | 10:30- 16:30 | RISC-V Laptops, RISC-V Android Devices (poster), RISC-V Network-Attached Storage (NAS), Milk-V Dev boards and RISC-V Fedora and Casa OS for NAS | Fedora Community and PLCT Lab (Programming Languages and Compilation Technologies Lab), Shanghai and Wuhan, China | |

8 | 10:30- 16:30 | TBD | TBD | |

9 | 10:30- 16:30 | JASA Chip Demo | Masataka Kobayashi | Japan Embedded Systems Technology Association (JASA) Technology Headquarters Hardware Committee RISC-V Working Group (Hitachi Industry & Control Solutions, Ltd.) | |

10 | 10:30- 16:30 | RISC-V Processor IP Security Demo | University of Electro Communication | |

11 | 10:30- 16:30 | TBD | TBD |

⑤ RISC-V research and Open Silicon

August 1, 2024 13:00-

Moderator: DTS Insight Co., Ltd.

Product Solutions Division

Sales Department, Sales Division 1

Kuriya Atsushi

The lecture name, lecture content and time are provisional and subject to change depending on the situation.

| Time | du-ra-tion | Lang | Presentation Topic | Presenter | Affiliation (click for details) | Materials |

|---|---|---|---|---|---|

11:45- | 25 min | JE | Reception and Admission: {Press Business Card Exchange Event} (Invitation Only) | MC: TBD | |

12:10- | 5 min | JE | Welcome Remark: {Press Business Card Exchange Event} (Invitation Only) | MC: TBD | |

12:15- | 30 min | JE | Socializing: {Press Business Card Exchange Event} (Invitation Only) | MC: TBD | |

12:45- | 5 min | JE | Closing Remarks: {Press Business Card Exchange Event} (Invitation Only) | MC: TBD | |

12:50- | 10 min | JE | Opening, Cleanup, and Changeover: {Press Business Card Exchange Event} (Invitation Only) | MC: TBD | |

13:00- | 10 min | E | Master of Ceremony’s Words of Welcome | Kuriya Atsushi | DTS Insights | |

| 13:15- 13:35 | 20 min | J | JASA RISC-V Chip Project | Tomohisa Kohiyama (Hitachi Industrial Equipment Systems Co., Ltd.) | Technical Headquarters Hardware Committee RISC-V Working Group Chief, Embedded Systems Technology Association (JASA) | – |

13:40- | 20 min | J | ISHI-Kai Open Silicon Activities and Invitation to Small Scale Chip Tapeout Opportunities: ISHI-KAI is a community-driven project that promotes open-source Process Design Kits (PDK) and Electronic Design Automation (EDA) tools. The initiative focuses on collaborative semiconductor design, bringing together novice designers to create individual analog circuits like inverters and operational amplifiers using tools such as xschem and klayout. These individual projects are then integrated into a single layout for fabrication. | Noritsuna Imamura | ISHI-KAi | – |

| 14:00- 14:20 | 20 min | NA | 20 Minute Reseating | Bio Break | – | – |

| 14:20– 14:40 | 20 min | E | Linux on RISC-V Software Ecosystem: (1) The status of Fedora on RISC-V including the repo status and software supported RISC-V dev boards (5 min) e.g. firefox, libreoffice, Thunderbird, chromium, (2) Providing the status of current Firmware (OpenSBI/UEFI/uboot) and the kernel status on RISC-V software ecosystem (5 min), (3) Status for other Linux distros on RISC-V , like Arch-linux, Gentoo(5min) | Wei Fu | RISC-V Ambassador @ RISC-V Foundation, Principal Software Engineer @ Platform Enablement, Red Hat Software (Beijing) Co.,Ltd. | – |

| 14:40- 15:00 | 20 min | E | Jiachen Project: RISC-V Prosperity 2036 (甲辰计划): The Jiachen Project: RISC-V Prosperity 2036, also known as 甲辰计划, is an ambitious initiative aimed at significantly advancing the RISC-V ecosystem by the year 2036, the next Year of the Dragon. This project is spearheaded by ASE Labs, PLCT Labs, and Sophgo, among other key players in the RISC-V community | Wei Wu | RISC-V Ambassador @ RISC-V Foundation, The co-founder and project director of PLCT Lab | – |

15:00- | 20 min | E | Canaan Kendryte K230D: The first rv64ilp32 Product for AIoT: The Canaan Kendryte K230D is the first rv64ilp32 product, balancing 64-bit processing advantages with the memory efficiency of 32-bit data types. It is suitable for various smart hardware products, including security-enhanced smart door locks, real-time surveillance home security cameras, and high-performance drones. | Ren Guo, Staff Engineer, linux cpu subsystem, Alibaba (China) | – |

| 15:20- 15:40 | 20 min | – | 20 Minute Reseating | Bio Break | – | – |

| 15:40-16:00 | 20 min | E | Technical Advantages of RISC-V in Shell-Role Type Chips: Shell-Role type chips represent a new chip architecture composed of a fixed logic Shell part and a flexible Role part. Examples of this architecture include the SLMLET in the CREST project and a test chip in the Agile-X project. The SLMLET incorporates an FPGA IP proposed by Kumamoto University in the Role part. Meanwhile, the Agile-X project employs a gate array in this part, enabling the realization of an ASIC configuration quickly and cost-effectively using Minimal Fab. This report compares the features of both examples and discusses their future potential. | Hideharu Amano | Professor, System Design Research Center, Graduate School of Engineering, The University of Tokyo | |

| 16:05- 16:25 | 20 min | E | Scalable AI Hardware Accelerator with Secured Network-on-Chip Framework: This presentation will explain the development of RISC-V-based scalable AI hardware accelerators and secure Network-on-Chip (NoC) frameworks. It will explore architectures and design principles that ensure robust security measures within the NoC while achieving efficient AI computation. Topics include custom extensions leveraging the flexibility of RISC-V, implementation strategies for performance optimization, benchmark results, and security protocols integrating trusted execution environments (TEE) and cryptographic accelerators to safeguard data integrity and confidentiality. The presentation will also share insights from the design automation and evaluation environments at the University of Electro-Communications (UEC) and discuss the technical advantages and future potential of collaborations with domestic and international research institutions and companies. | Hoang-Trong Thuc | Assistant Professor at the University of Electro-Communications (UEC) Cong-Kha Pham | Department of Computer and Network Engineering, The University of Electro-Communications (UEC), Director of the UEC ASEAN Research and Education Center (UAREC) | |

| 16:30- 16:50 | 20 min | E | Activities of AI chip design center: AIST and the University of Tokyo jointly operate an AI chip design center to support the development of semiconductor chips such as AI chips in Japan. From FY2019 to FY2022, the base was constructed as part of the NEDO project, and trial operations were also conducted in parallel. From FY2023, it will be positioned as a shared facility of AIST, and independent operation will begin. In this lecture, we will introduce the LSI design infrastructure and SoC platform that the AI Chip Design Center has developed and provided, as well as the future development of the AI Chip Design Center. | Kunio Uchiyama, Invited Senior Researcher, AI Chip Design Open Innovation Laboratory, Advanced Industrial Science and Technology (AIST) | |

| 16:55- 17:15 | 20 min | E | Kuniyasu Suzaki | Professor , Graduate School of Information Security, Institute of Information Security (IISEC): | Presenter: Kuniyasu Suzaki | Professor , Graduate School of Information Security, Institute of Information Security (IISEC) | |

| 17:15- 18:00 | 45 min | E |

|

⑥ AI, RISC-V research poster presentation

August 1, 2024 10:30-15:30

B2F Foyer

Technology exhibition location: Location No. Please refer to the layout diagram for RISC-V poster exhibition (Foyer).

技術展示場所 :Location No. RISC-V ポスター 展示 (ホワイエ)の配置図を参照ください。

| 枠 | 発表時間 | 言語 | 出展テーマ | 発表者 | 所属機関 | ポスター | |

|---|---|---|---|---|---|---|

| P1 | 11:35- | E | RISC-V System-on-a-Chip with ASCON Cryptography for IoT applications on 180nm CMOS: The number of IoT devices has grown significantly in recent years, and edge computing in IoT is considered a new and growing trend in the technology industry. While cryptography is widely used to enhance the security of IoT devices, it also carries limitations such as resource constraints or latency. Therefore, lightweight cryptography (LWC) balances commensurate resource usage and maintaining security while minimizing system costs. The ASCON stands out among the LWC algorithms as a potential target for implementation and cryptoanalysis. It provides authenticated encryption with associated data (AEAD) and hashing functionalities in many variants, aiming for various applications. In this brief, we present an implementation of ASCON cryptography as a peripheral of a RISC-V System-on-a-Chip (SoC). The ASCON crypto core occupies 1,424 LUTs in FPGA and 17.4kGE in 180nm CMOS technology while achieving 417Gbits/J energy efficiency at a supply voltage of 1.0V and frequency of 2MHz. | Khai-Duy Nguyen (The University of Electro-Communications)Japan, Tuan-Kiet Dang (The University of Electro-Communications)Japan, Binh Kieu-Do-Nguyen (The University of Electro-Communications)Japan, Cong-Kha Pham (The University of Electro-Communications)Japan, Trong-Thuc Hoang (The University of Electro-Communications)Japan | ||

| P2 | 11:35- 15:00 | E | Are we, uh, screwed?: An Overview in RISC-V Vector Extension in 2024: From the instruction design perspective, does RVV have its advantage compared to SIMD, NEC SX, and SIMT under different VLEN and workloads? Processor design in RVV is also negatively influenced by pipeline dependency and long vector handling. | Presenter: Yan Lu | Graduate School of Frontier Sciences, The University of Tokyo (Chiba, Japan), Yangyu Chen | Chongqing University (Chongqing, China), Yang Man | Institute of Computing Technology (Beijing, China), China Academy of Science, Yingwei Zheng | Southern University of Science and Technology (Shenzhen, Guangdong, China) | – | |

| P3 | 11:35- 15:00 | E | Development of a System for Easy Utilization of RISC-V Extensions Using Hypervisor Technology: In RISC-V, modular specifications known as “extensions” are being formulated one after another. However, the hardware implementation has not progressed as expected, leaving many extensions unused and in a state of limbo. | Norimasa Takana | University of Tsukuba,Yoshihiro Oyama | University of Tsukuba | ||

| P4 | 11:35- 15:00 | E | A triple modular redundant RISC-V processor on a Cyclone V FPGA: Under a strong radiation environment such as decommissioning situation of nuclear power plants, radiation-hardened processors are needed for robots and other systems. Currently, space-grade processors are available. However, even if we use such space-grade processors, the radiation tolerance is not sufficient in Fukushima Daiichi Nuclear Power Plant. The life-time of the space grade processors is limited to about 10 hours. So, we introduced triple modular redundancy (TMR) for a RISC-V processor to increase the total-ionizing-dose tolerance. | Masato Isobe | Graduate school of Environmental, life, Natural Science and Technology, Okayama University, Mioru Watanabe | Faculty of Environmental, Life, Natural Science and Technology, Okayama University, Nobuya Watanabe | Faculty of Environmental, Life, Natural Science and Technology, Okayama University | – | |

| P5 | 11:35- 15:00 | Poster Presentation 65 | TBD | – | ||

| P6 | 11:35- 15:00 | Poster Presentation 66 | TBD | – | ||

| P7 | 11:35- 15:00 | Linux Capable RISC-V SoC with OpenXC7 for Educational Purposes: RISC-V softcores are widely available, but most cores capable of running Linux are complex and therefore unsuitable for educational purposes. We want to present QuasiSoC, a 32-bit RISC-V CPU and SoC written in pure Verilog that runs the mainline Linux kernel in MMU and no-MMU modes. The 32-bit no-MMU support has been implemented for the first time and has now been added to the Linux kernel and buildroot upstream. The easy-to-understand code, BRAM-like bus interface, and optional memory management unit make it an optimal choice for educational scenarios. QuasiSoC typically utilizes only 25% of the logic resources in the AMD/Xilinx Artix 7 xc7a35t FPGA with SDRAM, HDMI, and SD card features enabled. Thus, it is compatible with the majority of budget-constrained educational development boards. | Yimin Gu (The University of Tokyo), Xu He (The University of Science and Technology of China), Xingyan Chen (The University of Science and Technology of China), Shicheng Zheng (The University of Science and Technology of China), Jianliang Lu (The University of Science and Technology of China) | |||

| P8 | 11:35- 15:00 | Poster Presentation 68 | TBD | – | ||

| P9 | 11:35- 15:00 | Hardware/Software Co-Design of Thread-enabled RISC-V-based Multicores: Since its inception in 2011, RISC-V has experienced tremendous growth, resulting in numerous free and open-source processors based on its instruction set. RISC-V is increasingly used in various devices like IoT, wearables, and AI, creating a demand for multicore platforms built with RISC-V cores. While combining different RISC-V cores for specific applications seems ideal, it’s challenging because most open cores lack features needed for efficient multicore design. This research proposes a hardware/software co-design solution to overcome these bottlenecks, significantly improving the performance of multicore systems. | Do Nguyen Binh Kieu(The University of Electro-Communications)Japan, | |||

| P10 | 11:35- 15:00 | DynamoRIO for RISC-V: Implementation and Porting Progress: DynamoRIO is a dynamic code transformation system renowned for its versatility in applications such as program analysis, profiling, instrumentation, and more. | Dr. Yang Liu, Precision Logic and Computational Technologies Laboratory (PLCT Lab) , Tsinghua University, Beijing | – | ||

⑦ RISC-V Press Business Card Exchange (Invitation Only)

August 1, 2024 12:00-13:00

Moderator: DTS Insight Co., Ltd.

Product Solutions Division

Sales Department, Sales Division 1

Kuriya Atsushi (scheduled)

| 時間 | 発表時間 | 言語 | プレゼンテーション題名 | 発表者 | 所属機関 | Note | |

|---|---|---|---|---|---|---|

| 12:00 | J | 開場 | – | |||

| 12:10-12:15 | J | 歓迎の挨拶 | TBD | — | ||

| 12:15-12:55 | J | 歓談 | TBD | |||

| 12:55-13:00 | J | 閉会 | – | |||

⑧ RISC-V related Japanese publications

Click on the book photo to purchase

Digital Circuit Design and Computer Architecture [RISC-V Edition] (00) Large book – June 7, 2022

Computer Architecture [6th Edition] Quantitative Approach Paperback – 2019/9/25 ¥8,800

Learning RISC-V and Chisel: Building your own CPU for the first time – The first step towards implementing a custom CPU using an open source instruction set Paperback (soft cover) – 2021/8/25 ¥3,520

A must-read book for those who want to start Chisel Paperback – August 28, 2020 ¥2,750

Getting Started with FPGA Electronics with Chisel Paperback – 2022/1/9 ¥2,750

RISC-V related Japanese publications

ideo