| Accelerate Silicon Research with Google Cloud Platform | Demo PDF Demo Video |

Booth Attendant: Google, Developer Relations Engineer | Using the RAD Lab module for Silicon, we ran hundreds of concurrent experiments on Google Cloud to explore the area and density parameter space for a RISC-V core design. Between each batch of experiments we reported the estimated total power consumption to the Vertex AI Vizier service, allowing it to suggest new parameters that quickly converge toward the best power metrics for this design.

D: PL_TARGET_DENSITY | |

| Comprehensive Solutions for RISC-V Architecture form Siemens EDA | Demo introduction site Demo Video |

Booth Booth Attendant: Yuri Ellison | Marketing Program Manager, Siemens EDA (Japan)

|

Siemens EDA offers comprehensive RISC-V solutions including RISC-V integrity verification solution that apply formal verification methodology, DFT solution for silicon debugging and bring-up, and high-level design solution rationing for shift-left in the design cycle, as well as RTOS, middle-ware, IP, tools, and services to enable jump-starting embedded system development. | |

| SiFive Update 2022 Spring | Demo Info |

|

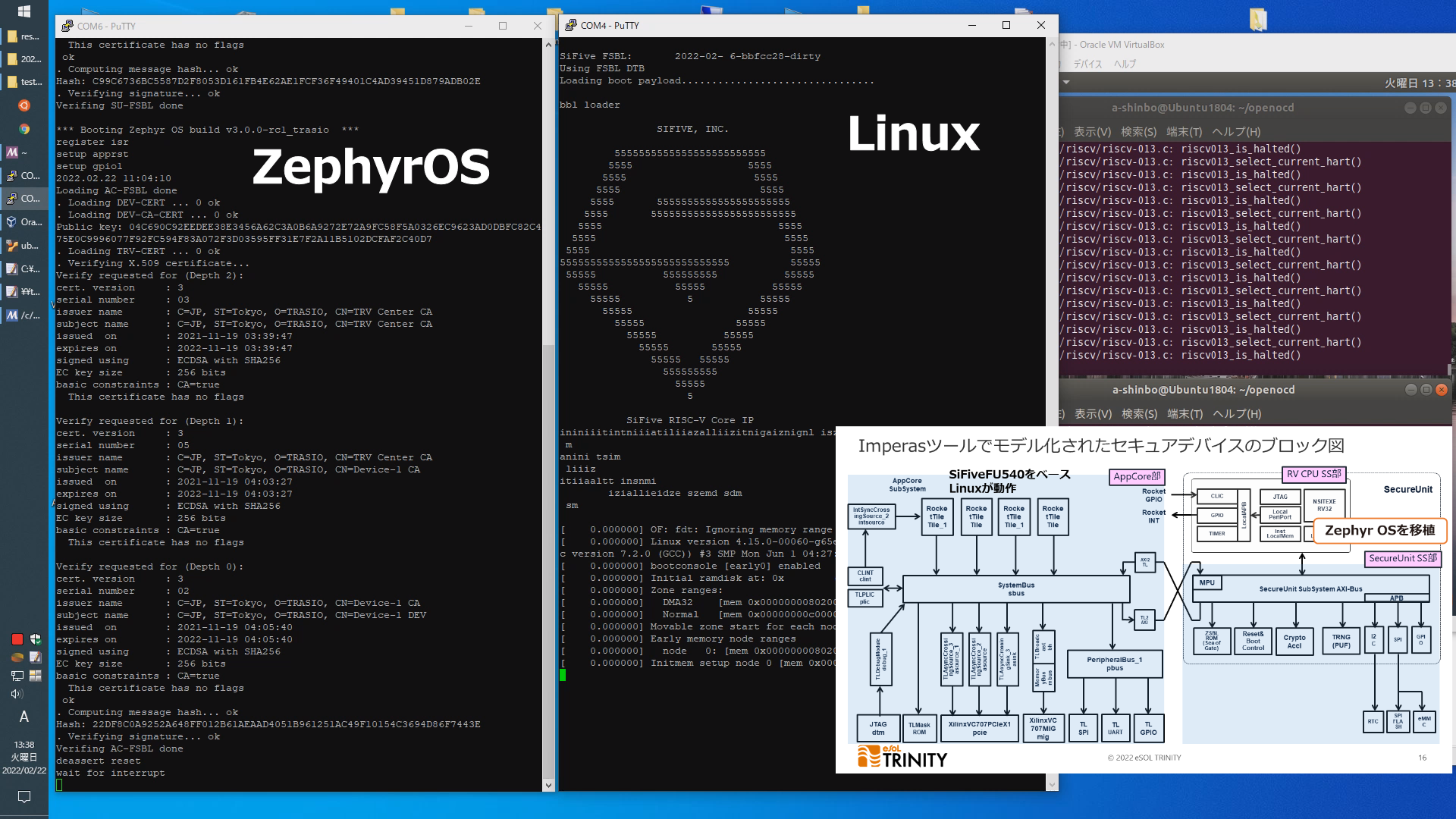

| Imperas RISC-V virtual prototype booting Zephyr OS and running applications. | Demo Video |

Booth Attendant: |  Imperas is the leader in RISC-V simulation solutions. For RISC-V software development the Imperas technology for virtual platforms allows the development of software before hardware is available. The VAP (Verification, Analysis and Profiling) tools support the separation of running activities to show the low-level firmware, OS processes and application code. In addition, for RISC-V further optimization can be explored with the analysis of custom instructions. | |

|

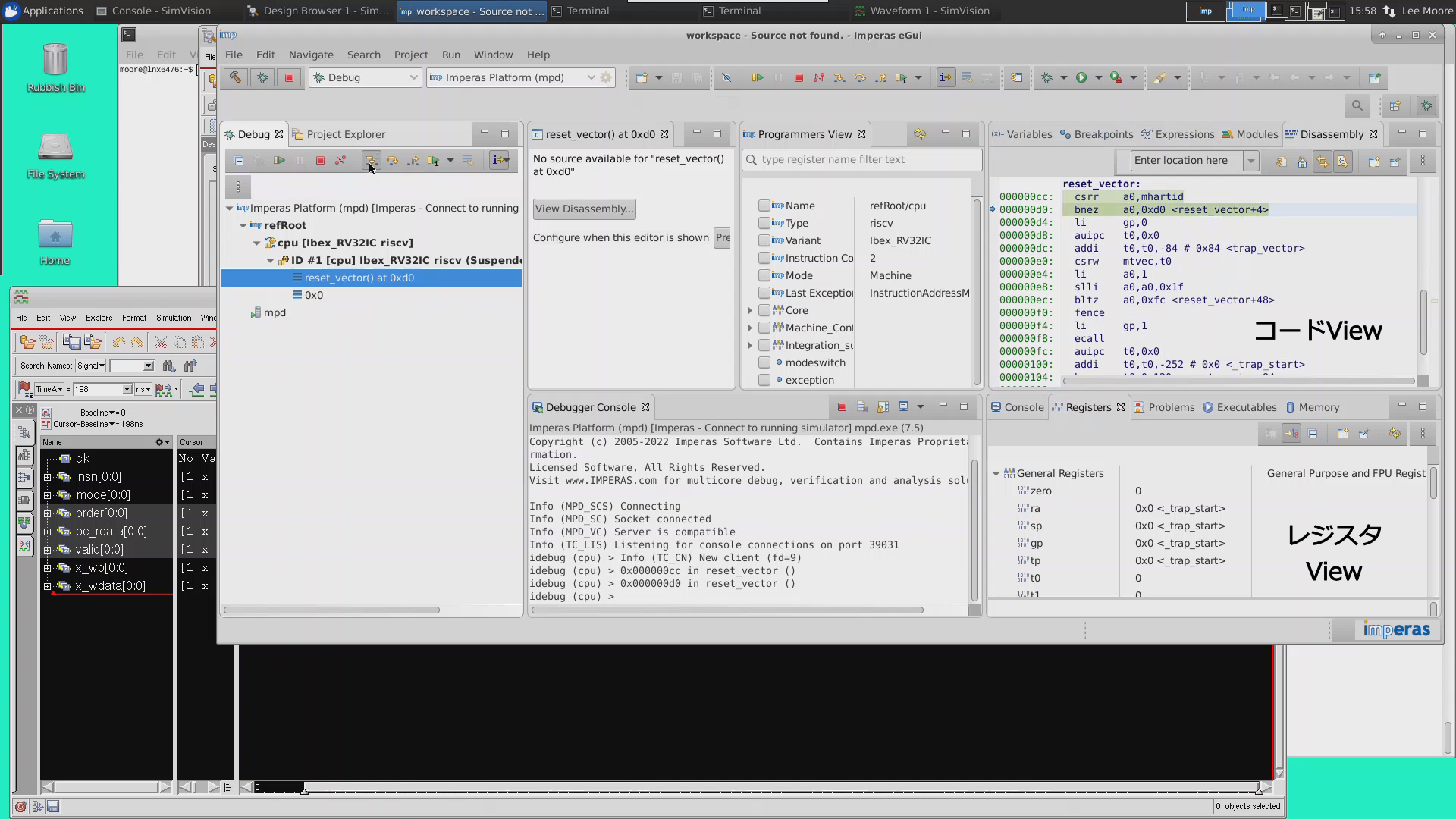

ImperasDV for RISC-V processor hardware design verification. | Demo Video |

Booth Attendant: Shuzo Tanaka VP & Director Engineering Department eSOL Trinity Co., Ltd. |  Imperas is the leader in RISC-V simulation solutions. For RISC-V processor DV the ‘step-and-compare’ methodology verifies the core RTL against a high-quality reference including asynchronous events and debug operations. | |

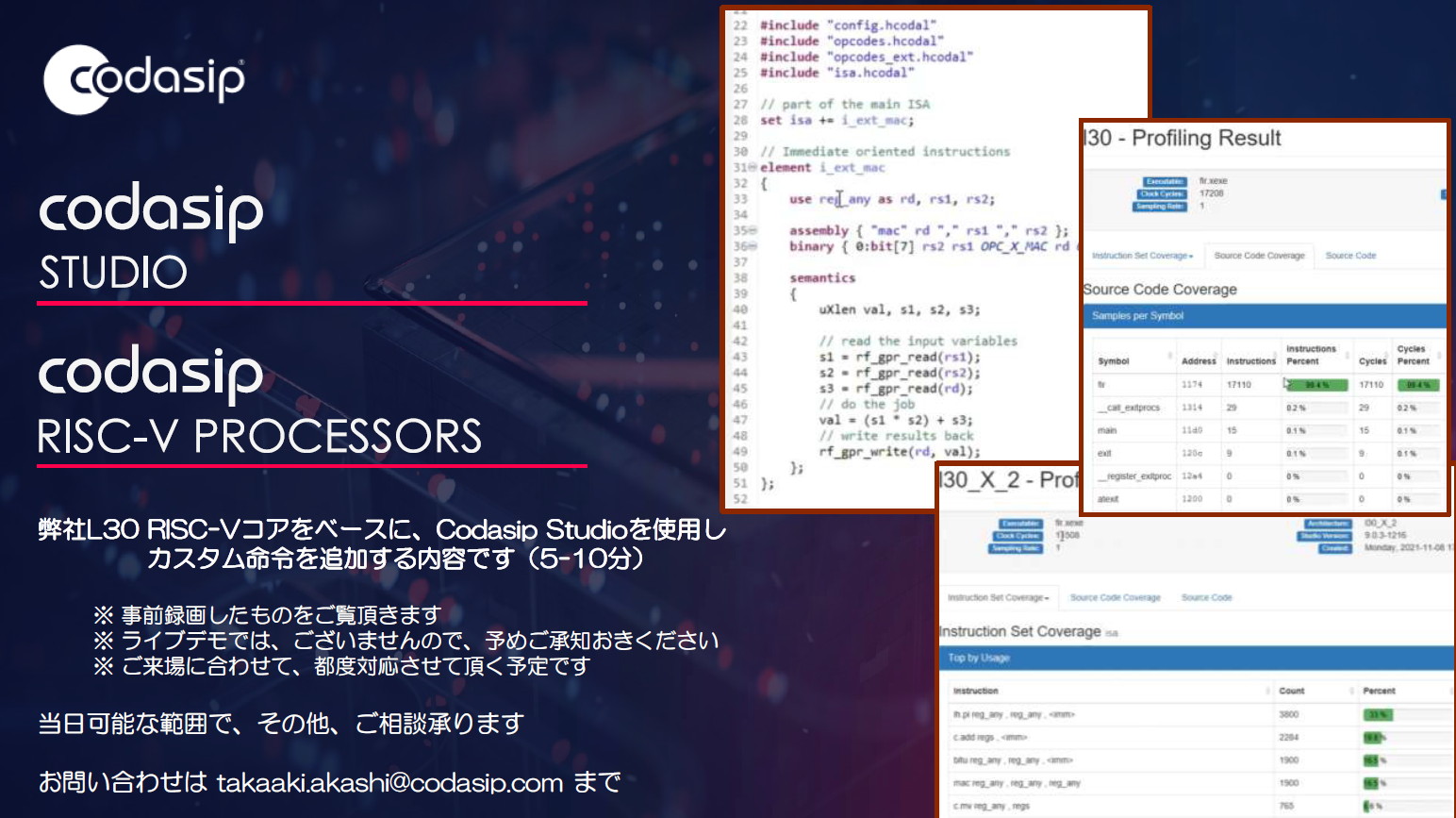

| RISC-V custom instruction addition using Codasip Studio | Demo PDF Demo Video |

Booth Attendant:Takaaki Akashi | Japan Country Manager, Codasip (Japan) | Based on our L30 RISC-V core, it is the content to add custom instructions using Codasip Studio (5-10 minutes) * We will respond each time you visit us.* Please see the pre-recorded version. Please note that this is not a live demo.* You can select Japanese for YouTube video with subtitles.  | |

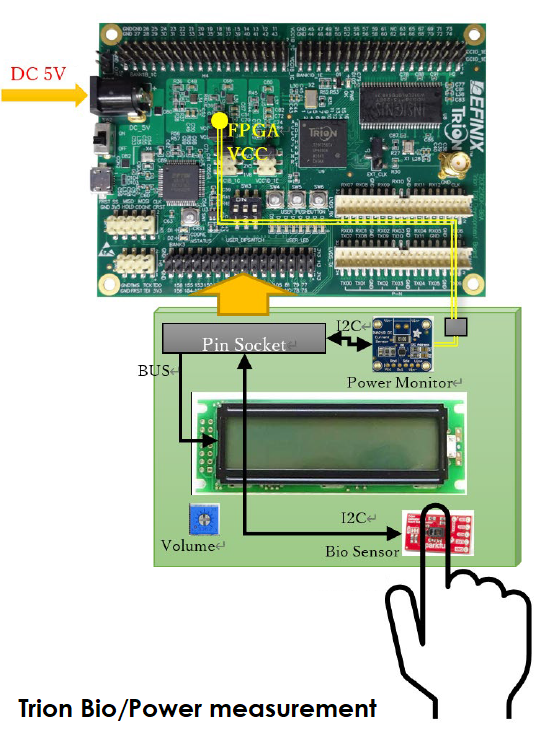

| Trion / Titanium FPGAs Live Demo (Trion / Titanium FPGA ライブデモ) | Demo PDF JP Demo PDF EN |

|

Runs the Efinix Sapphire RISC-V and UNO Labo. 1-stage RISC-V on a Trion FPGA to display biometric information and power consumption. Titanium FPGA will be conducting real-time image processing and real-time AI object tracking demos. |

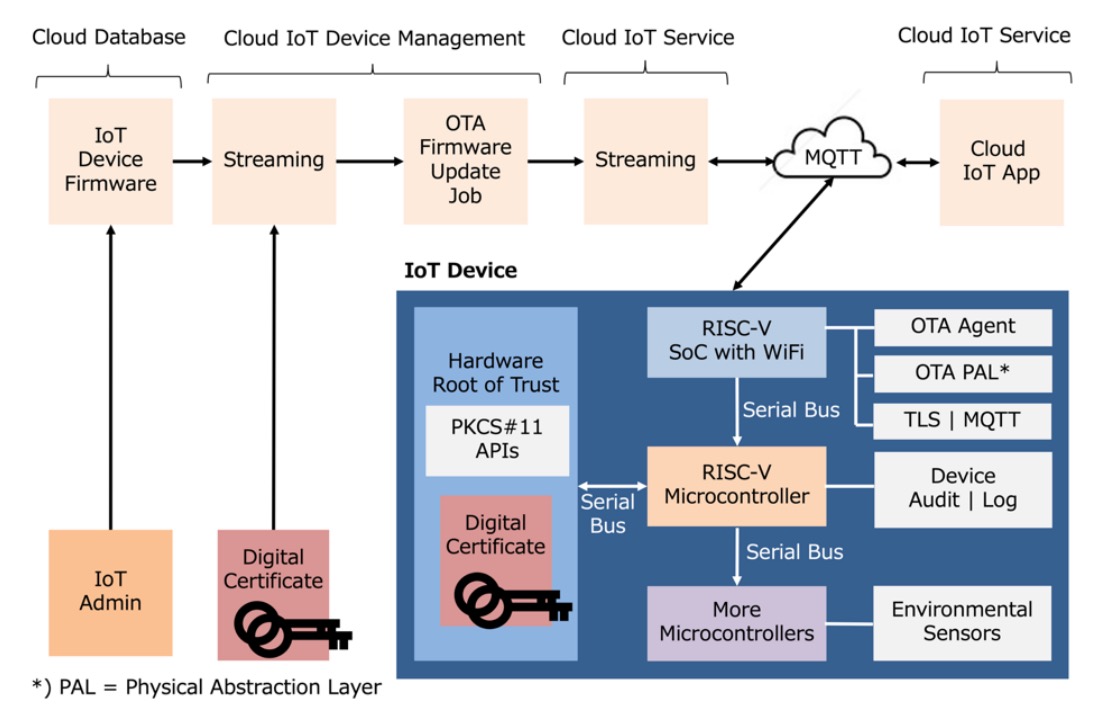

| Marmot with digital caliper and OTA | Demo PDF YouTube Demo Video |

Booth Attendant: |

This demonstration shows a full integration of secure OTA firmware upgrade and digital caliper monitor for an IoT with a 32-bit RISC-V running FreeRTOS on Marmot System. In this demonstration the RISC-V RTOS-based IoT conducts OTA via LTE Mobile SIM leveraging Amazon Web Services (AWS) IoT Core. | |