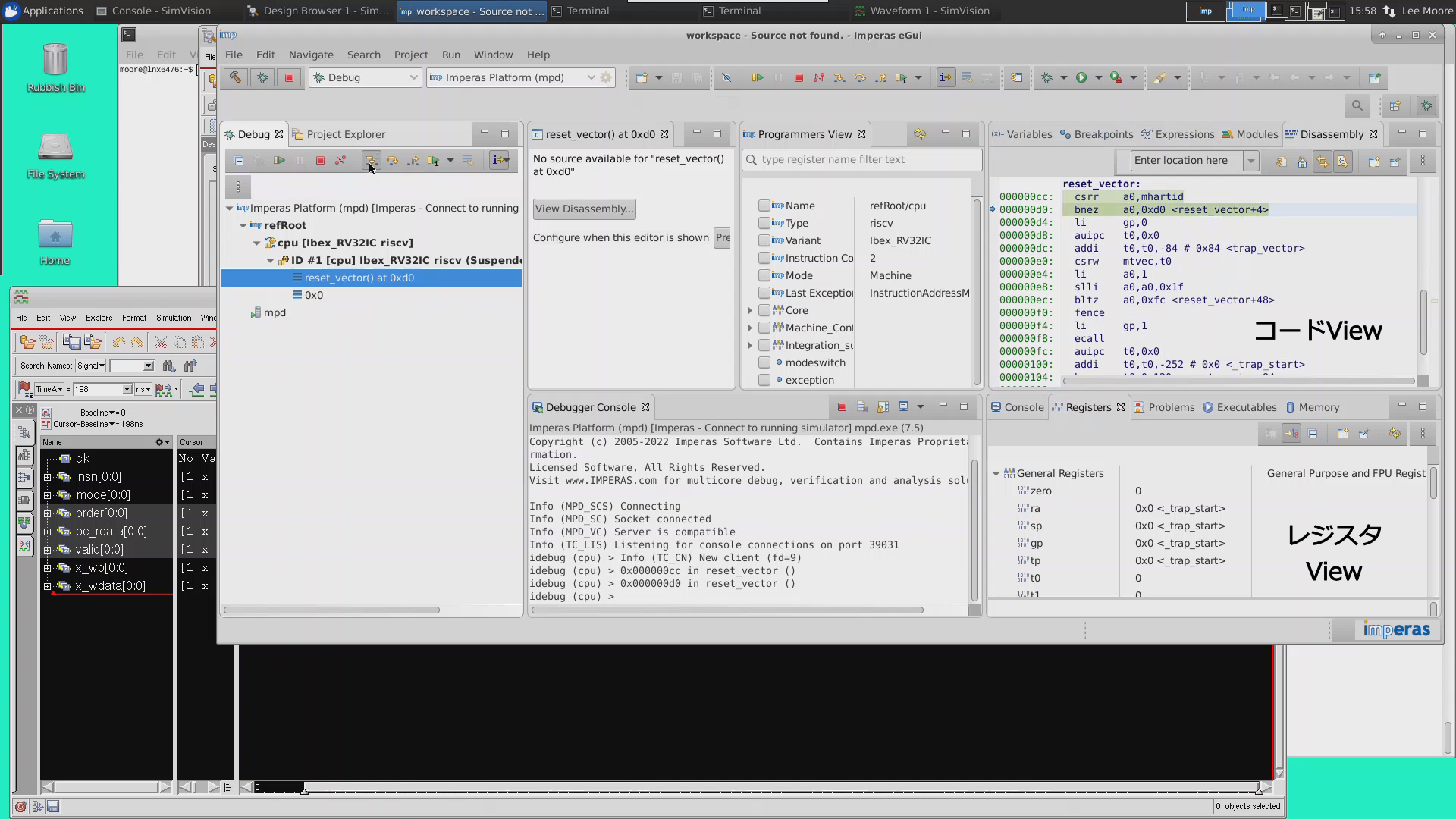

| ImperasDV for RISC-V processor functional design verification | Demo PDF Demo Video | |

Booth Attendant:

|  Imperas is the leader in RISC-V simulation solutions. For RISC-V processor DV the ‘lock-step-compare’ methodology verifies the core RTL against a high-quality reference including asynchronous events and debug operations. ImperasDV natively supports the open standard RVVI (RISC-V Verification Interface) that covers the RISC-V ISA (Instruction Set Architecture) including privileged mode, vector accelerators, multi hart, multi-cores, as well as custom extensions. The Imperas RISC-V Reference model can be encapsulated within a UVM test bench and SystemVerilog environment to give a unified debug experience across the RTL and Reference model to enable efficient issue resolution when a discrepancy is found. | |

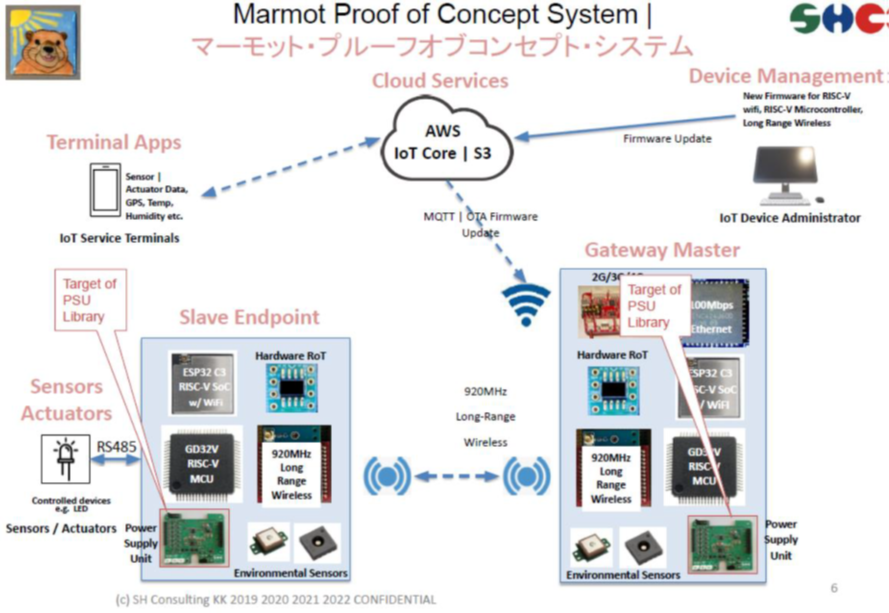

| Marmot System with PSU and Solar power supply | Demo PDF YouTube Demo Video |

Booth Attendant: Hoan Huynh Senior Software Engineer, SH Consulting Vietnam Company Limited |

This demonstration shows a capacity of PSU (Power Supply Unit) for manage power for Marmot System by using Solar panel and battery. By monitor voltage on the Solar and Battery, PSU can decide resource of power supply will be use. In the case good sunshine, PSU use power from Solar to (1) Keep the system work as normal (2) Can charge for battery. Otherwise PSU can use power from battery. | |