Thursday, March 5, 2026

9:00–18:00 Japan Standard Time (UTC+9)

Click here for attendees to register (Peatix)

Click here to submit your proposal (Talks / Posters) — Proposals will undergo a selection process

Click here for the Call for Sponsors: Presentations & Exhibits

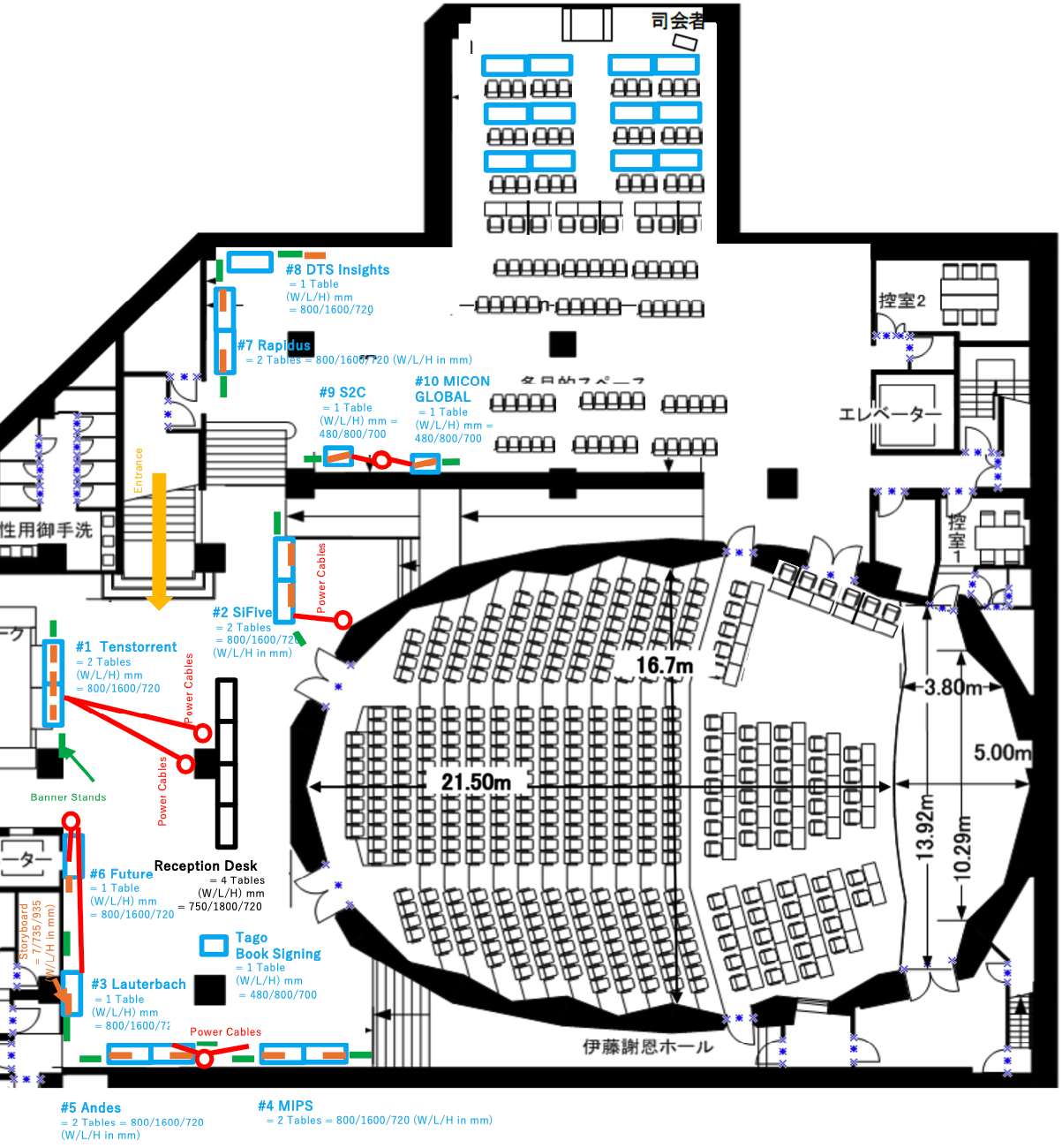

Venue Layout

CONFERFENCE A @Ito Memorial Hall (Click thumbnail to expand the picture)

時間 | 発表題目 | 発表者 |

13:10-13:30 | Welcome Remarks | Makoto Ikeda | Professor at the University of Tokyo A Professor at the University of Tokyo since 2013, he previously served as Associate Professor, Lecturer, and Research Associate, building a distinguished academic career spanning nearly three decades at Japan’s leading research university. His work bridges advanced semiconductor technology, integrated circuit design, and system-level innovation, with a strong emphasis on translating fundamental research into practical societal impact. |

Standard Cell Library Development and Design Infrastructure Establishment for the 2nm Process at Rapidus — Powered by Raads | Koki Tsurusaki | Director, Design Technology Division, Engineering Center, Rapidus Corporation

| |

Open Silicon for the AI Era: Tenstorrent and AI Everywhere | Mamoru Nakano, APAC Region Manager & Japan Country Manager at Tenstorrent | |

SiFive 2nd Generation Intelligence Family Introduction | Yoshihito Kondo | Representative Director, SiFive Japan | |

Software Guided Intelligence for Physical AI Platform Design with RISC-V | Takuya Katayama, MIPS Technical Marketing for Software & Tools | |

15:30-16:00 | Powering the Future of Compute with Andes RISC-V | Frankwell Lin, Chairman & CEO of Andes Technology (Taiwan) |

A Case Study of Custom AI Accelerator Development Using RISC-V | Yuki Miyashita | Future Corporation ki-labs | FPGA Lead | |

TRACE32: Advanced Debug and Trace Solutions for RISC-V | Yuji Mori | Representative Director, Lauterbach Japan Co., Ltd. (Germany) | |

16:40-17:00 | Debugging Environments Supporting RISC-V Development: Tools and Practical Challenges in Real Hardware Development | Tetsuo Asada | DTS Insight Corporation (Japan) |

Closing Remarks: Leveraging RISC-V to Revitalize Japan’s Digital Sector | Takuhiro Nakajo | Associate Professor, Institute of Engineering, Graduate School of Tokyo University of Agriculture and Technology |

CONFERENCE B @Multi-Purpose Space (Click thumbnail to expand the picture)

| Time Pic | Presentation Title | Presenter |

2nd Generation Intelligence Products Technology Explainer | Kunio Uchiyama | Lab Master (Invited Senior Researcher) | AI Chip Design Open Innovation Laboratory | National Institute of Advanced Industrial Science and Technology (AIST) | |

15:10-15:30 | AIST’s Initiatives in Advanced Semiconductor Research and Development | Dr. Meishoku Masahara | National Institute of Advanced Industrial Science and Technology (AIST) |

15:35-15-55 | Accelerating RISC-V Development via Hybrid Co-Emulation and Shift-Left Methodologies | S2C EDA Inc. (Shanghai) |

16:00-16:20 | Specification-accurate customizable RISC-V cores and accelerators | Luca TESTA, PhD – Co-founder and COO | Keysom Inc. |

Development and Performance Evaluation of a RISC-V Based CPU Chiplet at Tenstorrent | Masayuki Kimura | Sr.Staff Engineer | Tenstorrent Japan |

TUTORIAL A @Multi-Purpose Space (Click thumbnail to expand the picture)

| Time Pic | Presentation Title | Presenter |

Accelerating AI via “Architecture” RV23 | Shumpei Kawasaki | Representative Director, RISC-V Association Japan | |

SiFive 2nd Generation Intelligence Products Technology Explainer | John Simpson | Senior Principal Architect | SiFive Inc. | |

Invited Talk: Current Status of the “RISC-V Server SoC Specification” | Vedvyas Shanbhogue | Semiconductor Engineer | Meta (formerly Facebook) | Vice Chair, RISC-V ISA Security Horizontal Technical Committee | Chair, Confidential Computing SIG/TG (RISC-V International) | |

Invited Talk: Trusted Foundations for the AI and Cloud Era — Secure Large-Scale Data Analytics with RISC-V Confidential Computing | Ravi Sahita | Security Engineer | Meta (formerly Facebook) | Vice Chair, RISC-V International Security Horizontal Technical Committee | Chair, Confidential Computing SIG/TG (RISC-V International) | |

| TEE (Trusted Execution Environment) + Attestation + RoT (Root of Trust) on RISC-V Trusted Execution Environments (TEEs), which provide isolated execution environments separate from the normal operating system, are widely utilized across cloud platforms (Intel SGX, TDX, AMD SEV-SNP), smartphones (Arm Cortex-A TrustZone), and embedded systems (Arm Cortex-M TrustZone). Numerous experimental implementations have also been proposed for RISC-V. In recent years, the application of TEE concepts has expanded to include GPUs, and further developments are anticipated. This lecture will introduce these technologies, along with the underlying mechanisms that support TEEs, such as Root of Trust (RoT) and attestation. It will also explain the essential security requirements necessary to build trusted systems. | Kuniyasu Suzaki | Professor, Institute of Information Security

|

Time | Presentation Title | Speaker |

Turing Machine ASIC “Hands-On” TinyTapeout Tutorial — From RTL to GDSII and Fabrication | Munetomo Maruyama |

A physical model of a Turing machine displayed at the “Go Ask Alice” exhibit of the Harvard Collection of Historical Scientific Instruments.

The device visually demonstrates how an abstract Turing machine operates by manipulating symbols on a tape.

Photograph by GabrielF/Wikimedia Commons(CC BY-SA 3.0)

Alan Turing (1912-1954), 1951. Photograph by Elliott & Fry. Courtesy of Wikimedia Commons. Public Domain.