Japan Standard Time (UTC+9)

Bunkyo-ku, Tokyo University of Tokyo Ito Hall

Registration

① Promotion of technologies that enable RISC-V |

| ② Promotion of technologies that RISC-V enables |

| ③ Promotion of RISC-V technologies |

| ④ Promotion of computer security |

| ⑤ Promotion of social implementation through software and electronics |

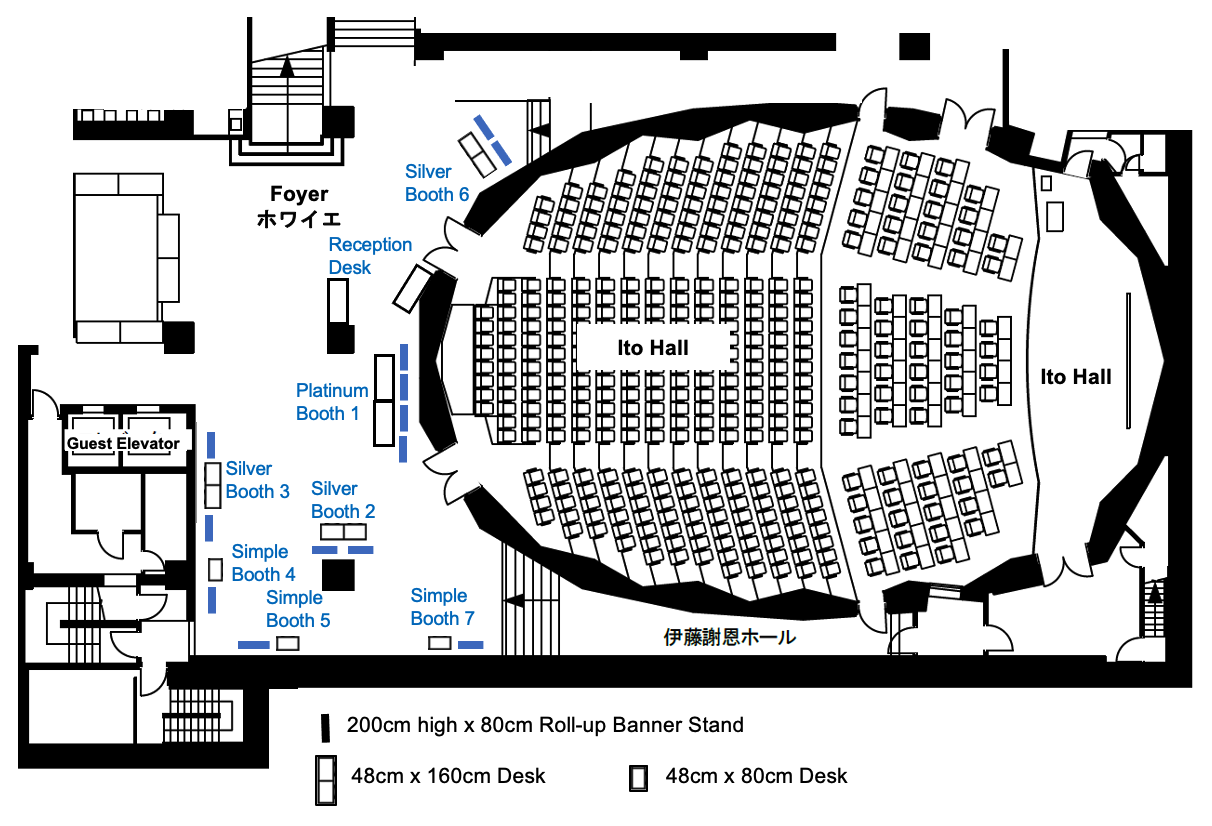

Venue Map

| Icon | Presentation Title | Speaker |

| Japan’s Semiconductor Strategy 2025 — Building the Technologies, Policies, and Industrial Ecosystem to Support Next-Generation Semiconductor Manufacturing | Hisashi Saito | Commerce and Information Policy Bureau, Minister of Economy, Trade and Industry (being arranaged) |

| Caliptra and OpenTitan Tutorial — Architecture and Integration of the Open Root of Trust Firmware Led by Google and Microsoft. | Andrés Lagar-Cavilla | Distinguished Engineer | Google LLC Mountain View, California, USA |

| Panel Discussion: Toward a Standard RISC-V Platform — Understanding and Implementing the RVA23 Linux-Class Profile | RISC-V Alliance Japan |

| Activities of RISC-V Working Group of Japan Embedded Systems Technology Associations (JASA) | RISC-V Working Group: Japan Embedded Systems Technology Associations (JASA) |

| Hands-on Tutorial and Demo: OpenROAD and Tiny Tapeout Workflow | Noritsuna Imamura, ISHI-Kai |

Abstract of the Presentation

| Icon | Presentation Title, Entity and Abstract |

| Japan’s Semiconductor Strategy 2025 by METI |

| Caliptra and OpenTitan Tutorial | Google LLC Mountain View, California, USA |

| Panel Discussion | RISC-V Association Japan |

| Activities of RISC-V Working Group of JASA RISC-V Working Group | Japan Embedded Systems Technology Associations (JASA) | In recent years, the JASA RISC-V Working Group, efforts have focused on promoting understanding of RISC-V and validating implementation technologies. The group first implemented a RISC-V processor on FPGA, followed by a prototype chip fabricated through the Google Shuttle program, on which functional demonstrations and software evaluations were conducted. Currently, the group is developing an original in-house RISC-V chip design, achieving successful demonstrations at each stage. This presentation will highlight these achievements and discuss future development plans. |

| Hands-on Tutorial and Demo: OpenROAD and Tiny Tapeout Workflow | ISHI-Kai This hands-on tutorial uses the open-source EDA tool OpenROAD and the educational Tiny Tapeout platform to guide participants through the fundamental workflow from LSI design to chip fabrication. Participants will gain practical experience with design automation, physical implementation, and verification processes by performing each step interactively. The goal is to provide a hands-on understanding of open-source hardware design methodologies. (Advance registration is recommended.) |

| Icon | Speakers’ Profiles |

| Japan’s Semiconductor Strategy 2025 by METI |

| Caliptra and OpenTitan Tutorial | Google LLC Mountain View, California, USA |

| Panel Discussion | RISC-V Association Japan |

| Activities of RISC-V Working Group of JASA RISC-V Working Group | Japan Embedded Systems Technology Associations (JASA) | In recent years, the JASA RISC-V Working Group, efforts have focused on promoting understanding of RISC-V and validating implementation technologies. The group first implemented a RISC-V processor on FPGA, followed by a prototype chip fabricated through the Google Shuttle program, on which functional demonstrations and software evaluations were conducted. Currently, the group is developing an original in-house RISC-V chip design, achieving successful demonstrations at each stage. This presentation will highlight these achievements and discuss future development plans. |

| Hands-on Tutorial and Demo: OpenROAD and Tiny Tapeout Workflow | ISHI-Kai This hands-on tutorial uses the open-source EDA tool OpenROAD and the educational Tiny Tapeout platform to guide participants through the fundamental workflow from LSI design to chip fabrication. Participants will gain practical experience with design automation, physical implementation, and verification processes by performing each step interactively. The goal is to provide a hands-on understanding of open-source hardware design methodologies. (Advance registration is recommended.) |