# Side-Channel Leakage Evaluation of a RISC V Processor

Chester Rebeiro

Department of Computer Science and Engineering

Indian Institute of Technology Madras, India

chester@cse.iitm.ac.in

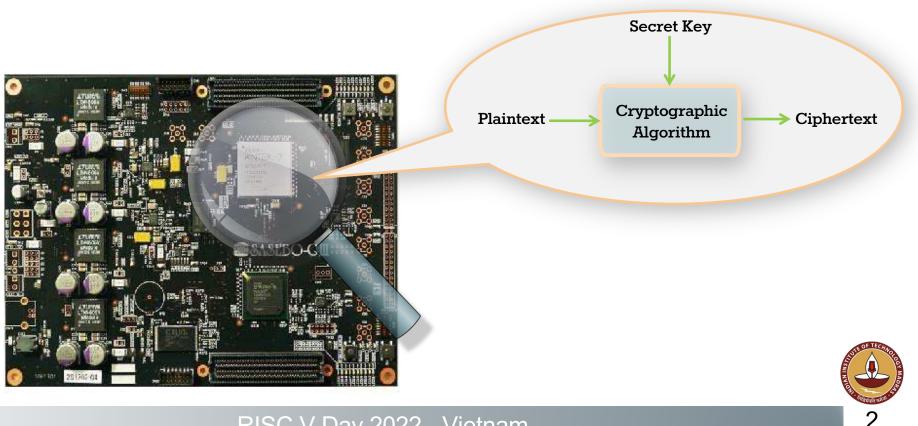

## **Side-Channel Analysis**

- Attacker can extract secrets from an embedded device through physical parameters

- For example: Device's power consumption, electro-magnetic emanation, execution time, and acoustic information

# **Applications of Side-Channel Analysis**

- Firmware reverse engineering

- Recovering passwords

- Mobile app fingerprinting

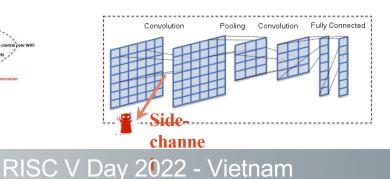

- Predicting input image used in CNN accelerators

Extracting Secret Keys from Yubikey2 Device

App and Website Fingerprinting from Android Mobiles

EM Probing on PIC Microcontroller

### **Power Attack Countermeasures**

### Algorithmic Approach

### Implementation Approach

### Software Solutions

#### Hardware Solutions

## Limitations of Existing Countermeasures

- Algorithm and Implementation solutions:

- Specific to crypto algorithms

- Huge overheads up to 3X

- Software solutions do not prevent all leaks

- EDA based approaches cannot provide guarantees due to noise

### **Computer Architecture Enabled Side-Channel Protection**

Empowering computer architects to handle power side-channel leakages

- Countermeasures incorporated early during the design phase

- Minimize overheads

- Side-channel security for all applications executed in a processor

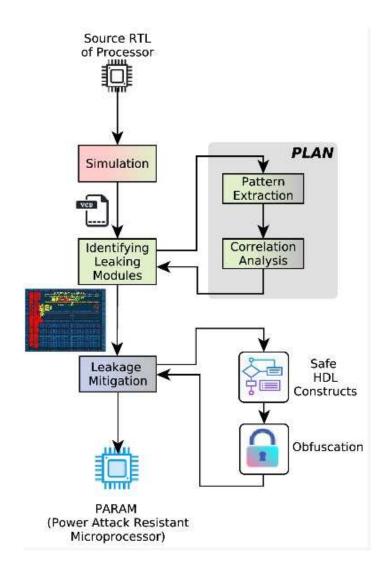

## The Big Picture

Leakage

Identification

2. Adding Countermeasures

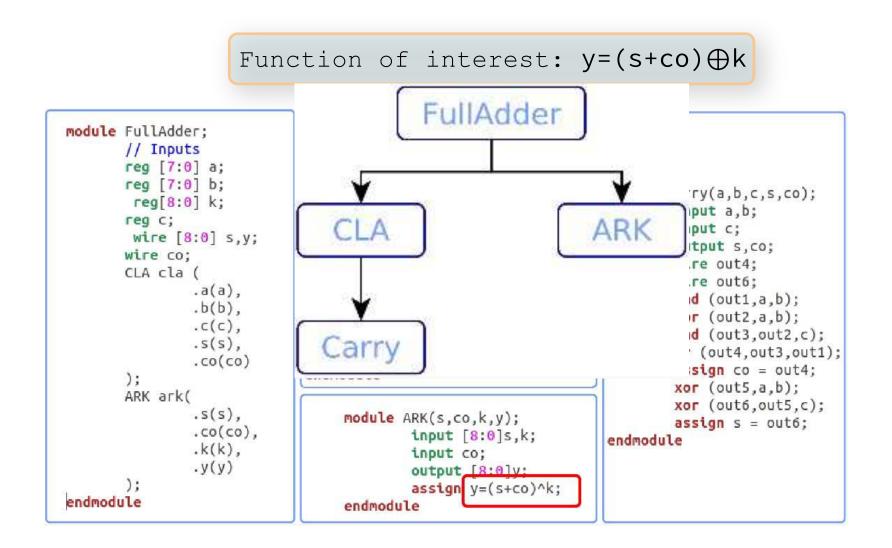

## Leakage Identification: Full Adder

Revenue of the second s

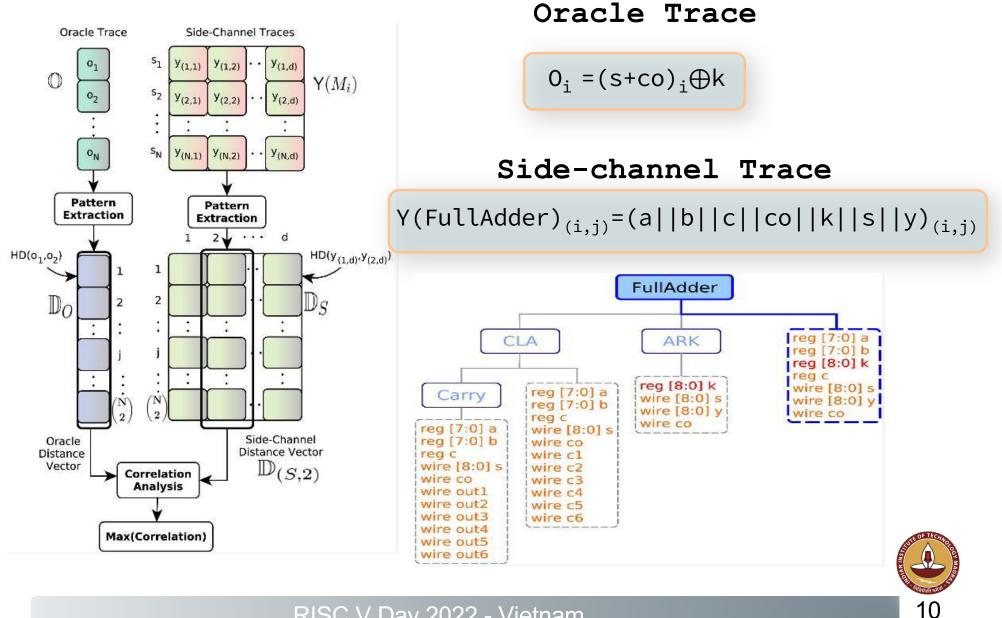

### Leakage Identification: Oracle & Side-channel

### Oracle Trace

- Derived from function of interest by substituting the actual secret value

- For example:  $(s+co) \bigoplus k$

- Contains ground truth information

### Side-channel Trace

- Derived from simulation data by aggregating value of signals belonging to same module

- Contains approximated power consumption information of each module

## PLAN: Power Leakage ANalyzer

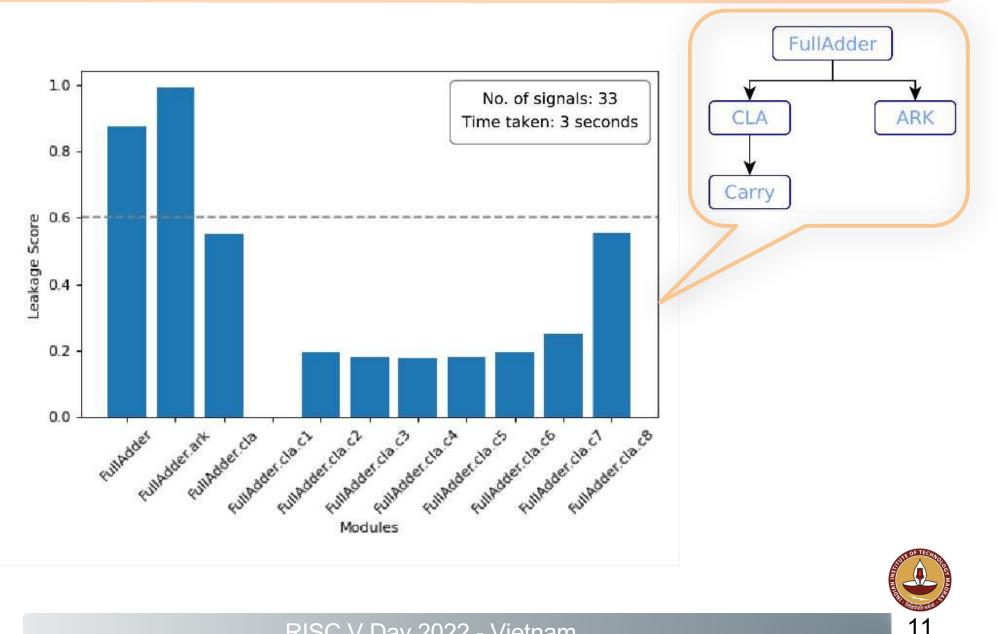

## **Information Leakage: Full Adder**

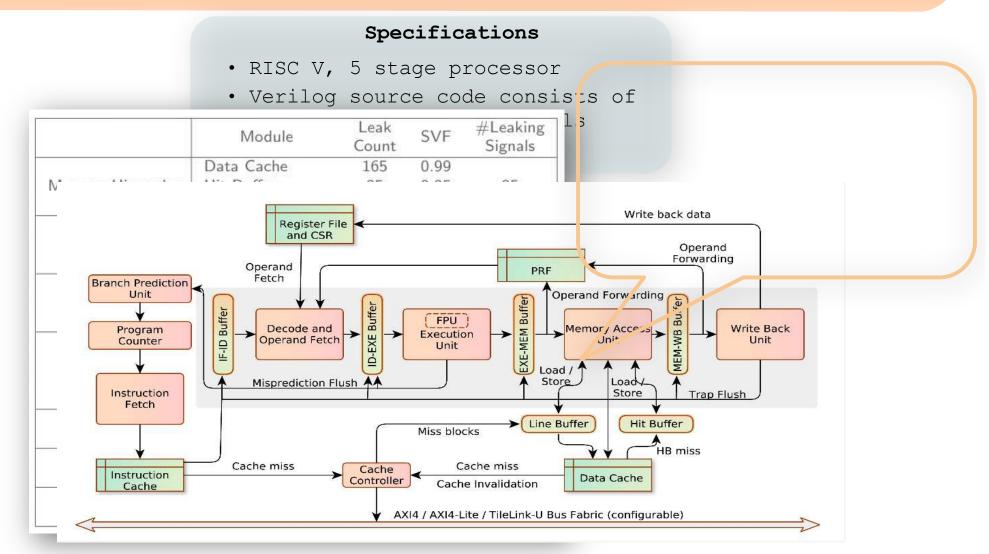

# Leakage in a RISC V Processor: Shakti C<sup>1</sup>

<sup>1</sup>SHAKTI processors: An open-source hardware initiative, VLSID 2016.

12

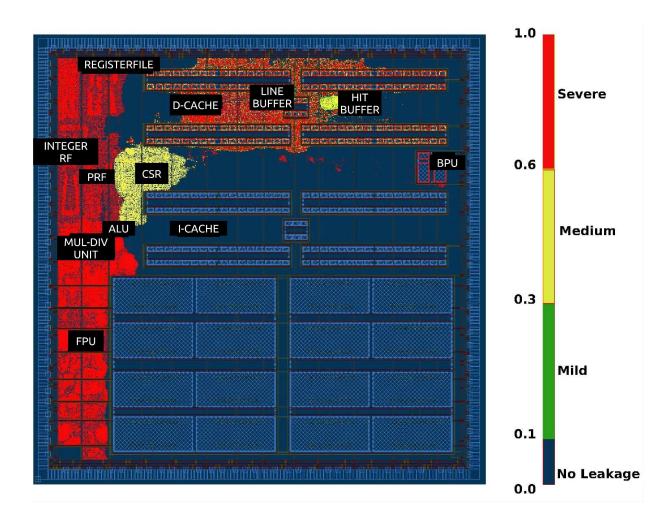

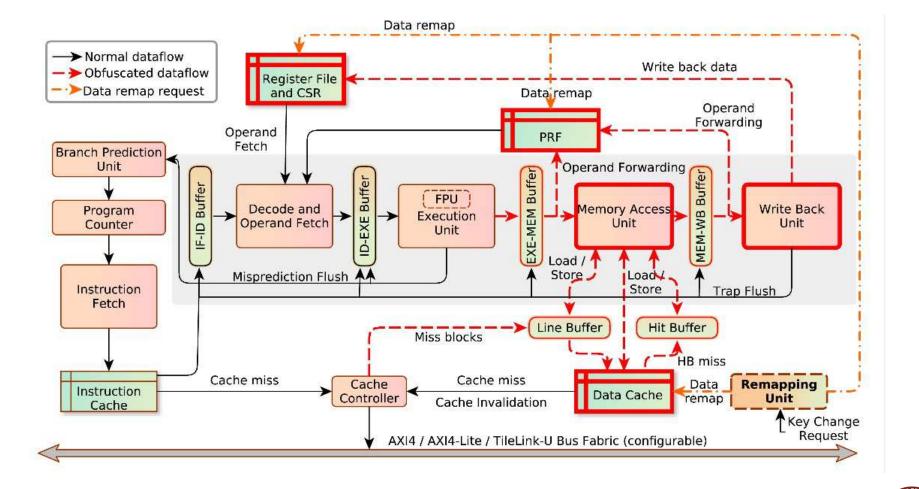

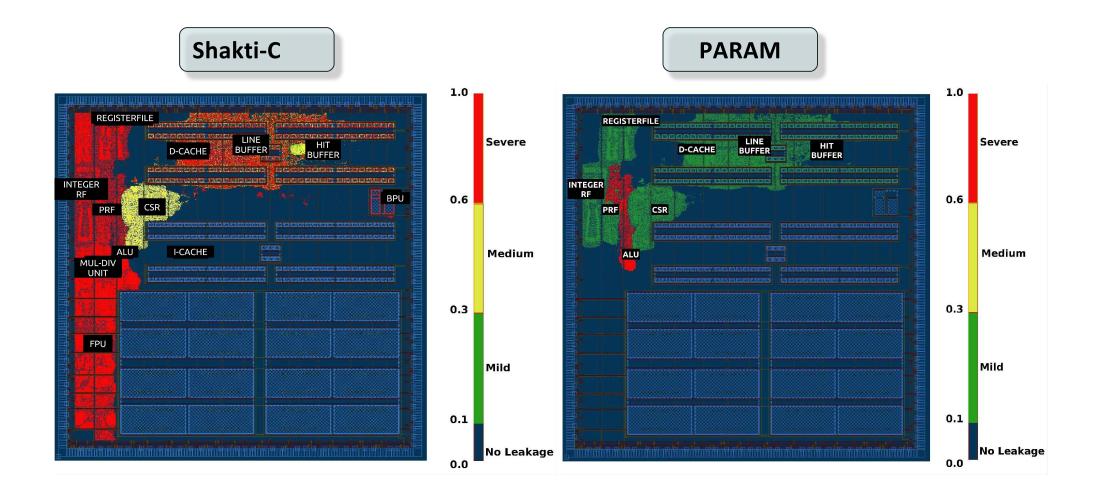

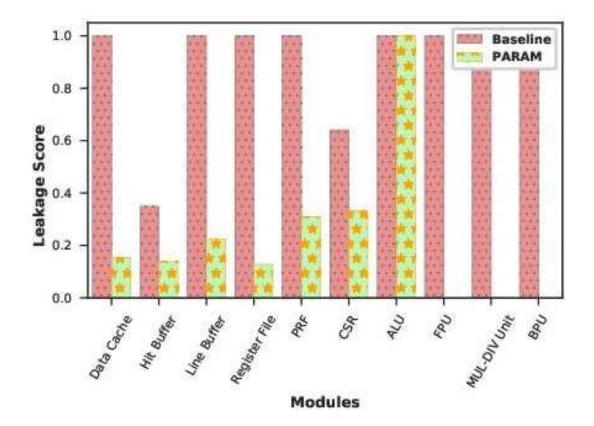

### **Information Leakage: Shakti-C**

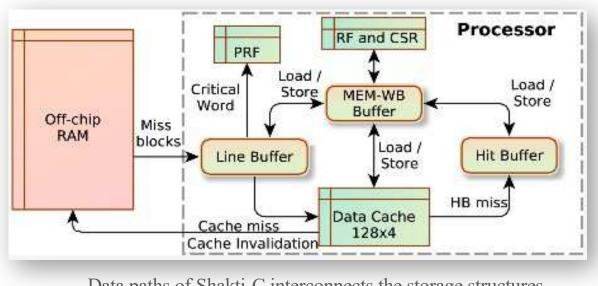

## **Analysis of Memory Units**

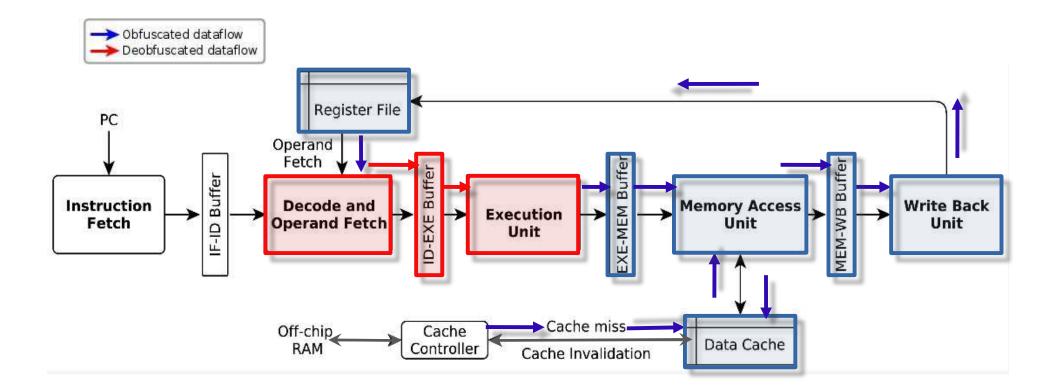

Data paths of Shakti-C interconnects the storage structures

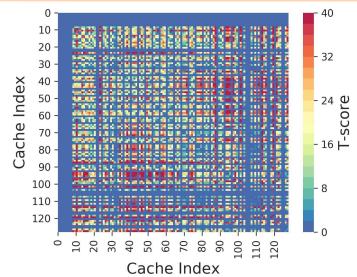

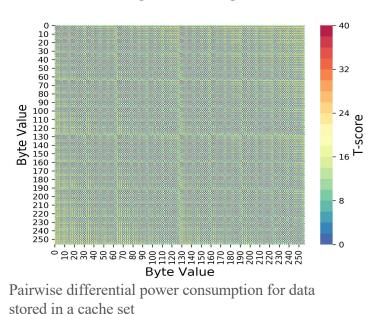

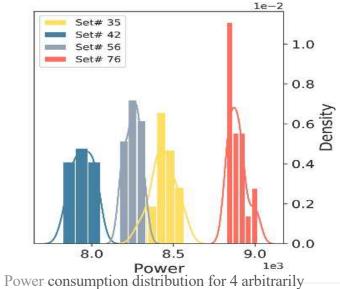

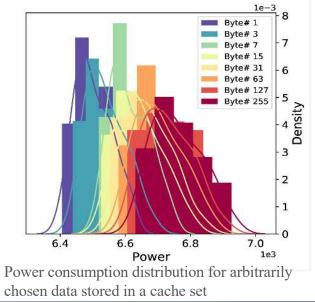

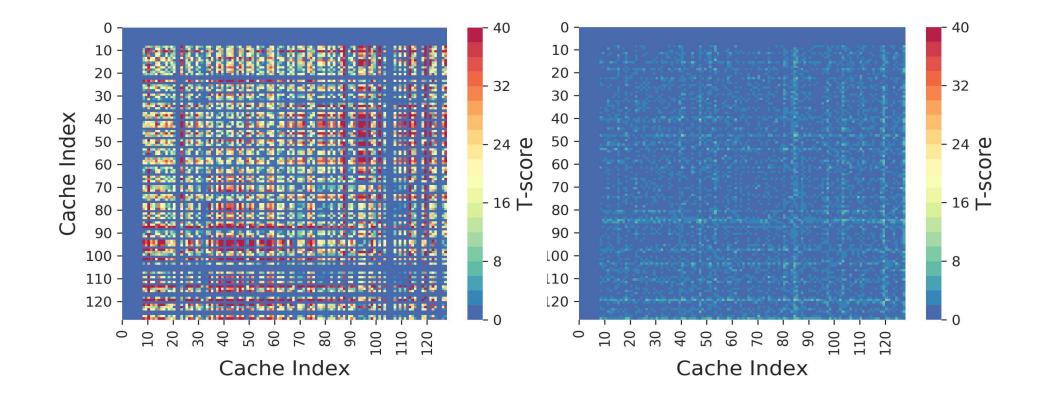

### Data Cache Leakages

Power consumption distribution for 4 arbitrarily chosen cache sets

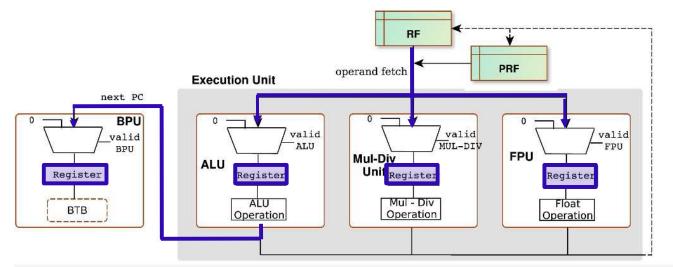

# **Analysis of Leakage in Functional Units**

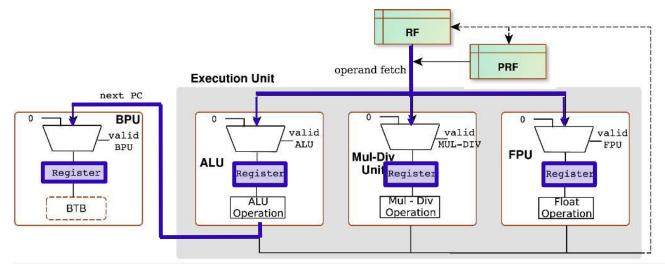

Expected design of Execution Unit in reference platform Shakti-C

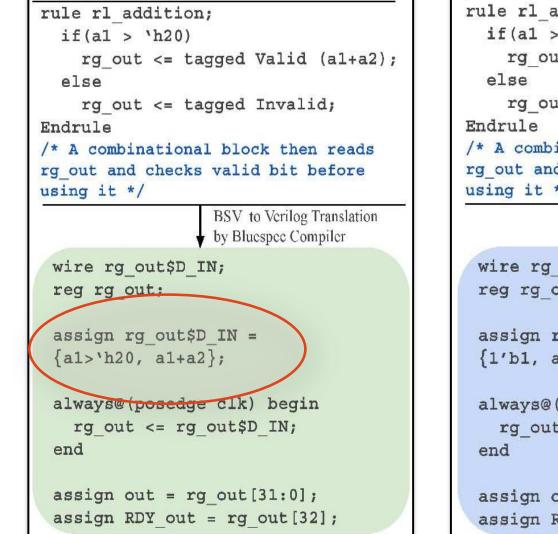

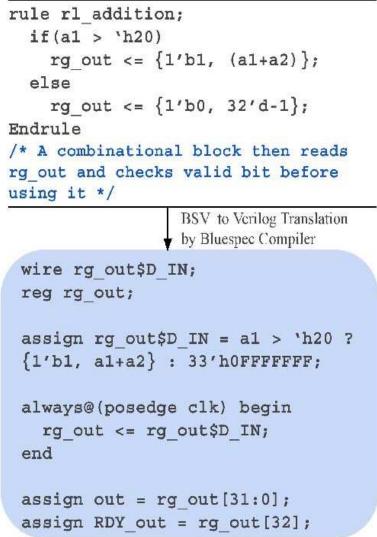

Design after Bluespec compilation

# Fixing the Leakages

1. Modules holding data correlated with the secret

Obfuscate data to break the correlation between data and power consumption

2. Security agnostic EDA translations

Use safe HDL constructs

# **Fixing Correlation with Obfuscation**

### Leakage Reduction in Data Cache

### Fixing Leakage due to Security Agnostic EDA Translation

An illustration of leakages due to EDA translations before and after fix

### PARAM: Power Attack ResistAnt Microprocessor

RISC V Day 2022 - Vietnam

21

## **Information Leakage Plots**

### Results

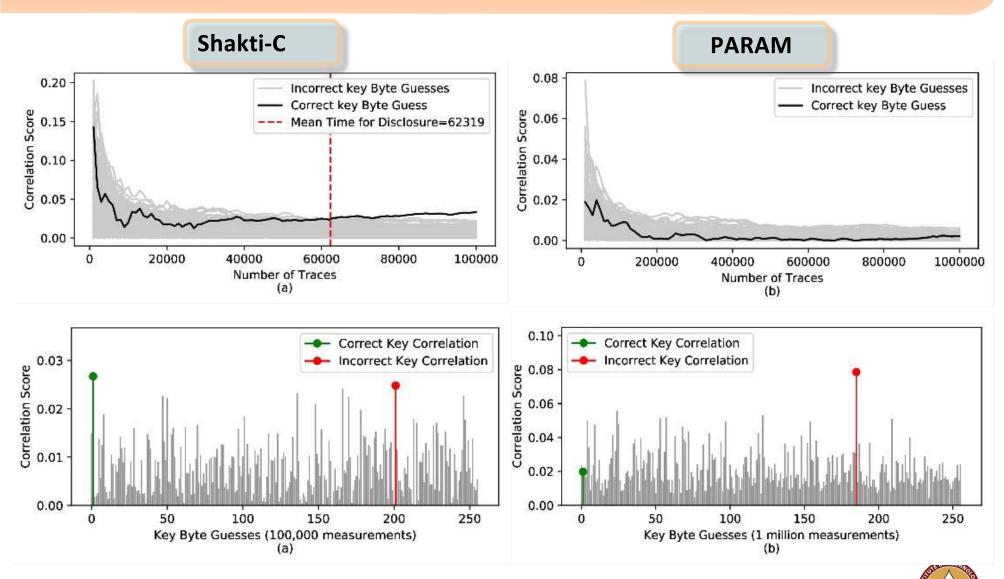

### **Experimental Setup: Differential Power Analysis**

- Processor is instantiated on the SASEBO-GIII FPGA board which has Kintex-7 (C7K160T-1FBG676C) FPGA

- Collect power traces while executing benchmark code on both baseline and PARAM processors

- Compute Mean Time for key Disclosure (MTD) to measure resistance against first-order DPA

## **DPA Results**

DPA results of reference architecture before and after leakage mitigation

25

## **Conclusion and Future works**

- First general purpose processor with built-in security against power attacks

- Low area and performance overheads

- Address ALU and control path leaks

# Questions ? Email: chester@cse.iitm.ac.in