# CONTENT

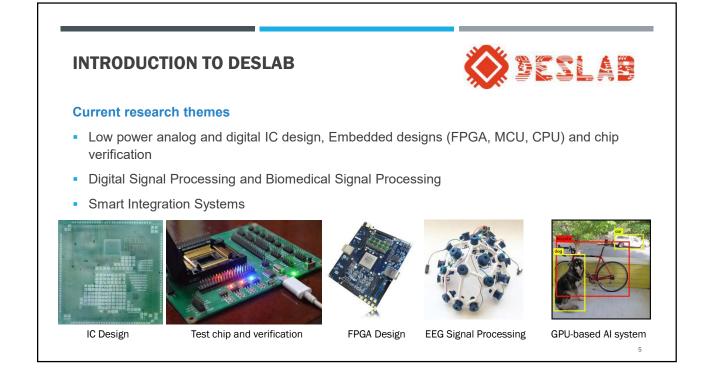

- Introduction to HCMUS, FETEL and DESLAB

- Sharing some RISC-V implementation results

- Ongoing Plans

2

| UN                   | IVERSITY of SCIENC                                                                                | CE, VNUHCM                                                                               |

|----------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| HIS<br>1941          | TORY<br>Division of Indochina College of<br>Science                                               | <ul> <li>Information technology</li> <li>Biology and biotechnology</li> </ul>            |

| 1956                 | Faculty of Science<br>the University of Saigon                                                    | Chemistry120 programsElectronics and telecommunications\$ 68 graduate\$ 52 undergraduate |

| 1977                 | Ho Chi Minh City University                                                                       | Mathematics and computer science                                                         |

| 1996                 | University of Natural Sciences                                                                    | Material science                                                                         |

| 2007<br>until<br>Now | University of Science<br>- Vietnam National University HCMC<br>( <u>http://www.hcmus.edu.vn</u> ) | Physics and engineering physics<br>Environmental science<br>Geology                      |

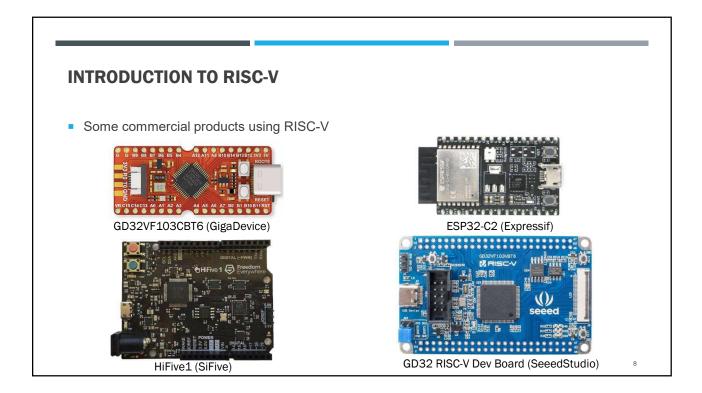

# **INTRODUCTION TO RISC-V**

- RISC-V ISA defines the software interface, not hardware implementation.

- In a RISC-V based SoC, RISC-V compatible core(s) will be used to run software compiled for RISC-V ISA.

- Some open-source RISC-V 32-bit and 64-bit cores:

- RISC-V microcontroller (FE310-G003, GD32VF103, etc).

- Rocketchip (32-bit, 64-bit RISC-V)

- VexRiscV (32-bit, with MMU)

- PicoRV32 (32-bit, very small)

- XuanTie C910 (64-bit, high performance)

- Berkeley Out-of-Order Machine (BOOM) (64-bit RISC-V)

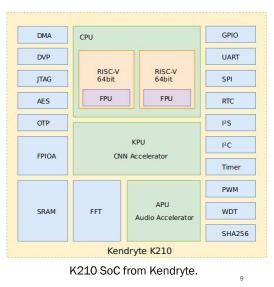

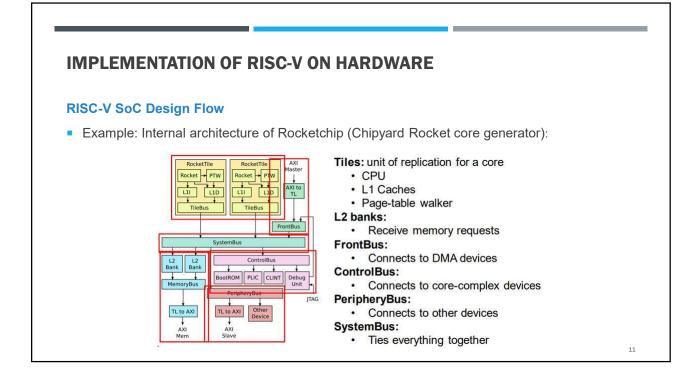

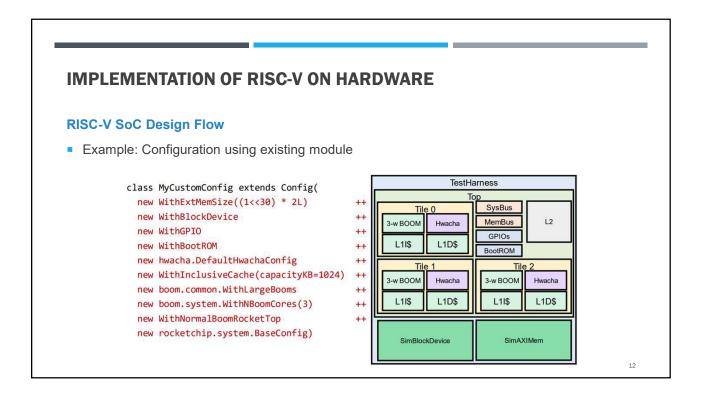

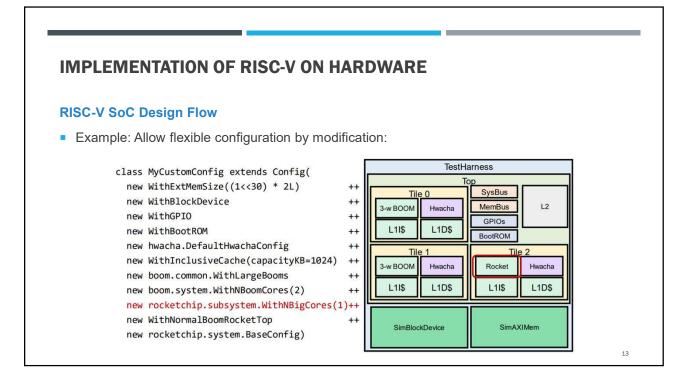

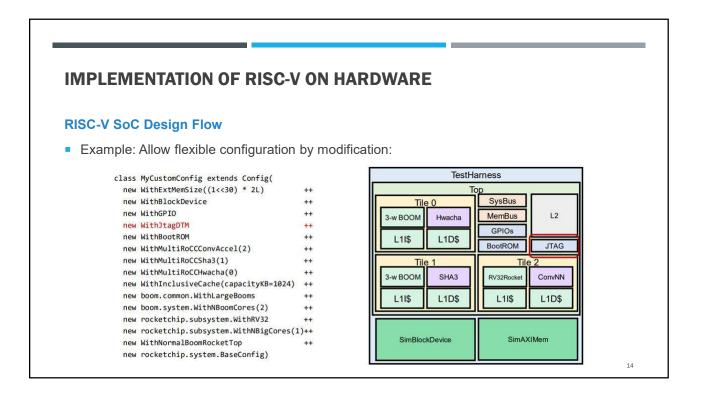

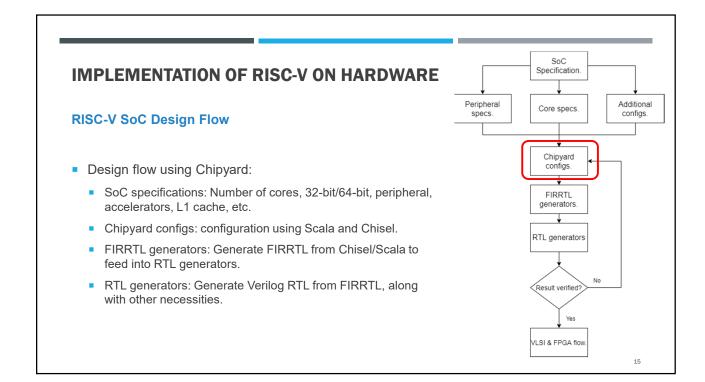

### **RISC-V SoC Design Flow**

- A SoC needs more than just CPU cores!

- Additional IPs needed:

- Peripherals: GPIO, Timer, Accelerators, JTAG, etc.

- Bus(es): AXI, Avalon, TileLink, Wishbone, etc.

- Bus bridge, synchronizer, power management, etc.

- $\rightarrow$  Long time to develop.

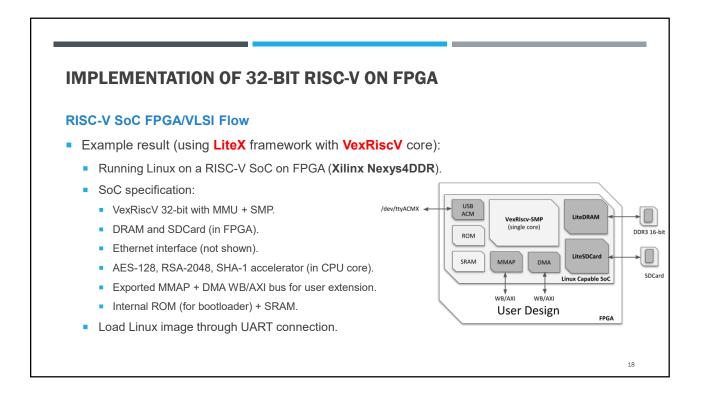

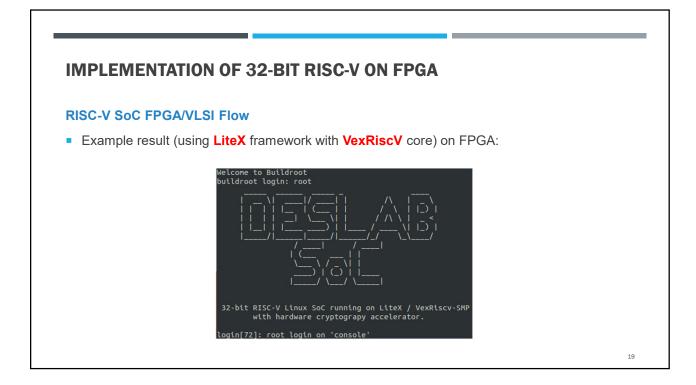

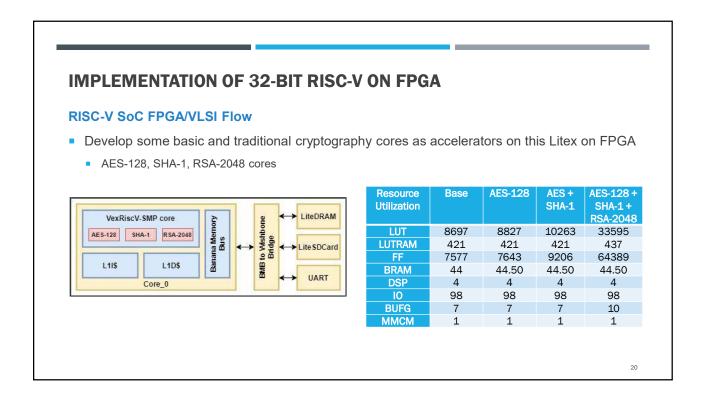

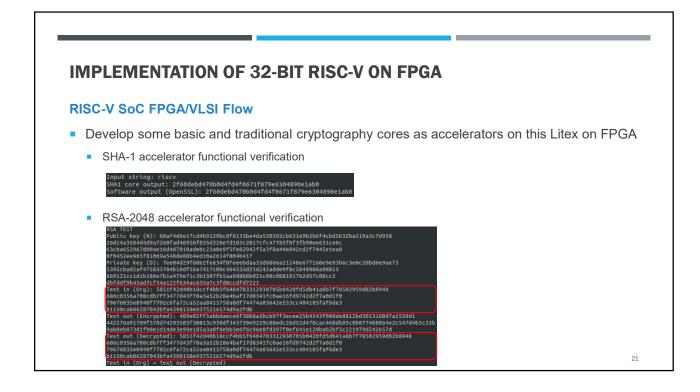

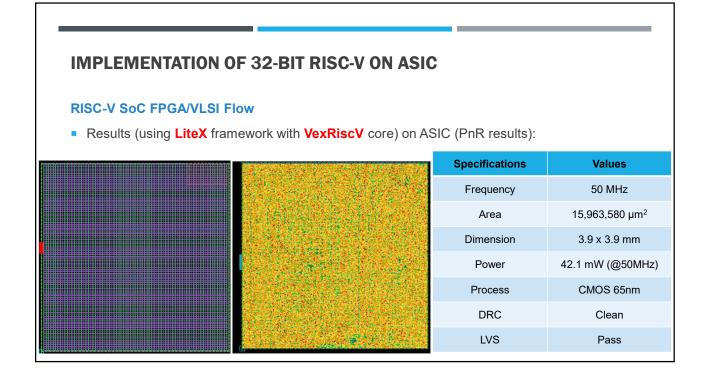

| RISC-V SoC FPC                                                                                                                        |                                                                        | <br>vith <b>VexRiscV</b> core) on                                                                                             | ASIC (PnR results):                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Cell Count<br>Hierarchical Cell Count:<br>Hierarchical Port Count:                                                                    |                                                                        | ,<br>Utilization Ratio:<br>Utilization options:<br>- Area calculation based on:                                               | 0.5078<br>site row of block vlsi                                                                                |

| Leaf Cell Count:<br>Buf/Inv Cell Count:<br>Buf Cell Count:<br>Inv Cell Count:<br>CT Buf/Inv Cell Count:<br>Combinational Cell Count:  | 821304<br>100447<br>24374<br>76073<br>0<br>420496                      | - Categories of objects excluded:<br>Total Area:<br>Total Capacity Area:<br>Total Area of cells:<br>Area of excluded objects: | hard macros macro_keepouts soft_macros io_cells hard_blockage<br>15963580.6290<br>15582653.1330<br>7912595.8449 |

| Sequential Cell Count:<br>Macro Count:                                                                                                | 420490<br>400808<br>0                                                  | <ul> <li>hard_macros</li> <li>macro_keepouts</li> <li>soft_macros</li> <li>io_cells</li> <li>hard_blockages</li> </ul>        | 125309.2223<br>3134.9253<br>0.0000<br>0.0000<br>381527.4960                                                     |

| Area                                                                                                                                  |                                                                        | Utilization of site-rows with:                                                                                                | 0 5070                                                                                                          |

| Combinational Area:<br>Noncombinational Area:<br>Buf/Inv Area:<br>Total Buffer Area:<br>Total Inverter Area:<br>Macro/Black Box Area: | 1663492.92<br>6249090.54<br>477995.35<br>81037.93<br>396957.42<br>0.00 | - Site 'unit':                                                                                                                | 0,5078                                                                                                          |

| Net Area:                                                                                                                             |                                                                        |                                                                                                                               |                                                                                                                 |

| Specifications               | Values             |

|------------------------------|--------------------|

| Frequency                    | 500 MHz            |

| Area                         | 1,384,255 μm²      |

| Dimension                    | 1.17 x 1.17 mm     |

| Power                        | 493.6 mW (@500MHz) |

| Process                      | FinFET 7nm         |

| DRC, Antenna, boundary, ERC  | Clean              |

| LVS                          | Pass               |

| EM and IR drop               | Clean              |

| LEC from RTL to Post-Routing | Design Equal       |

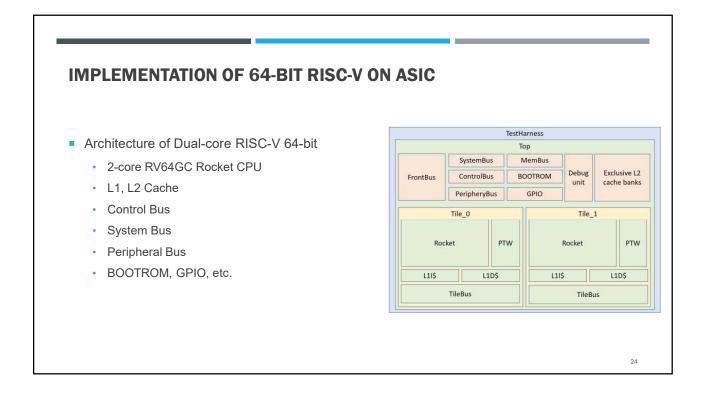

| IMPLEME                     | NTATION OF                  | 64-BIT RISC-V                                                                            | ON ASIC                                                                 |                                                  |

|-----------------------------|-----------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------|

|                             |                             |                                                                                          |                                                                         |                                                  |

|                             |                             |                                                                                          |                                                                         |                                                  |

| ERC and A                   | ntenna Verifica             | ation                                                                                    |                                                                         |                                                  |

|                             |                             |                                                                                          |                                                                         |                                                  |

|                             |                             | TOTAL Result Count = 0 (0)                                                               | RULECHECK RESULTS STATISTICS                                            |                                                  |

|                             |                             | TOTAL Result Count = $\theta$ ( $\theta$ )<br>TOTAL Result Count = $\theta$ ( $\theta$ ) |                                                                         |                                                  |

| ULECHECK MPCdummya Layer or | stside PrBr                 | TOTAL Result Count = $0$ (0)                                                             | RULECHECK pickup.p_to_p TOTAL<br>RULECHECK pickup.n to n TOTAL          | Result Count = $0$ (0)<br>Result Count = $0$ (0) |

|                             |                             | TOTAL Result Count = $\theta$ ( $\theta$ )                                               | RULECHECK pickup.n_to_p TOTAL                                           | Result Count = $0$ ( $0$ )                       |

| ULECHECK BPC_Odrawing_Laye  | r_outside_PrBr              | TOTAL Result Count = $\theta$ ( $\theta$ )<br>TOTAL Result Count = $\theta$ ( $\theta$ ) | RULECHECK mnpg TOTAL                                                    |                                                  |

|                             |                             | TOTAL Result Count = $\theta$ ( $\theta$ )                                               | RULECHECK mppg TOTAL<br>RULECHECK mnpgldd TOTAL                         |                                                  |

|                             |                             | TOTAL Result Count = $0$ (0)                                                             | RULECHECK floating.nxwell float TOTAL                                   |                                                  |

|                             |                             | TOTAL Result Count = $\theta$ ( $\theta$ )                                               | RULECHECK floating.psub TOTAL                                           |                                                  |

| ULECHECK MB1Sdummy_Layer_o  | stside_PrBr                 | TOTAL Result Count = $\theta$ ( $\theta$ )                                               | RULECHECK npvss150                                                      | Result Count = $0$ (0)                           |

|                             |                             | TOTAL Result Count = 0 (0)<br>TOTAL Result Count = 0 (0)                                 | RULECHECK ppvdd150 TOTAL                                                |                                                  |

|                             |                             | TOTAL Result Count = $\theta$ (0)                                                        | RULECHECK ppvdd49 TOTAL                                                 | Result Count = $0$ (0)                           |

|                             |                             |                                                                                          | RULECHECK LV <mark>SD</mark> MY4_DNW_CHECK TOTAL                        |                                                  |

| RULECHECK RESULTS STATE     | STICS (BY CELL)             |                                                                                          | ERC RULECHECK RESULTS STATISTICS (BY                                    |                                                  |

|                             |                             |                                                                                          | •••                                                                     |                                                  |

| SUMMARY                     |                             |                                                                                          | SUMMARY                                                                 |                                                  |

| OTAL CPU Time:              | 1219                        |                                                                                          | TOTAL CPU Time:                                                         | 1511                                             |

| OTAL REAL Time:             | 345                         |                                                                                          | TOTAL CPU TIME:<br>TOTAL REAL Time:                                     | 688                                              |

|                             | ries: 257679057 (1236818036 | 5)                                                                                       | TOTAL Original Layer Geometries:                                        | 246392023 (1045410547)                           |

| OTAL DRC RuleChecks Execute |                             |                                                                                          | TOTAL ERC RuleChecks Executed:<br>OTAL ERC RuleCheck Results Generated: | 13<br>0 (0)                                      |

| OTAL DRC Results Generated  |                             |                                                                                          |                                                                         |                                                  |

##

| IMPLEMENTATION OF 64-BIT RISC-V ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>DRC and LVS Verification</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Sent FLL:       Sent FLL:       Sent FLL:         Sent FLL:       FL:       FL:         Sent FLL:       Sent FLL:       Sent FLL:         Sent FLL:       Sent FLL:       Sen | RULECHECK NPCdummy Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NPC RUMPYdrawing Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NPC Gonzwig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NPC Gonzwig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NPC Gonzwig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NPC Gonzwig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NPC Gonzwig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBC RUMPYdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer outside PrBr       TOTAL Result Count = 0 (0)         RULECHECK NBISdrawig Layer constale PrBr       TOTAL Result Count = 0 (0)         TOTAL REAL CPU Time: |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

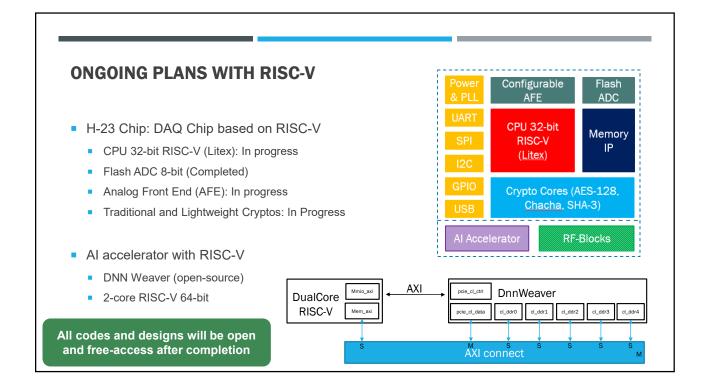

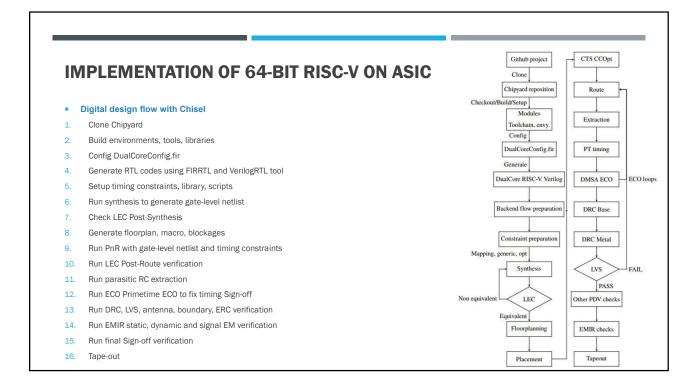

# <section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>