Xifan Tana https://sites.google.com/site/pegaillard on/home

SOFA-CHD (Skywater Opensource FPGAs)

M. Shalan | http://efabless.com

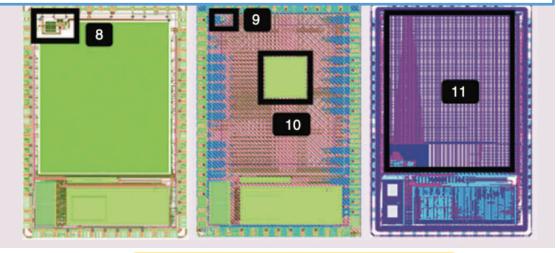

NFive32-Based SoC to validate several open-source projects and IPs.

James Stine | https://vlsiarch.ecen.okstate.edu/

MorphleLogic

Merik Voswinkel |

http://www.fiberhood.org

**SKY130**

A test-wafer for testing Mophle Logic

@ 1.4k

reconfigurable hardware for SKY130.

Caravel\_RISCV\_OSU is an implementation of a single-cycle RISC-V processor inside of the Caravel...

1.8k

SKY130A

Amatuer Radio Satellite Transceiver (SKY130) - Caravel Submission

Chameleon SoC

M. Shalan | http://efabless.com

AHB-Lite based SoC for IBEX

Softshell

Harrison Pham | https://harrisonpham.com/

Multicore MCU for implementing software defined peripherals.

SKY130 @ 1.7k

#### Select

### Open

#### Source

### **Designs**

#### OPEN SOURCE ECOSYSTEM AT WORK

# How do we simplify chip

design? #5

# OK - sounds good so far but ... manufacturing cost \$\$

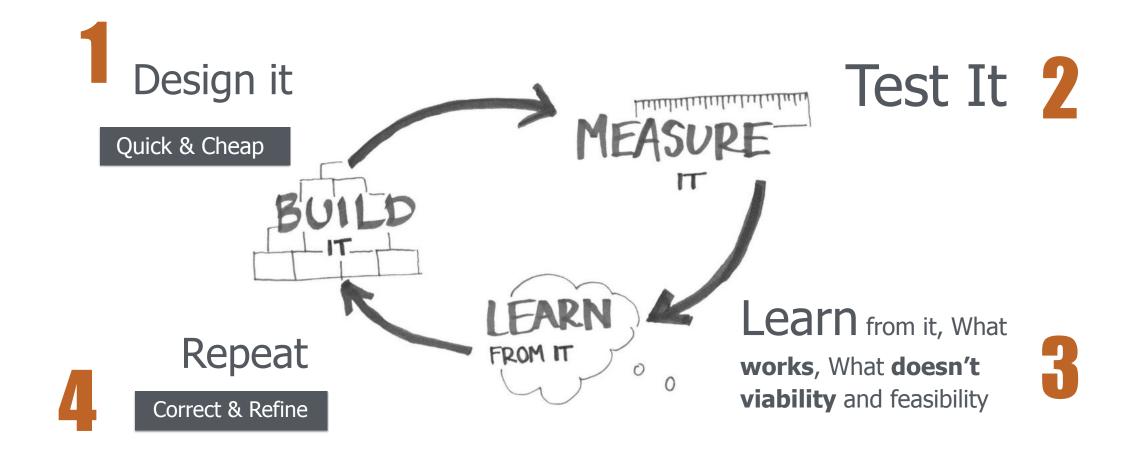

# Enable — Fail fast, learn and repeat

# Enable — Fail fast, learn and repeat

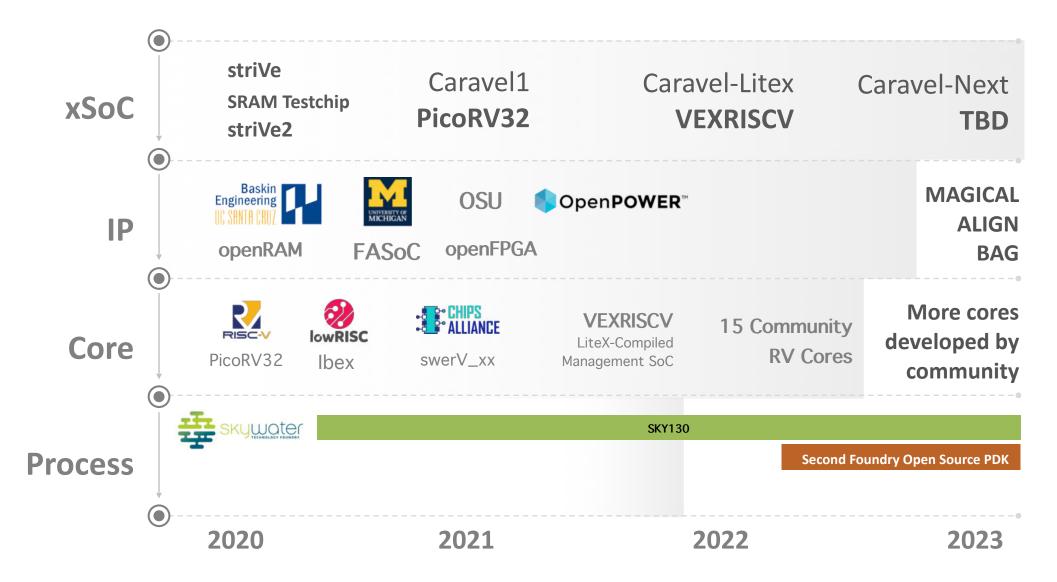

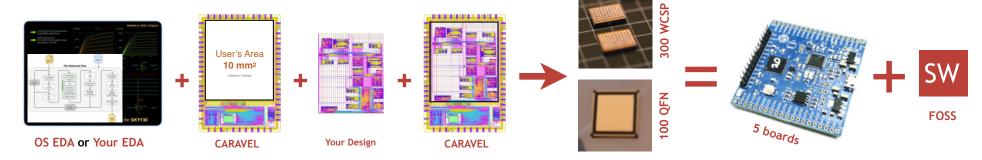

#### **GOOGLE'S OPEN MPW PROGRAM**

- Google is funding 4 manufacturing runs in 2022 minimum of 40 designs each

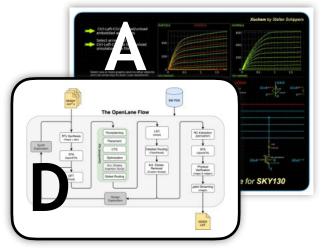

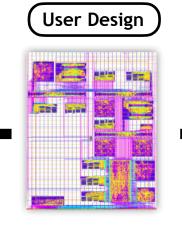

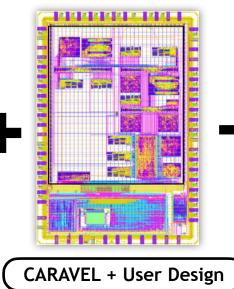

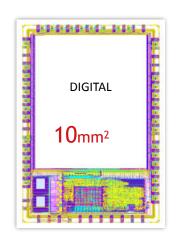

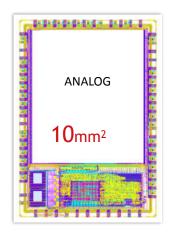

- Participants use an Harness SoC (<u>Caravel</u>) with <u>10mm2 open area</u>

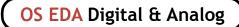

- SKY130 Open Source Digital & Analog Design Tools are available

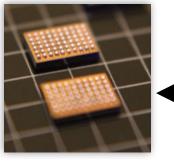

- Participants get 5 dev boards + 300 WCSP-packaged parts

- All designs must be public and under an open source license

- All designs must contain information & files to reproduce the work

- Participants are strongly encouraged to try new ideas, take risks and iterate

- All skill and experience levels are welcome to participate

Start here <a href="https://ef.link/gmpw">https://ef.link/gmpw</a>

Join the community at <a href="https://ef.link/chat">https://ef.link/chat</a>

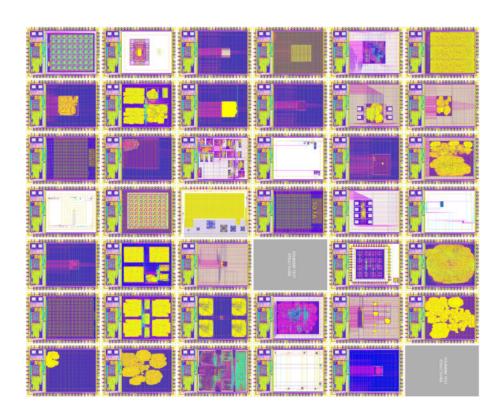

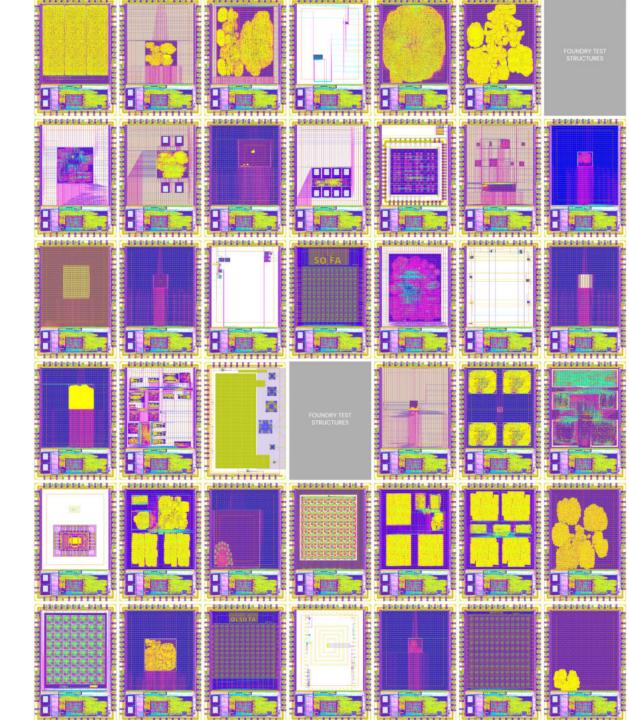

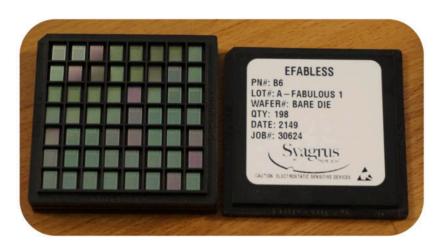

# The first shuttle was overbooked: 45 designs submitted in 30 days!

# Shuttle Program

Sponsored by

#### **DESIGN TYPES**

- 9 x Open processor cores

- 9 x SoC's

- Crypto-currency Miner

- Robotic App Processor

- Amateur Satellite Radio Transceiver

- 7 x Analog/RF

- 5 eFPGA's

See Projects Here: <a href="https://efabless.com/projects/shuttle\_name/MPW-1">https://efabless.com/projects/shuttle\_name/MPW-1</a>

#### **DESIGN TYPES**

- 9 x Open processor cores

- 9 x SoC's

- Crypto-currency Miner

- Robotic App Processor

- Amateur Satellite Radio

Transceiver

- 7 x Analog/RF

- 5 eFPGA's

#### **COMPANIES**

- IBM: OpenPOWER MicroWatt

- QuickLogic eFPGA

- Antmicro

- Western Digital Swerv-EL2

- EFabless

- SpinMemory

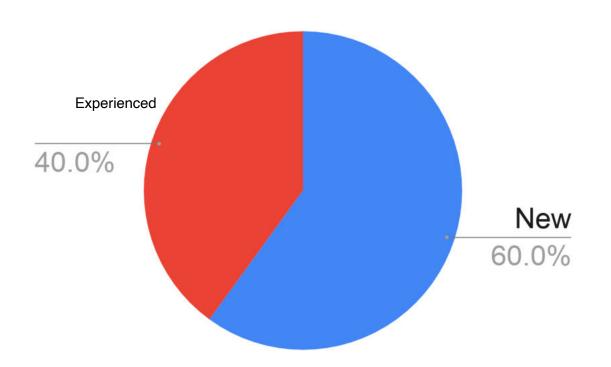

# 60% by first time designers!

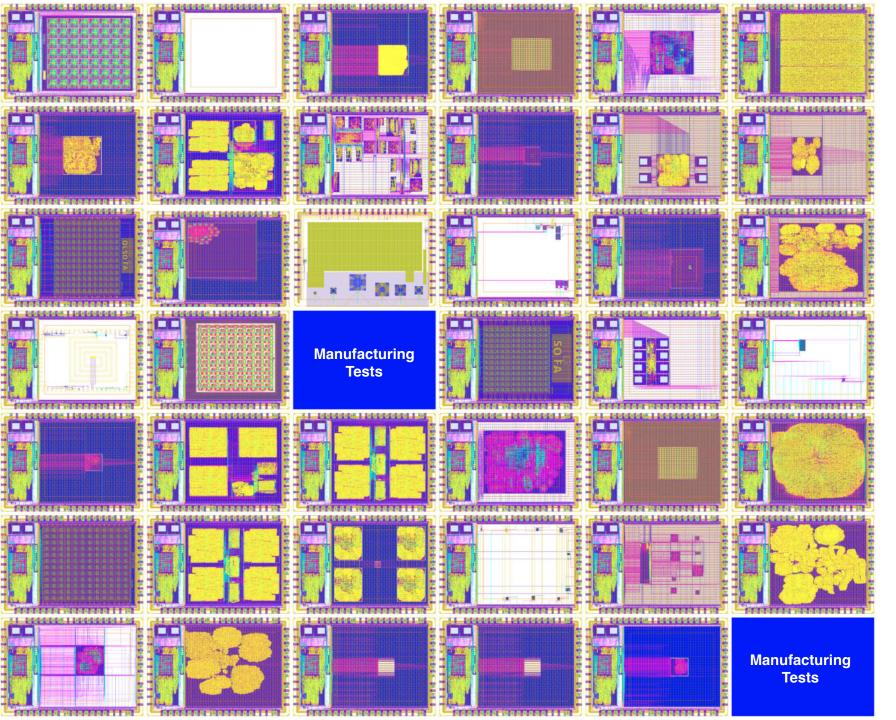

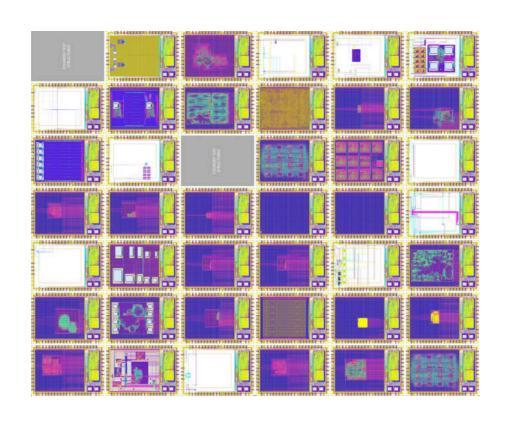

# And so was the second: 56 designs submitted in 30 days!

# Shuttle Program

Sponsored by

#### **DESIGN TYPES**

- 11 x Open processor cores

- 11 x SoC's

- Crypto-router

- T<sub>2</sub>D Converter LIDAR

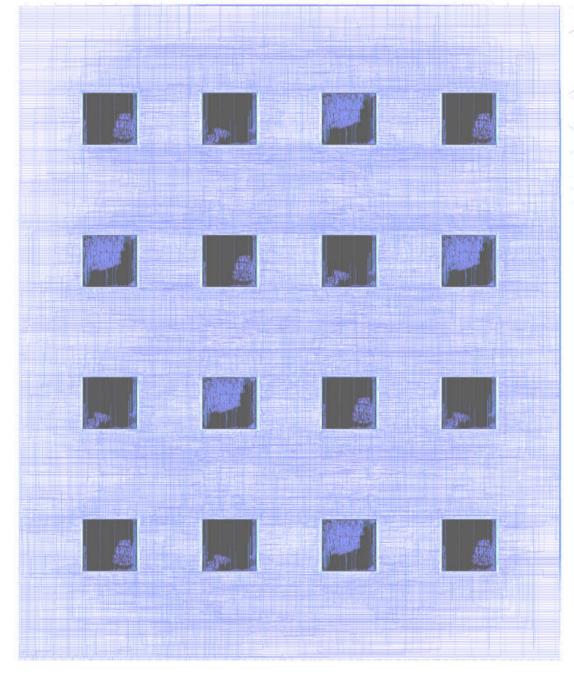

- Multi-project harness for Caravel x 16

- 17 x Analog/RF

- 2 eFPGA's

See Projects Here: <a href="https://efabless.com/projects/shuttle\_name/MPW-2">https://efabless.com/projects/shuttle\_name/MPW-2</a>

# **MPW ONE**

# MPW TWO

Sponsored by

**WELCOME TO THE EFABLESS OPEN MPW SHUTTLE PROGRAM**

NIVERSITY IN CAIRO

Universities Put Fabrication into Courses and Drive Research and Early Innovation

Companies Advance and Showcase their Innovations

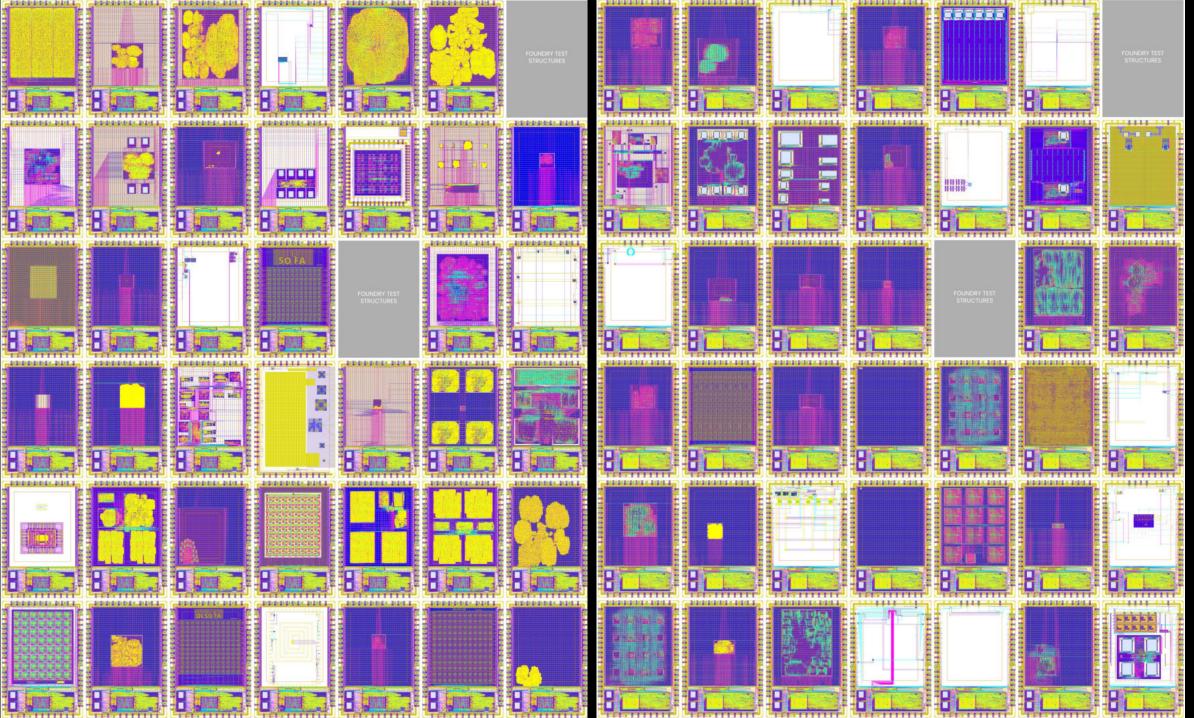

# OpenMPW Project Submissions

Always Overbooked

45 MPW-1

56 MPW-2 **52**MPW-3

55 MPW-4

77 MPW-5

https://efabless.com/projects

Temperature

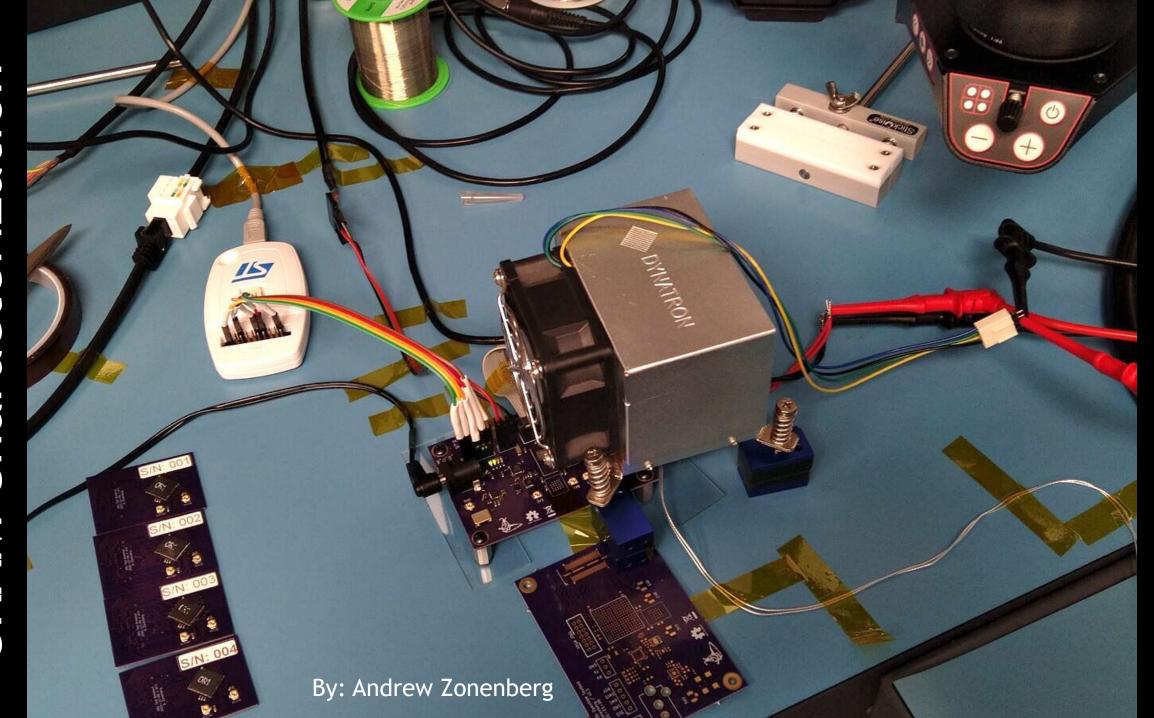

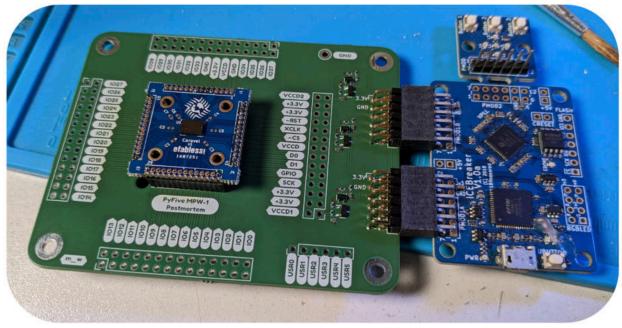

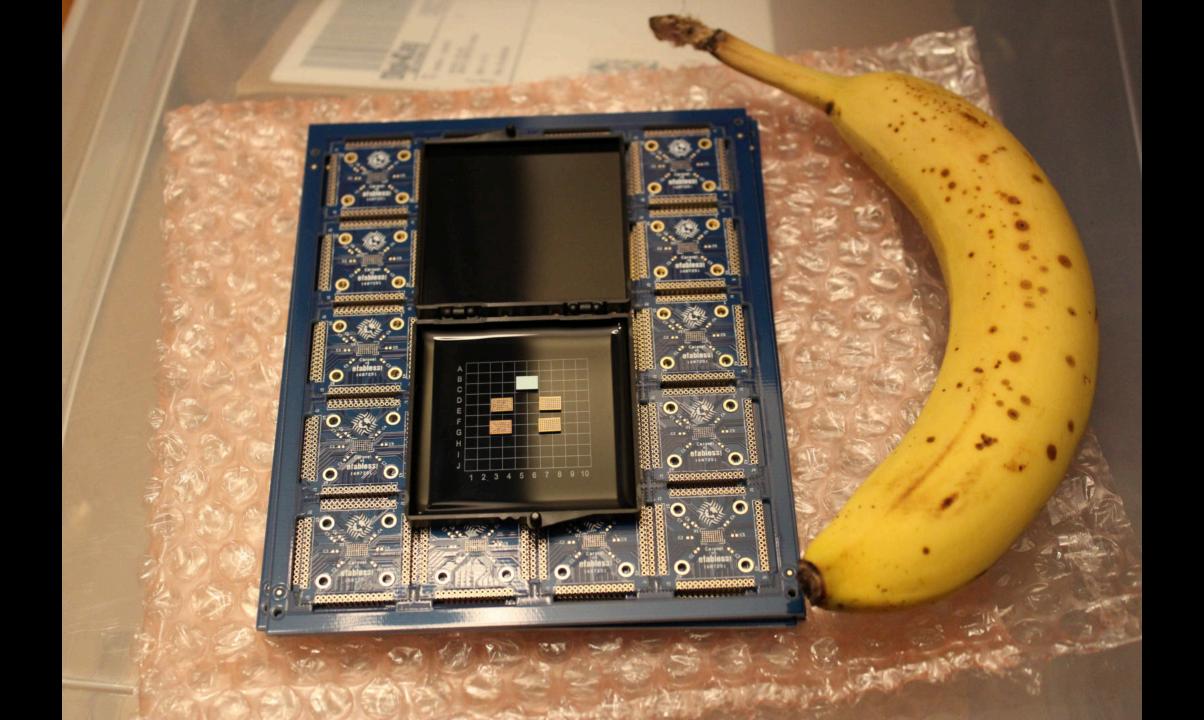

- www.zerotoasiccourse.com/post/mpw1-bringup/

- github.com/mattvenn/mpw1-bringup

bit.ly/cicc22-edu-goog

All my ASIC designs for Google MPW1 are working!

Zero To ASIC Course 1.1K views • 1 month ago

youtu.be/IdOvywOSSmI

bit.ly/cicc22-edu-goog

Woowzaaa!! I'm Caravel!!

bit.ly/cicc22-edu-goog

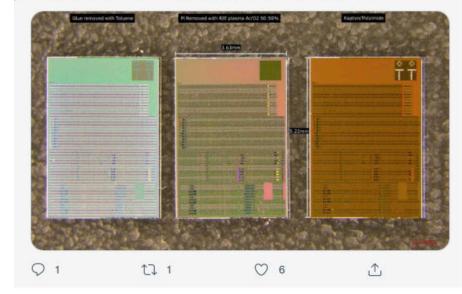

#### Volodymyr Pikhur @vpikhur · 15h

Replying to @vpikhur

Loaded 10 samples into RIE (reactive ion etcher) to strip top polyimide layer. I use a 50/50 mix of oxygen and argon gas.

olodymyr Pikhur @vpikhur · 15h

...

ter polyimide is removed there is adhesive/glue layer remaining. Adhesive n't be removed with normal solvents such as acetone or isopropyl cohol. Very non-polar solvent such as Toluene does the job.

#### Volodymyr Pikhur @vpikhur · 15h

All 3 under stereo microscope with approximate die dimensions.

# $MPW^2$

github.com/mattvenn/ multi\_project\_tools

Compatible with

Open MPW or chiplgnite

Programs

16 projects in one slot

100 ICs  $\div$  16 = ~5 ICs each \$9,750  $\div$  16 = ~\$610 USD

## **BUT** ....

What if I do not want to open source my design? I would like to guarantee my spot on the run. I need it on my own schedule.

# chipignite by efabless:

chipIgnite

Rapid IC Creation

**Start Here**

https://ef.link/start-digital https://ef.link/start-analog

5 Dev Boards

300 WCSP Parts

MANUFACTURING

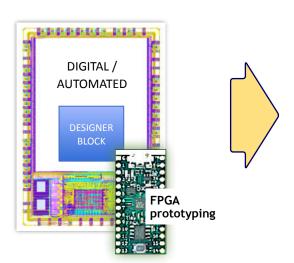

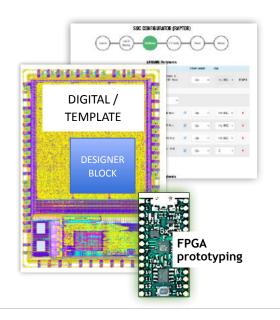

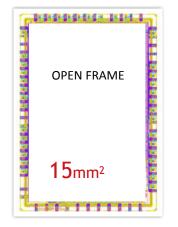

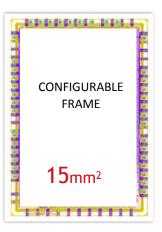

# chipignite options

### LOW COMPLEXITY

IP Development

Digital & low frequency analog

Enabling larger designer base

## HIGH COMPLEXITY

IP Development

Complete Custom ASIC

Analog & Digital

Expert designer base

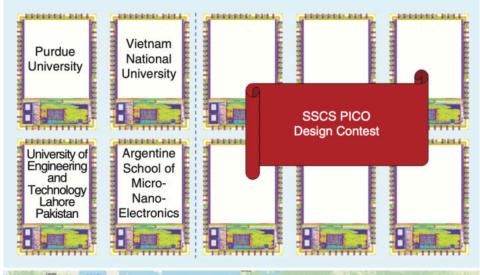

#### IEEE - PICO PROGRAM

2021

Link to Article SSCS Magazine Article - NOV 2021

Multiple Projects per One chipIgnite Slot

Link to Article SSCS Magazine Article - JAN 2022

## chiplgnite CUSTOMERS

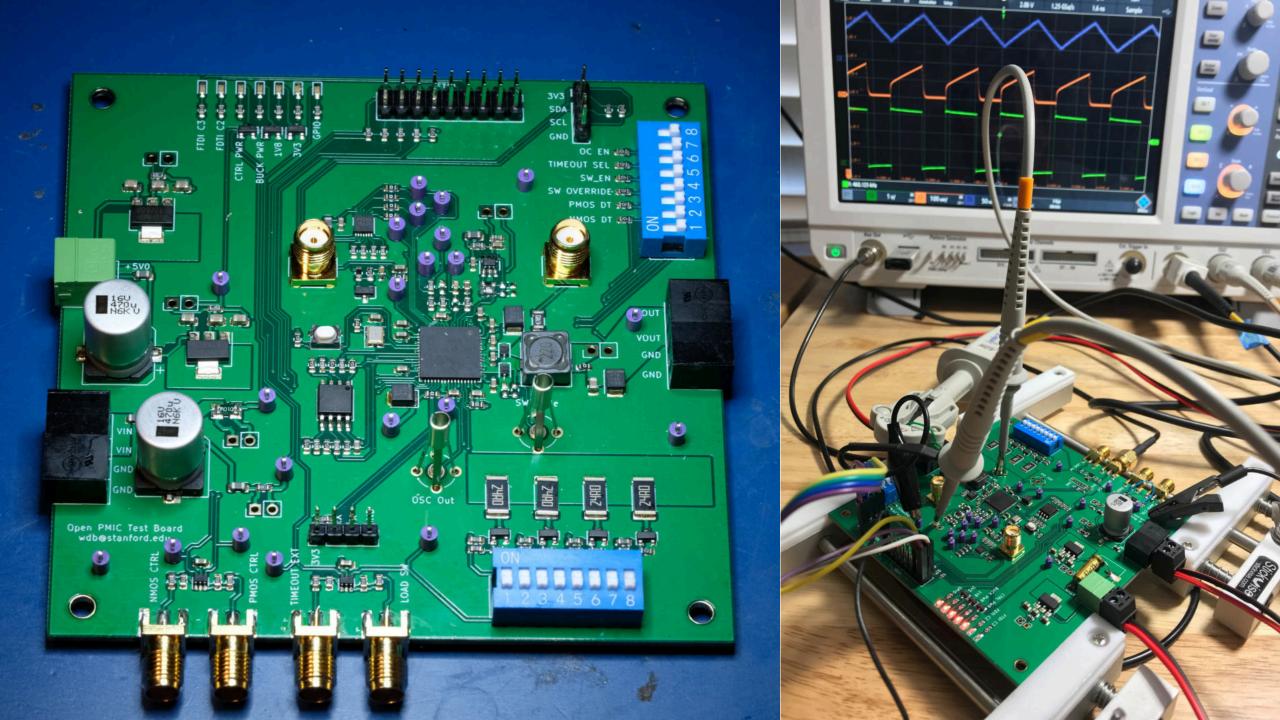

Stanford **EE272** Design Course

Three more universities ...

High Schools coming in June 2022

#### **Startups**

Using chipIgnite as their proof-ofconcept or low volume production

SSCS "PICO" Open Source Design Contest:

56+ submitted designs

will tape out at Efabless

https://sscs.ieee.org/about/solid-state-circuits-directions/sscs-pico-program https://efabless.com/projects/project\_definition/SSCS-21 2

Open Source

FPGA Foundation

global program

innovation among

university

students

#### 2 ChipIgnite Slots per University

Turkey, Pakistan, India, Australia

#### OPEN SOURCE CHIPATHON - 2022

| Low power 130nm CMOS 10 Bit SAR ADC                  | https://platform.efabless.com/projects/851 |

|------------------------------------------------------|--------------------------------------------|

| Analog Baseband Circuitry For 60GHz Receivers        | https://platform.efabless.com/projects/855 |

| SPATIAL SD ADC                                       | https://platform.efabless.com/projects/872 |

| ENCRYPTED LSB STEGANOGRAPHY WITH AES ACCELERATOR     | https://platform.efabless.com/projects/873 |

| CMOS Bandgap Voltage Reference Design                | https://platform.efabless.com/projects/874 |

| On Chip DC-DC Converter with Fast Transient Response | https://platform.efabless.com/projects/879 |

| DC-DC Buck Converter for efficient CubeSat EPS       | https://platform.efabless.com/projects/881 |

| CMOS Power Oscillator Test Chip                      | https://platform.efabless.com/projects/882 |

| Subthreshold SRAM                                    | https://platform.efabless.com/projects/883 |

| Self-Interference Cancellation Low Noise Amplifier   | https://platform.efabless.com/projects/888 |

| MATRIX MULTIPLIER FOR AI ON EDGE APPLICATIONS        | https://platform.efabless.com/projects/889 |

| ReRAM based DNN accelerator                          | https://platform.efabless.com/projects/904 |

| Mix-Pix - A mixed signal circuit for smart imaging   | https://platform.efabless.com/projects/916 |

| 60 GHz demonstrator chip                             | https://platform.efabless.com/projects/920 |

| A compact batteryless low-startup boost converter    | https://platform.efabless.com/projects/922 |

| Sub-Sampling PLL targeting SerDes Applications       | https://platform.efabless.com/projects/923 |

| Radiation-Hardened-By-Construction Microcontroller   | https://platform.efabless.com/projects/928 |

| Mixed-Signal SoC for Nanopore-Based DNA Sequencing   | https://platform.efabless.com/projects/933 |

| Digitally Enhanced PLL                               | https://platform.efabless.com/projects/935 |

| Novel boost converter for battery-powered IoT uses   | https://platform.efabless.com/projects/939 |

| System on Chip for the Next Pandemic                 | https://platform.efabless.com/projects/945 |

| Electrochemical Water Quality Monitoring             | https://platform.efabless.com/projects/951 |

#### WHAT IS?

- Design using SkyWater SKY130 (130nm) rich process + std cells + IO cells

- Start from the Caravel Harness no cost book your slot for \$200

- You *choose your licensing terms* for your design by *default it's proprietary*

- The offered area (10mm2) is not just silicon area It is a framed house with plumbing and electricity just bring your appliances

- Cycle Time 95 days +/- depending on the package choice

| Rapid Prototyping     | \$9,750  | 100 QFN parts + 5 dev boards   |

|-----------------------|----------|--------------------------------|

| Engineering Samples   | \$9,750  | 300 WCSP parts + 5 dev boards  |

| Low Volume Production | \$20,000 | 1000 WCSP parts + 5 dev boards |

## chiplgnite: GET STARTED

- o chipIgnite Web Page

- Getting Started Video

- Project Template on Github

- o Browse Previous Projects

- Join SkyWater PDK Slack Space https://join.skywater.tools

- o The OpenLane flow for digital PnR can be found at https://openlane.readthedocs.io

- The OpenROAD Project <a href="https://theopenroadproject.org/">https://theopenroadproject.org/</a>

- The documentation is at https://docs.skywater.tools

- Caravel documentation https://caravel-harness.readthedocs.io

- WOSET/ICCAD Workshop on EDA <a href="https://woset-workshop.github.io/WOSET2020.html">https://woset-workshop.github.io/WOSET2020.html</a>

### **GET TO SILICON**

https://efabless.com

#### CARRIER SOC HARNESS

## caravel noun

car·a·vel | \ 'ker-ə-ˌvel , 'ka-rə-, -vəl \

#### **Definition of caravel**

: any of several sailing ships

A small 15th and 16th century ship that has broad bows, high narrow poop, and usually three masts with lateen or both square and later sails.

Source: https://www.merriam-webster.com/dictionary/caravel