#### RISC-V Days Tokyo 2022 Spring

# Creating a World where a 14-year-old Designs a Chip

Mohamed Kassem

Cofounder & CTO, EFABLESS.COM

mkk@efabless.com

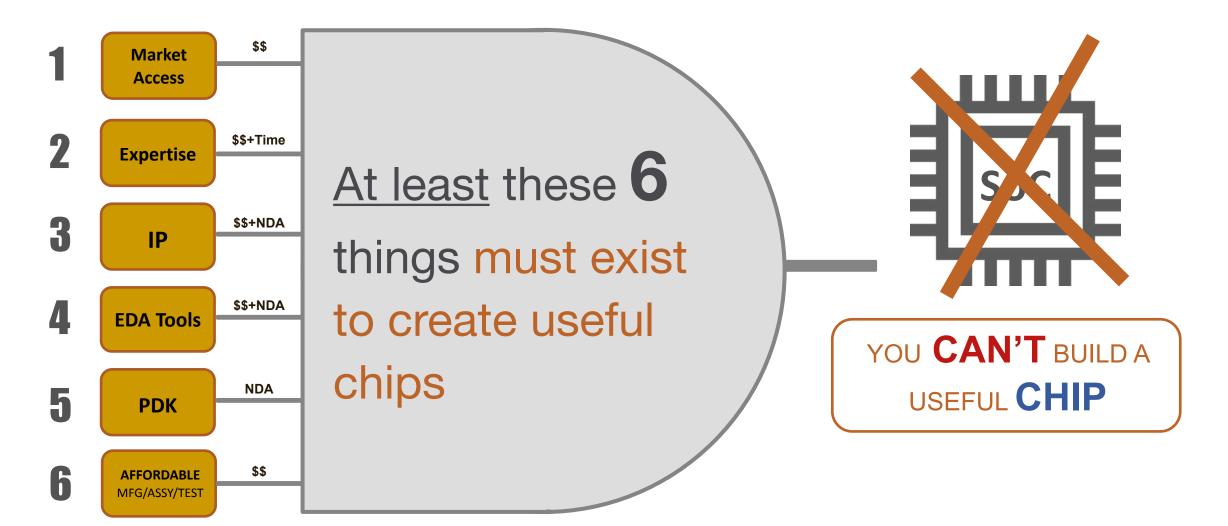

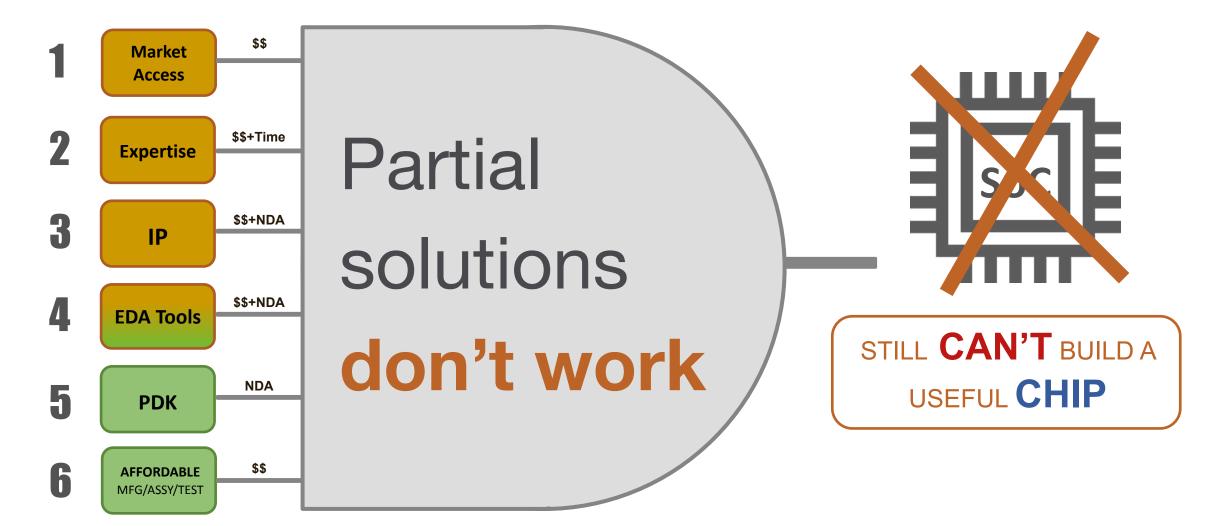

## Why is it "hard" to design chips

Limited access to knowledge

Limited access technology

Costly manufacturing

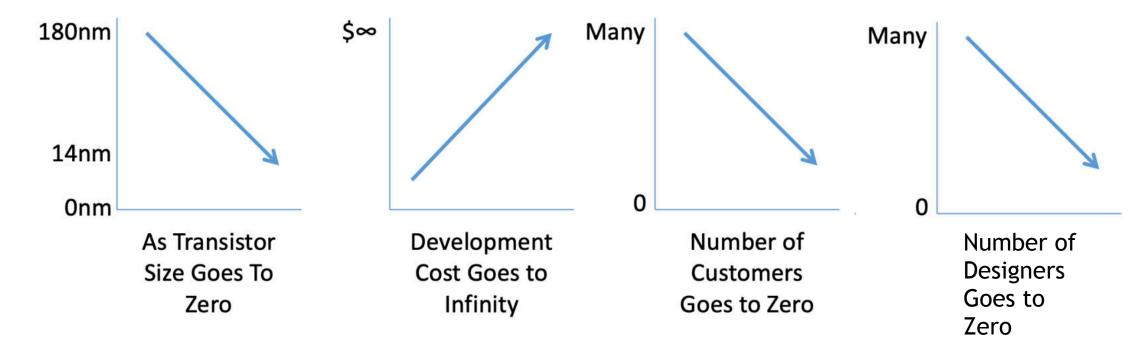

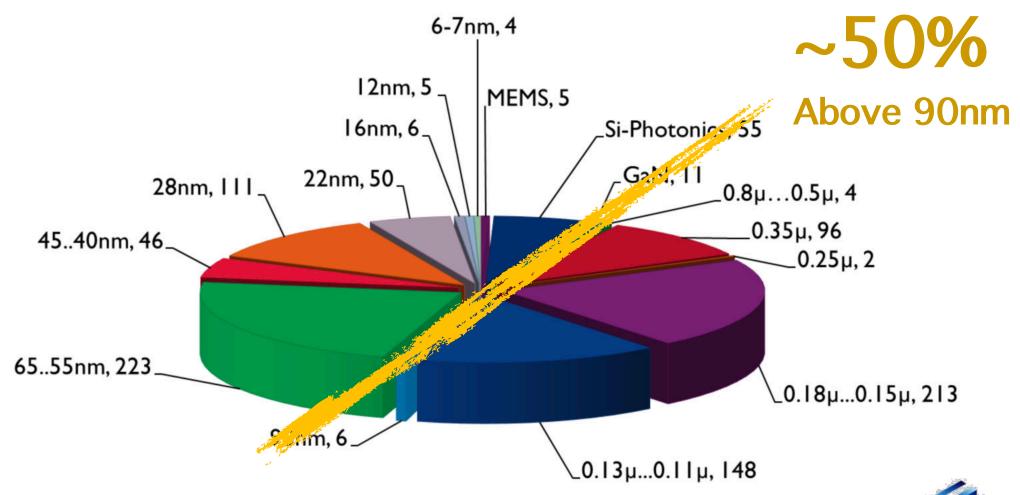

#### **CHIP INDUSTRY TRENDS**

Source: Mike Noonen

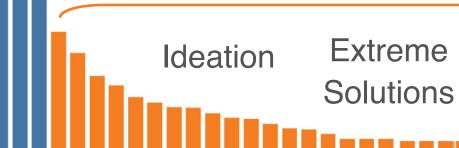

#### WE NEED A 1000X PRODUCT DESIGNERS

Markets Served By Traditional Methodology Long-tail Innovation is required on a massive scale to meet demand 10,000's of Products

Niche Al Markets ML Right-sized compute & power

number of products

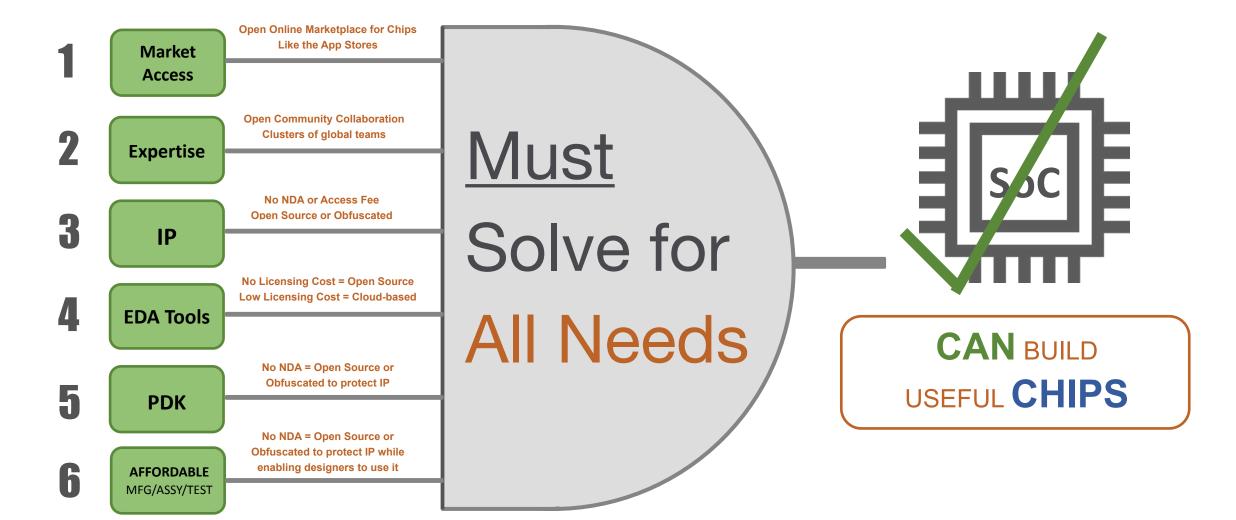

#### We need to

# Simplify the process of Chip creation and Open it to Everyone

# How would we simplify chip design?

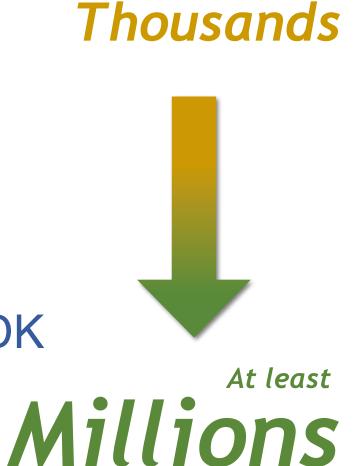

## Think what app stores did to software innovation.

Simplified (democratized)

the development tools

the business process

the connection to customers

## Think what app stores did to software innovation.

Simplified (democratized)

the development tools

the business process

the connection to customers

Thousands

## Think that we apply the same approach to chip design

Simplify (democratize)

the access to chip design tools & PDK

the business process

the connection to customers

Think that we apply the same approach to chip design

Simplify (democratize)

the access to chip design tools & PDK the business process

the connection to customers

## .... too complicated

## .... still too complicated

### .... what we need ...

## How do we simplify chip

design? #1

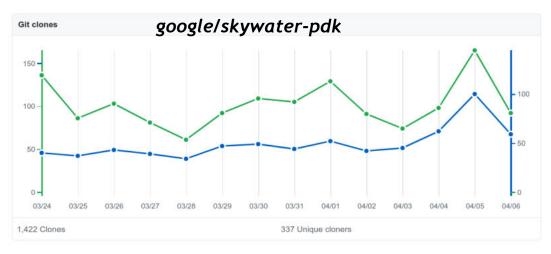

## Open access to technology PDK \*\*\* SKYLWOTER OPEN ACCESS TO TECHNOLOGY PDK \*\*\*

No NDA, nothing to sign - it's Open Source

\$ git clone https://github.com/google/skywater-pdk

- -> Technology information availability is virtually limitless

- -> Leading to massive open collaboration

- -> Skywater 130nm PDK

## What do I do with a 130nm process? intel Intel Chips

13

2000

Initial clock speed:

1.5GHz

Transistors:

42 million

Manufacturing technology 0.18 micron

Drocossor

Initial clock speed:

1.7GHz

Transistors:

42 million

Manufacturing technology: 0.18 micron

processor

Initial clock speed:

1.7GHz

Transistors:

55 million

Manufacturing technology:

90nm

16

2006

Intel® Core™2 Duo

processor

Initial clock speed::

2.66GHz

Transistors:

291 million

Manufacturing technology:

65nm

410 million

Manufacturing technology: 45nm

4/ MIIIION

Manufacturing technology: 45nm

1.16 DIIIION

Manufacturing technology: 32nm

1.4 DIIIION

Manufacturing technology: 22nm

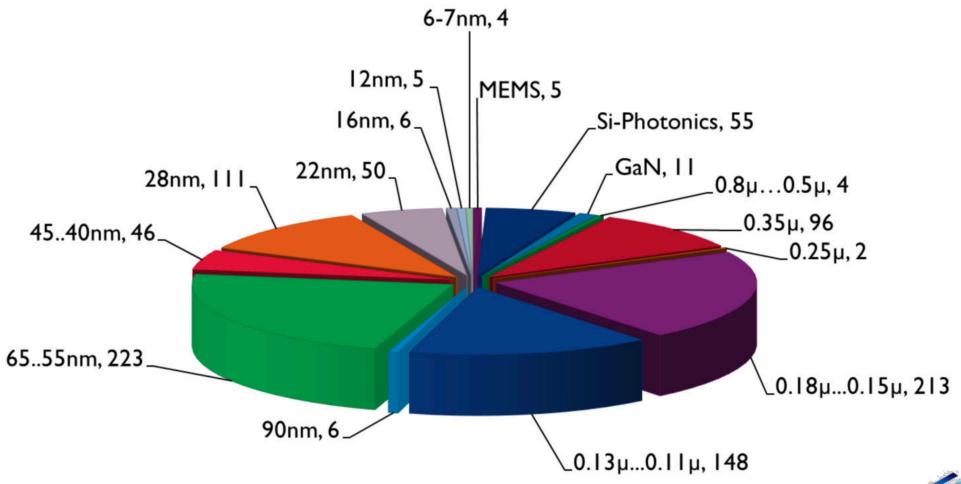

#### FABRICATION SERVICE (CIRCUITS 2021)

#### FABRICATION SERVICE (CIRCUITS 2021)

## **A LOT....**

See efabless.com/projects

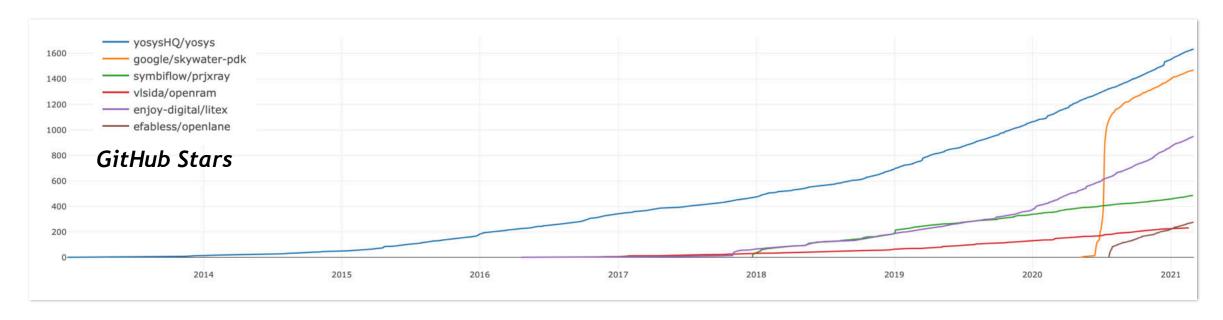

#### SKY130 OPEN SOUCRE PDK WENT VIRAL

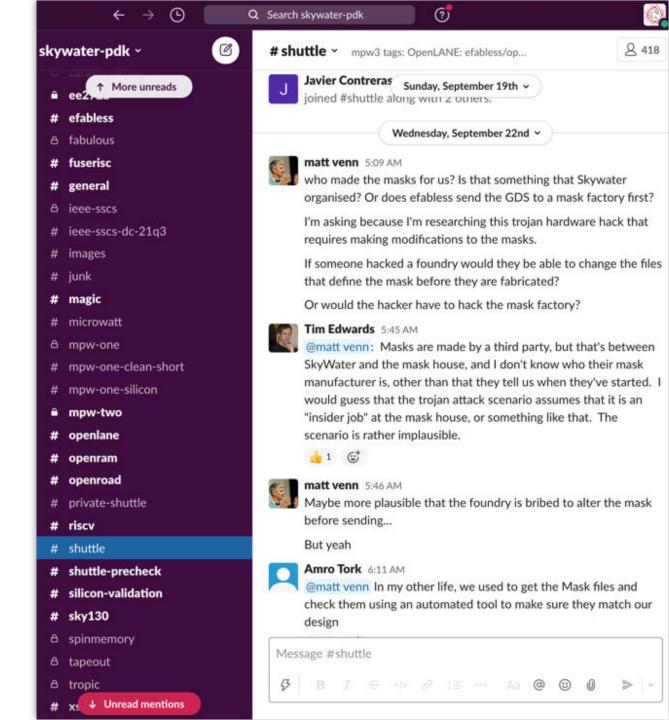

#### LIVE SLACK COMMUNITY

3K+

100+

COMMUNITY MEMBERS

CHANNELS & TOPICS

Join SkyWater-PDK Community <a href="https://join.skywater.tools">https://join.skywater.tools</a>

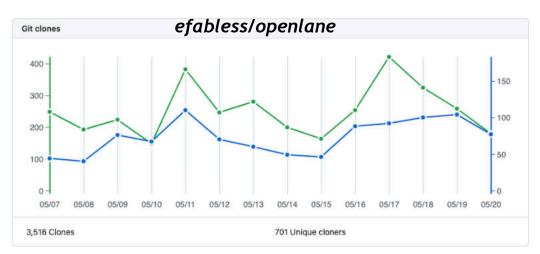

## How do we simplify chip

design? #2

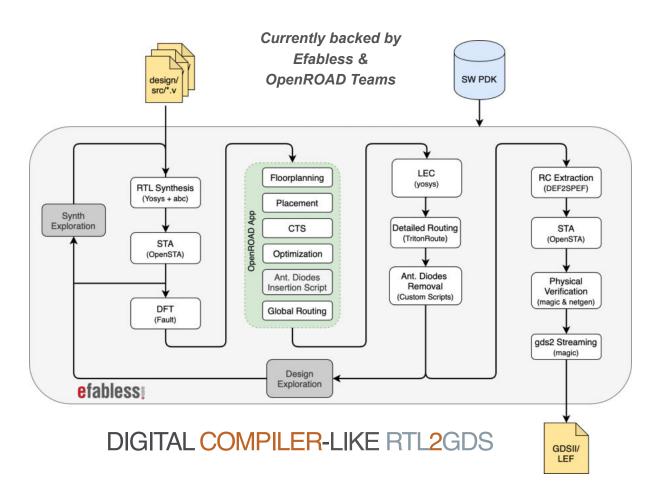

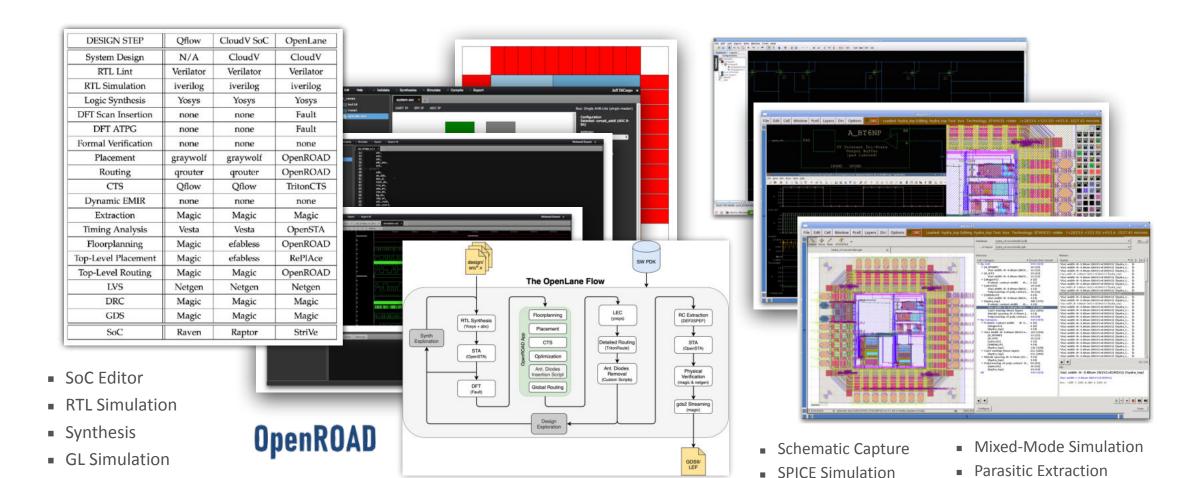

## Codify and abstract knowledge

Automate code-to-chip

like a *GNU software*compiler - with trade-offs

in area and performance.

It opens the door for software developers to generate hardware That's at least a 1000x more potential designers!

#### **OPEN SOURCE DESIGN FLOWS & TOOLS**

Silicon Compiler Coriolis OpenLane

Physical Verification

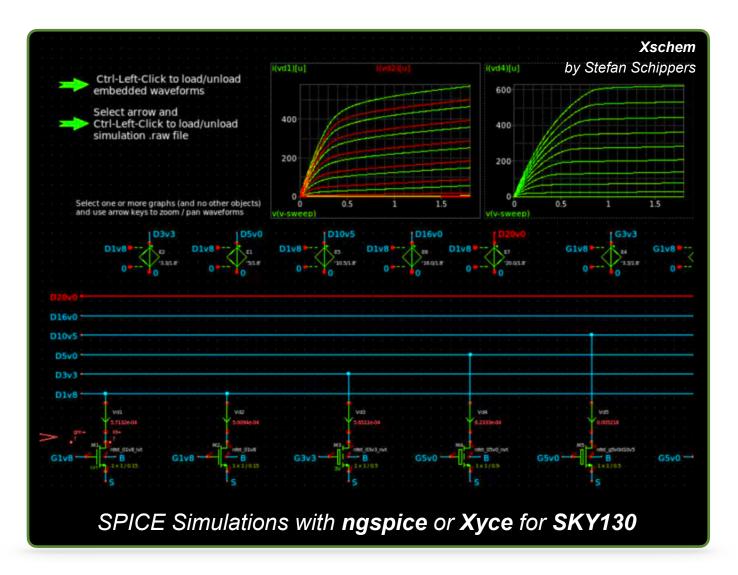

#### ANALOG TRANSISTOR-LEVEL

Analog transistor-level design, schematic and layout

Schematics: Xschem

Simulators: ngspice, Xyce

**Support:** Process Corners and statistical simulations

Packed with out-of-thebox examples - just click, copy and run yours

# Why does it matter to have tools open-sourced?

Limitless availability which fosters spontaneous idea realization and open collaborative development by community

## How do we simplify chip

design? #3

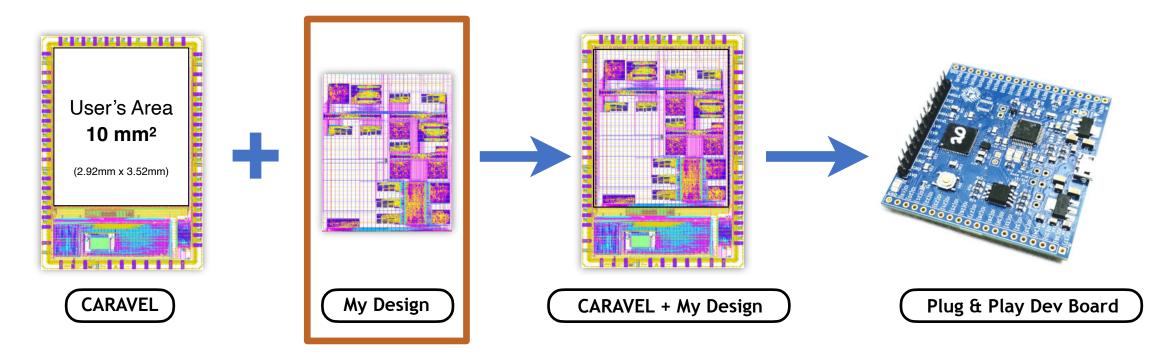

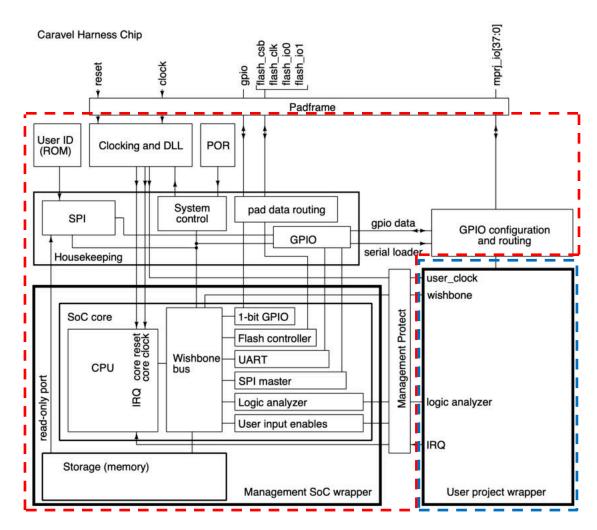

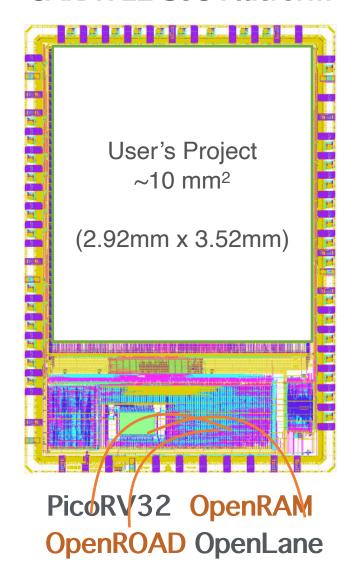

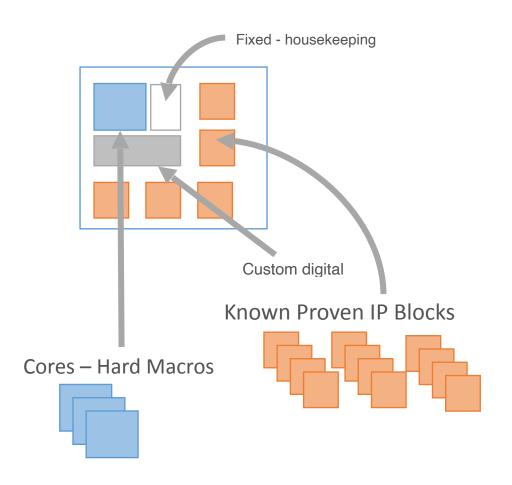

### Start from the 15th floor to reach 20

Build on existing foundational work by others - CARAVEL You only need to know your design ... or your code

#### **CARAVEL PLATFORM**

https://github.com/efabless/caravel

#### **CARAVEL SoC Platform**

.github/workflows .travisCl modifications docs gds irsim ß lef reuse lvs ease macros mag tomaglef Structure ngspice oas Uniform Open Source File openlane qflow scripts signoff spef spi/lvs utils verilog

xyce

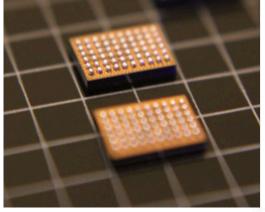

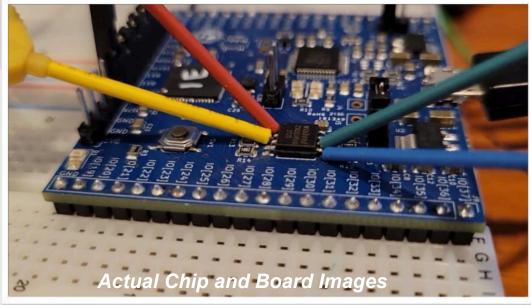

#### **SILICON TESTING & VALIDATION**

Designers receive packaged chips and assembled 5 evaluation boards with for each project

On-chip **open source** test framework with firmware to support the following:

- On-chip logic Analyzer

- Drivers for common peripherals

- Flash memory programming software utility

- Example firmware routines for common functions

- Instructions for customizing firmware for each project

## How do we simplify chip

design? #4

## Build an open library of "IP blocks"

#### Make them like **LEGO**

- Silicon proven / verified functions

- Highly leveraged known proven IP blocks

- Scope of customization is constrained

- Quality processes enable extending the known proven IP blocks by community

#### Select

### Open

#### Source

### Designs

caravel\_fulgor\_opamp

Diego Hernando |

http://www.fundacionfulgor.org.ar/sitio/i ndex.php

Operational amplifier (opamp) based on the Miller topology designed in Skywater SKY130 CMOS process.

SKY130 @ 2.2k

SHA1 engine

Konrad Rzeszutek Wilk

The SHA1 engine, while not the most secure nowadays is still used by git commits and TPM PCR...

SKY130A 731

Caravel-SOFA-HD

Xifan Tana |

https://sites.google.com/site/pegaillard on/home

SOFA-HD (Skywater Opensource FPGAs)

SKY130 @ 1.6k

Caravel

Sylvain Munaut |

https://github.com/PyFive-RISC-V

Peripherals tests for future SoC targeting Micro/Circuit Python

MPW-1 SKY130 @ 1.8k

#### Caravel User-project Initiator Interconnect

FWPayload public

Matthew Ballance I http://github.com/mballance

A simple RISC-V core+peripherals subsystem for the Google-sponsored Open MPW shuttles for SKY130.

Caravel\_Astria\_Testchip

public

Astria Nur Irfansyah | http://www.its.ac.id

Test circuits consisting of synthesizable comparators for a stochastic ADC, to be submitted for...

HS32Core public

Kevin Mack Baragona | https://github.com/hsc-latte

Open Source Hardware Processor

10\_bit\_potentiometric\_DAC

Sameer S Durgoji |

https://www.vlsisystemdesign.com/

Design of a 10 Bit Potentiometric Digital to Analog Converter with 3.3V analog voltage, 1.8V...

1.4k

SKY130A 1.1k