# Leadership in the New Computing Era

**Yoshihito Kondo**

Representative Director, SiFive Japan

## Founded by the Inventors of RISC-V

- SiFive is the RISC-V founder & brand standard

- Leading the commercialization effort since 2010

- World's largest technology Co's work with SiFive to adopt RISC-V

- Largest team & investment

### **Continued Investment Across Diverse Portfolio**

400+

design wins

### **The Gold Standard**

Majority of top Semi manufacturers

Major U.S. hyperscalers

Leading electric, and autonomous vehicles

Billions

Chips based on SiFive RISC-V cores, >10 billion cores

### SiFive is supplying 5 of them

### SiFive Products Are in the Field

A wide range of control, real-time and application processor applications

Embedded Controller for mobile SoC

Camera Sensor

Optical Image Stabilizer

SSD

**FPGA Platforms**

**Network Switch**

Surveillance Camera

WiFi/BT Module

Laptop Docking

Station

Smart Watch

### Shift to RISC-V for Performance and

### **Al Acceleration**

#### Consumer

Edge Al Security Camera

Computational Photography

Mobile & Wearables

Smart TV

#### Infrastructure

Generative Al

DPU

Storage, Networking

5G

#### **Automotive**

Standalone ADAS

Central Compute

IVI

### Accelerating the RISC-V Software Ecosystem

Qualcom

### **HiFive Premier P550 Board**

#### **Key points**

- High performance RISC-V CPU board

- Focusing on a comprehensive out of the box experience

- More information here

#### What might not have been obvious from the PR

- This is effectively an embedded RISC-V PC

- Expected to be fastest performing RISC-V dev board in market

#### What can you expect next?

- Broader portfolio of HiFive development boards

- More news and announcements coming soon...

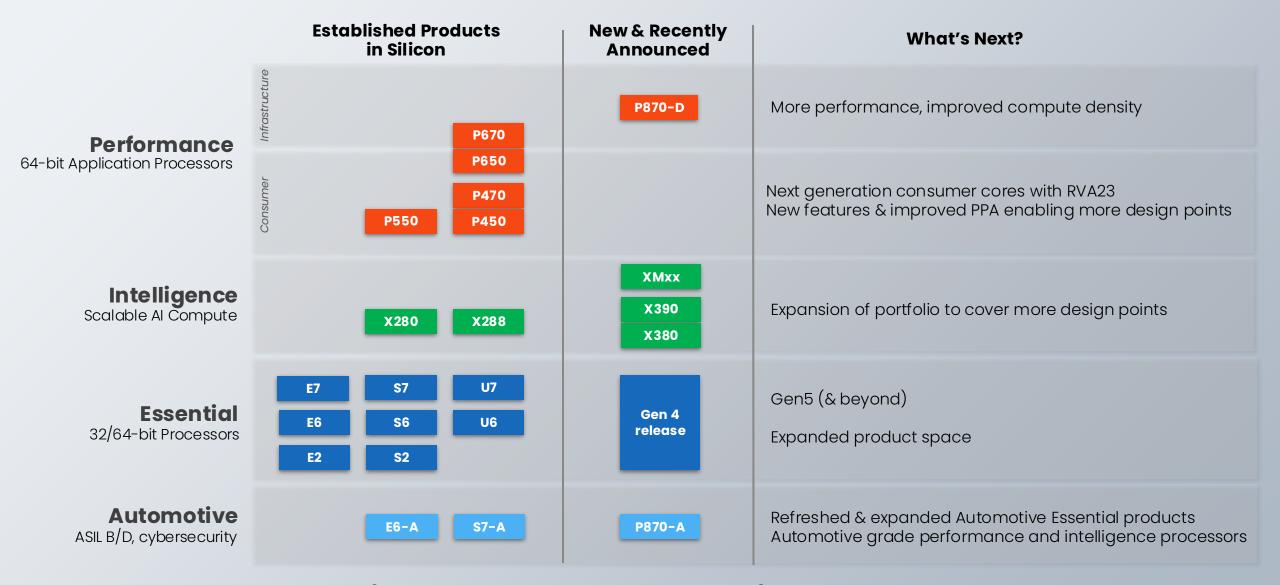

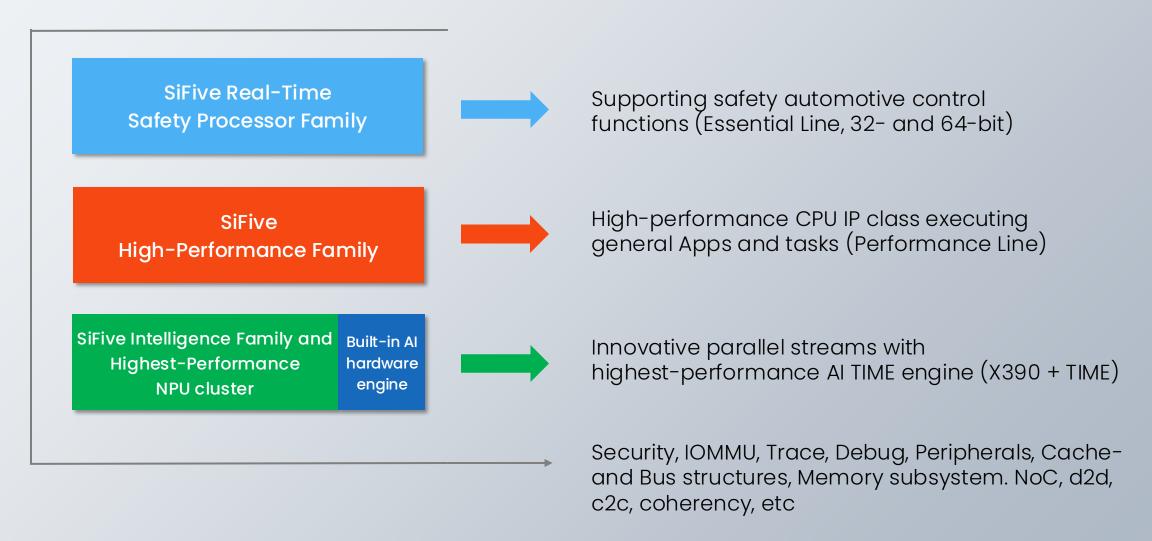

### SiFive Product Update

### 2024 – A Year of Product Portfolio Expansion

#### Embedded ("Essential")

- 4th Generation of Essential Family; Improved performance and power efficiency, inclusion of industry-standard interfaces

- ISO 26262 and ISO 21434; First IP provider to achieve ISO 21434 certification

#### Applications Processors ("Performance")

- P550 Premier Board; Advancing RISC-V open-source software

- P870-D Solution

- Most performant RISC-V processor available today. Bar none.

- Emphasis on simplifying creation of scalable systems

#### Al Compute ("Intelligence")

Today! XM Processor. Leadership processor for accelerating high performance Al workloads

#### SiFive Announces 4th Generation of Popular **Essential Product Line to Spur Innovation Across Embedded Applications**

SiFive is seeing growing adoption, with more than two billion SiFive RISC-V based chips already in the market

Munich, Germany, June 25, 2024 - Today SiFive, Inc. the gold standard for

prod SiFive - July 11, 2024

#### SiFive Becomes First IP Supplier to Achieve Automotive ISO/SAE 21434:2021 Product Certification

it's a critice August 14, 2024 their interc being gen and even o

reputation and recent

View our C

#### SiFive Announces New High-performance RISC-V Datacenter **Processor for Demanding AI Workloads**

SiFive Performance P870-D brings high compute density and scalability to datacenters, vehicles, and embedded systems

Santa Clara, Calif., Aug. 14, 2024 - Today SiFive, Inc., the gold standard for RISC-V computing, announced its new SiFive Performance™ P870-D datacenter processor to meet customer requirements for highly parallelizable infrastructure workloads including video streaming, storage, and web appliances. When used in combination with products from the SiFive Intelligence product family, datacenter architects can also build an extremely high-performance, energy efficient compute subsystem for Al-powered applications.

### ISO 26262 & ISO 21434 Certifications

#### **Key points**

- 4 Essential products certified to ISO 26262 (functional safety) and ISO 21434 (cyber security)

- Products and processes are reviewed and audited by an independent third-party (TÜV SÜD)

### What might not have been obvious from the PR

First IP supplier of any CPU architecture to achieve ISO 21434

#### What can you expect next?

Further expansion of Automotive grade products across all three pillars of compute

### The Auto Evolution - a Better Approach

No architectural breaks

RISC-V is Open.

RISC-V is Flexible.

RISC-V is Standardized.

RISC-V is the best architecture for software defined vehicles.

High level of reusability

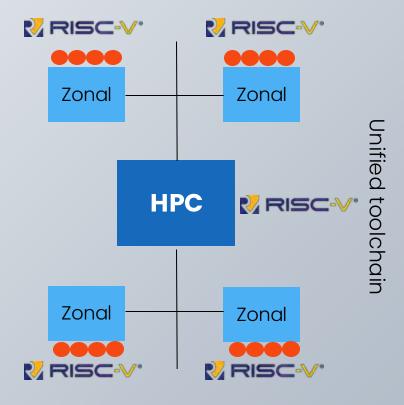

### **ADAS & Zonal HW Building Blocks**

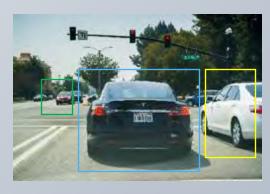

Taking ADAS HW to the next level

### RISC-V Automotive Software Ecosystem

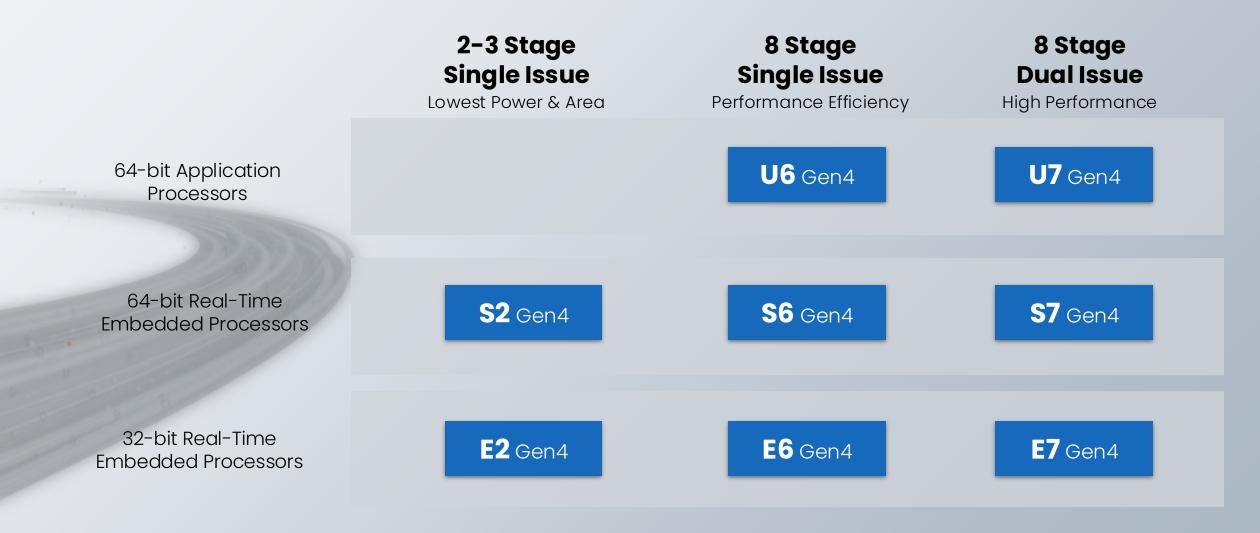

### 4th Generation Essential Processor Portfolio

#### **Key points**

- Major update to embedded products which have shipped in billions of deployed devices

- Family includes cores from 2 stage single issue to 8 stage dual issue, 32- and 64-bit options

- Up to 40% improvement in power over prior generation

#### What might not have been obvious from the PR

Very wide scalability & configuration options

#### What can you expect next?

- A fifth generation, continued innovation & investment

- Expansion of the features, options, configurations

### 4<sup>th</sup> generation SiFive Essential IP portfolio

Fully refreshed portfolio with many configuration options to cover all the possibilities

### 4<sup>th</sup> generation Essential Updates

Driven by market requirements and customer feedback

| Better<br>performance | Lower<br>Power                       | Latest<br>Features            | Improved<br>Interfaces |

|-----------------------|--------------------------------------|-------------------------------|------------------------|

| Improved L2 Cache     | Up to 40% Runtime Power<br>Reduction | RVA22 Profile                 | AMBA ACE Support       |

| Enhanced L1 Memory    |                                      | Hypervisor                    | More CLPs per Core     |

| Performance           | New Power Management                 |                               |                        |

|                       | Features                             | WorldGuard Security           | Improved Burst Support |

| Better Code Density   |                                      |                               |                        |

|                       |                                      | Advanced Interrupt Controller |                        |

|                       |                                      | Secure Debug                  |                        |

### Alls a Capability, Not an Application

A capability that will be added to virtually all systems

### Supports a wide range of devices

From sensors to supercomputers

### Addresses different perf/latency requirements

From object recognition to generative Al

### Adapts to various market-specific constraints

From data center to memory-constrained systems

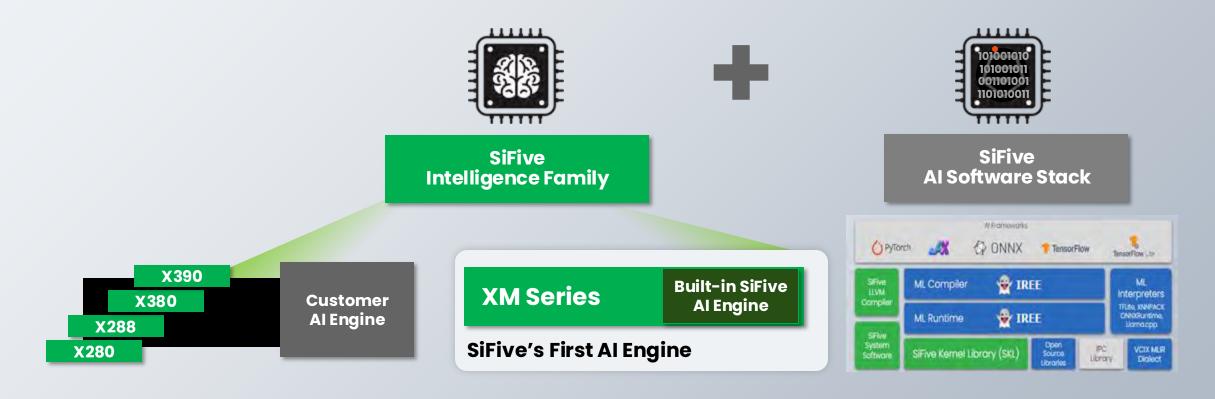

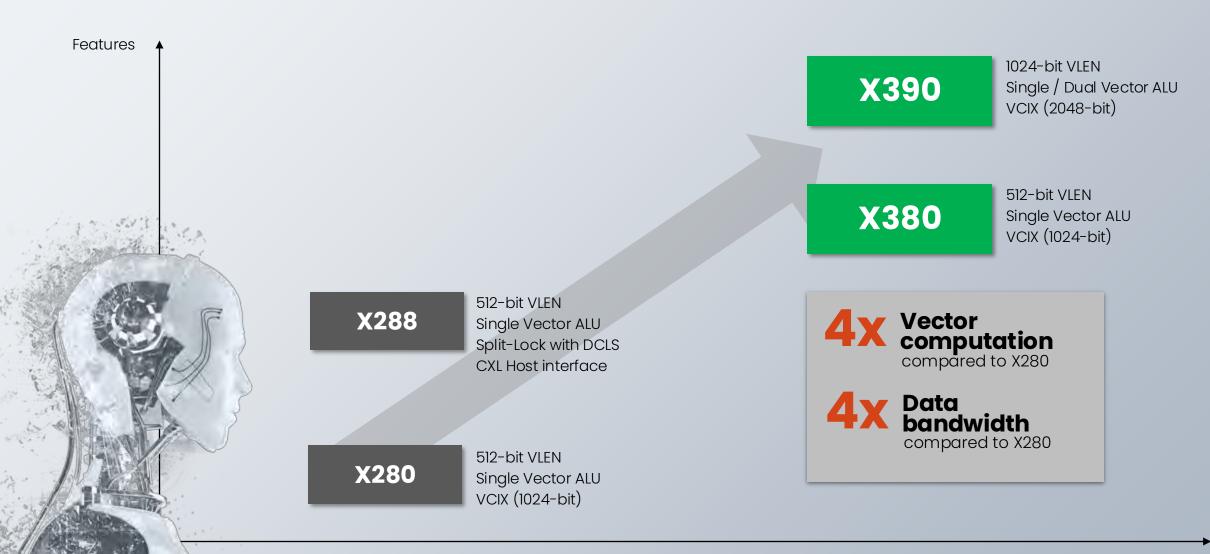

# Today SiFive Expands Intelligence Product Portfolio

New XM series will complement existing X Series portfolio, giving customers more choice

### SiFive Intelligence Family Recap

2023

### Flagship SiFive Based Design Wins

Edge

**Datacenter**

Strong momentum spanning wide range of markets and use cases

© 2025 SiFive 2025

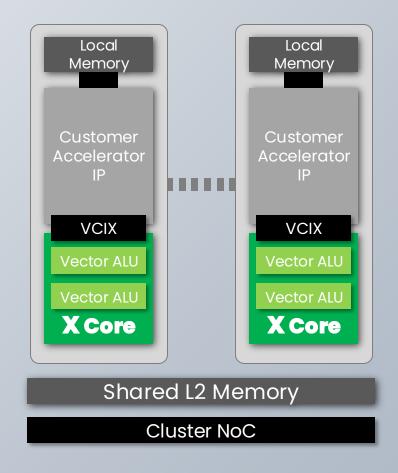

# Typical Intelligence X Core Implementation Using VCIX

- X-Cores provide RISC-V standards, wide vectors, memory interface, and supported software stack

- Highly scalable coherent memory system to accommodate any Al workload

- Wide VCIX interface to optimize data transfer and reduce latency to customer accelerator IP

- 768GBs of total bandwidth per core

- Provides a rapid way for customers to attach high-bandwidth custom accelerators into a standard RISC-V system

Intelligence Cores with VCIX turn customer accelerators into a scalable RISC-V systems

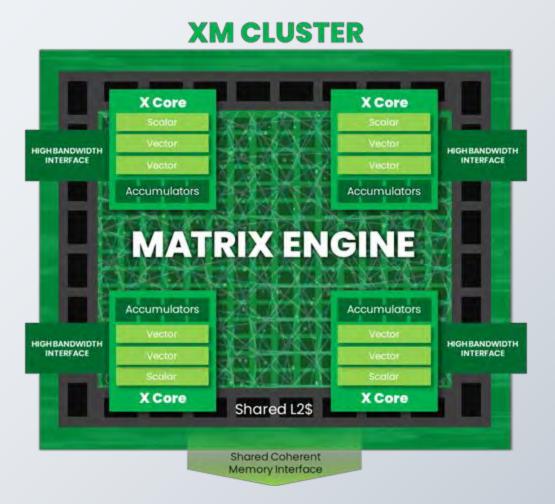

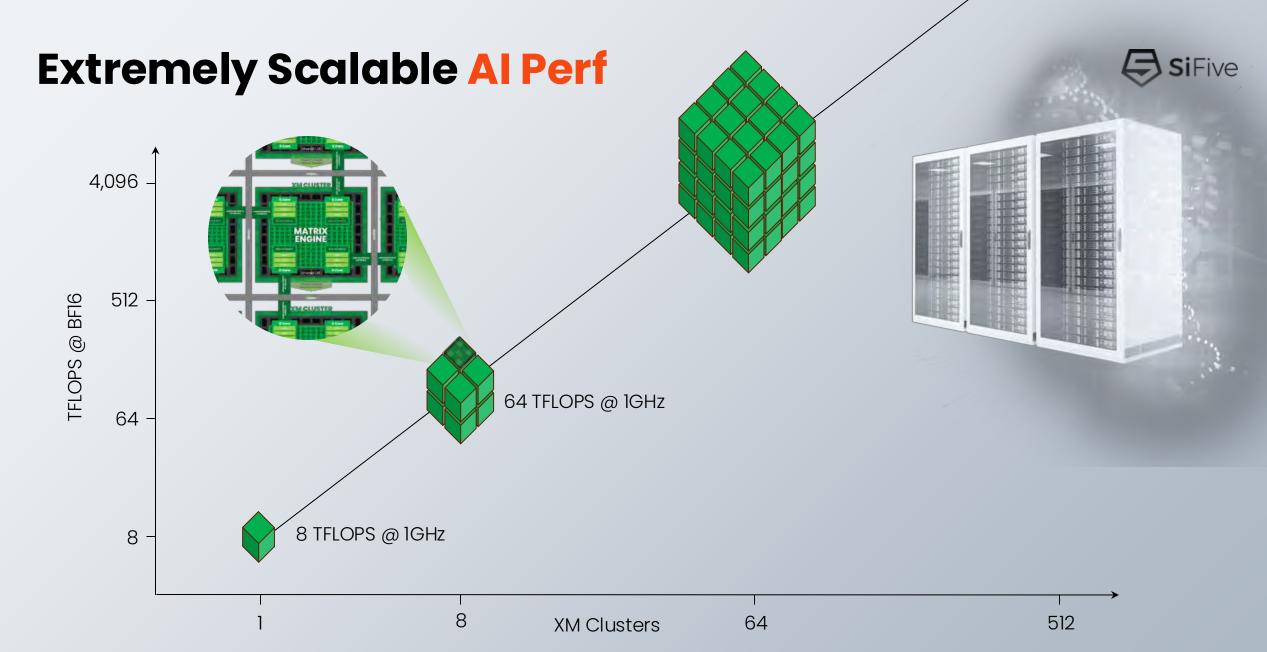

### SiFive XM – Scalable Al Compute Clusters

XM available now for select customers in early evaluation phase

#### SiFive Matrix Engine

Fat outer-product design

Tightly integrated with 4 X-Cores

Deep fusion with vector units

#### **4 X-Cores per Cluster**

Each with dual vector units

Executes all other layers e.g. activation functions

Configurable capacity and bandwidth L2 Cache

New exponential acceleration instructions (up to 64 per cycle per core)

#### **New Matrix Instructions**

Fetched by scalar unit Source data comes from vector registers (INT8, BF16, FP16, FP32, FP64) Destination to each matrix accumulator (INT32, FP32, FP64)

1 Cluster = 16 TOPS (INT8), 8 TFLOPS (BF16) per GHz 2TB/s Sustained Bandwidth per XM Cluster

Integration of scalar/vector/matrix engines enables extremely memory bandwidth-efficient compute

Massive scalability allowing customers to build up to industry leading levels of performance

© 2025 SiFive 2025

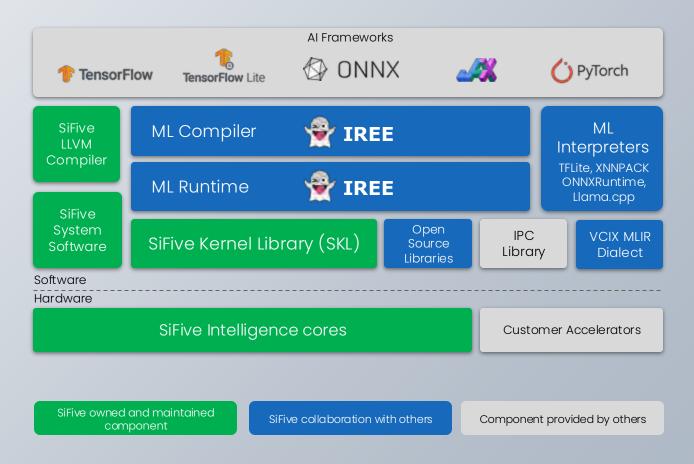

### Software Strategy for Intelligence Processor Family

- SiFive will collaborate across the ecosystem to support creation and evolution of comprehensive solutions

- SiFive is focusing engineering efforts on optimizations for its processor cores within common frameworks

- 3+ years investment in software effort to date

- Creating a proven software reference as starting point

Enabling a collaborative full AI software framework

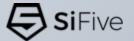

### SiFive Kernel Libraries (SKL)

- Organized into five key areas

- Delivers performance acceleration

- Libraries expose standard APIs where applicable

SiFive will open source SKL to provide a proven foundation for customer development and to help align software efforts across the RISC-V ecosystem

### Why SiFive?

We invented RISC-V: Nobody knows it better

Complete IP portfolio: >\$500M R&D investment

Proven quality: billions of cores shipped, ISO certifications

Customization expertise: workflow geared to enable customer optimized solutions

Trusted advisor: good partners value your interests as much as theirs

Empowering innovators

www.sifive.com