## RVfpga-Soc

# How to go from a RISC-V Core to a RISC-V SoC?

Zubair Kakakhel (AZKY Tech Labs)

Imagination Worldwide University Programme | September 2021

iup@imgtec.com

#### What is a System on Chip (SoC)?

An **SoC** is an integrated circuit or an IC that integrates an entire electronic or computer system onto it.

#### The challenge

Very little material about how to **make** an SoC

```

module swerv

import swerv_types::*;

clk,

input logic

input logic

rst_1,

input logic

dbg_rst_l,

input logic [31:1]

rst_vec,

input logic

nmi int,

input logic [31:1]

nmi_vec,

output logic

core_rst_1, // This

output logic [63:0] trace_rv_i_insn_ip,

output logic [63:0] trace_rv_i address_ip,

output logic [2:0] trace_rv_i_valid_ip,

output logic [2:0] trace_rv_i_exception_ip,

output logic [4:0] trace_rv_i_ecause_ip,

output logic [2:0] trace_rv_i interrupt_ip,

output logic [31:0] trace_rv_i tval ip,

```

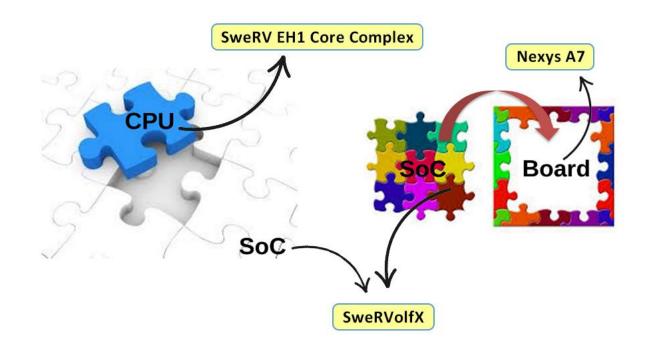

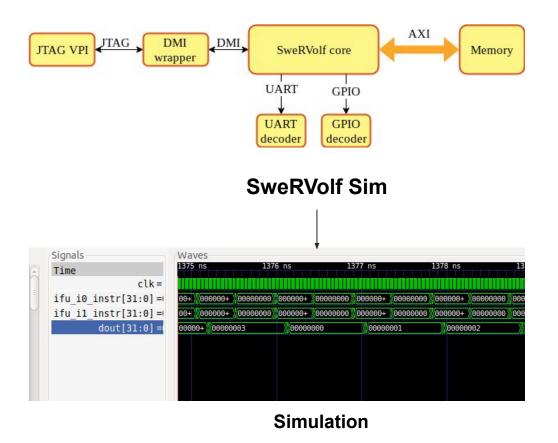

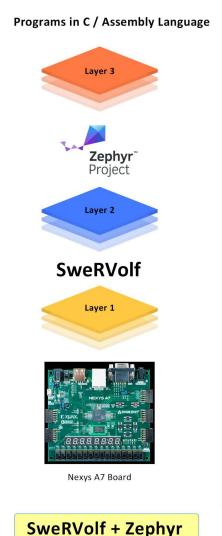

#### What is RVfpga-SoC?

A set of teaching materials explaining how to design and build an SoC

- ➤ CPU

- SweRV EH1

- > SoC

- SwerVolfX

- Board

- Nexys A7

- > Simulator

- Verilator

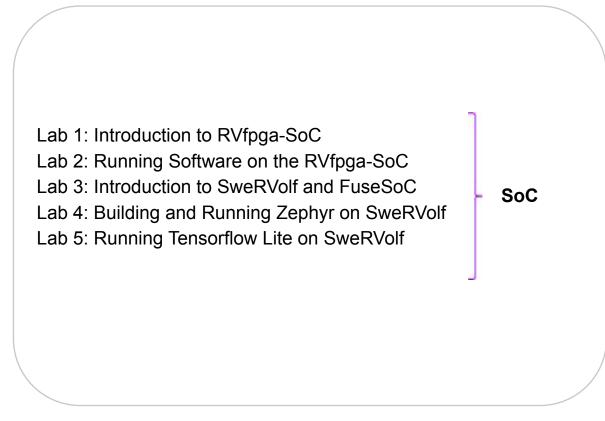

# What does RVfpga-SoC include?

### **RVfpga-SoC Course includes** following five extensive labs:

- 1. Introduction to RVfpga-SoC

- 2. Running Software on the RVfpga-SoC

- 3. Introduction to SweRVolf and FuseSoC

- 4. Building and Running Zephyr on SweRVolf

- 5. Running Tensorflow Lite on SweRVolf

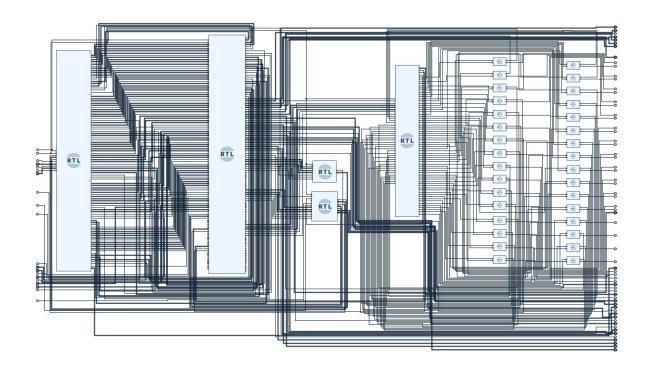

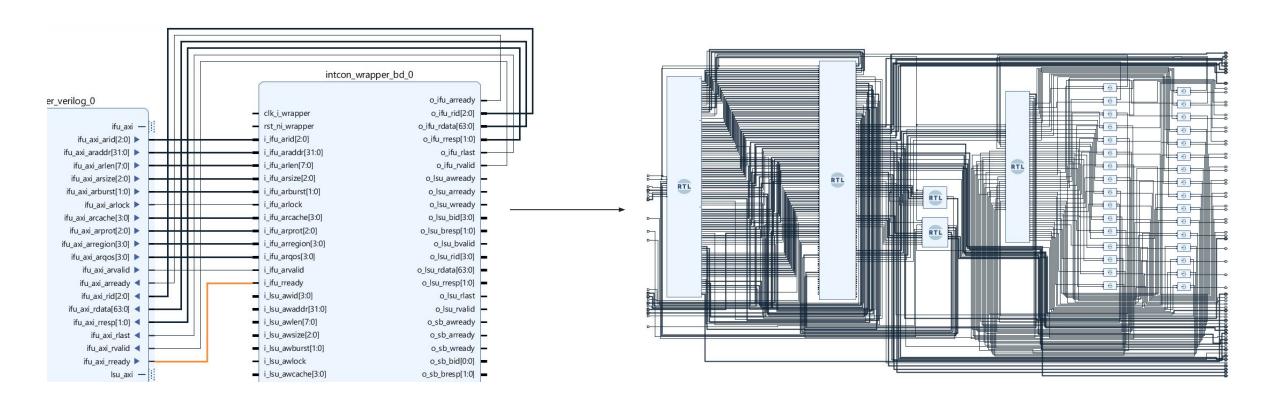

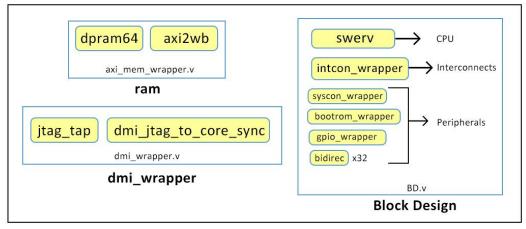

#### Lab 1: Building an SoC (Visual approach)

Wire CPU, Interconnect, Peripherals, Clock, Memory, Reset etc.

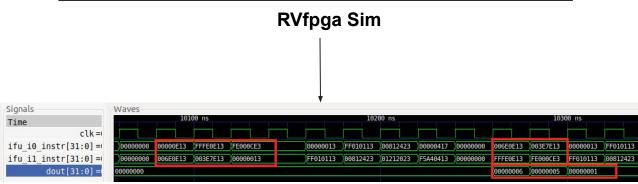

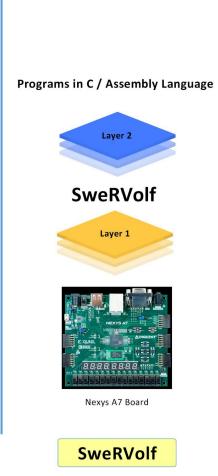

#### Lab 2: Running Software on RVfpga-SoC

Run C programs on the SoC created in Lab 1

**Simulation**

RVfpga Nexys

Nexys A7 Implementation

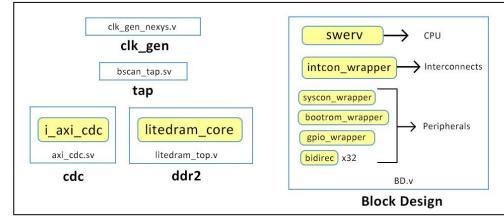

#### Lab 3: FuseSoC approach to SoC design

FuseSoC does all of this tedious work that we manually did in Labs 1 and 2

DDR2

LiteDRAM

SweRVolf core

UART

UART

SPI

SPI

SPI Flash

**SweRVolf Nexys**

Nexys A7 Implementation

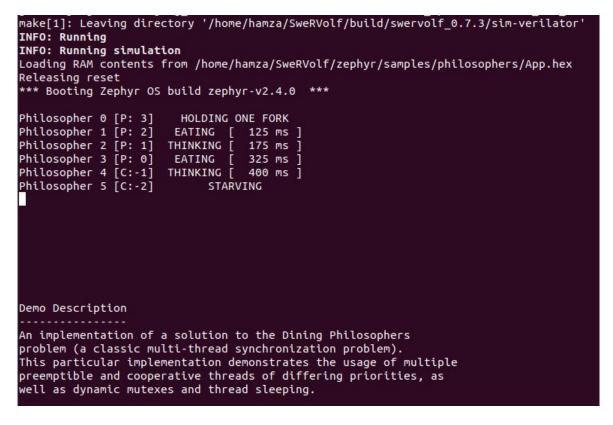

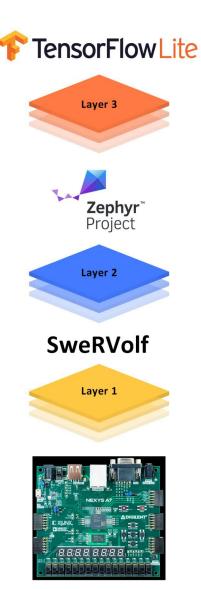

#### Lab 4: Running Zephyr on SweRVolf

Building and Running Zephyr (an RTOS: Real Time Operating System) on SweRVolf.

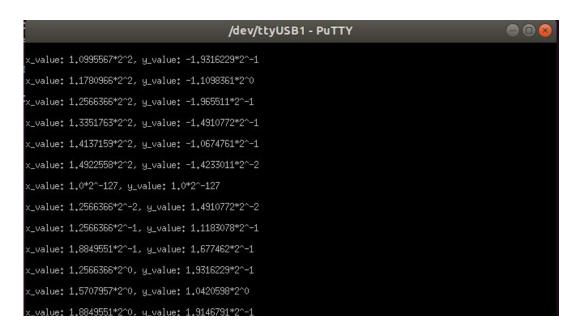

#### Lab 5: Run Tensorflow Hello World

The Hello World example is designed to demonstrate the absolute basics of using TensorFlow Lite for Microcontrollers. This program trains and runs a model that replicates a sine function.

#### Two Courses: RVfpga vs. RVfpga-SoC (1)

RVfpga and RVfpga SoC are two courses. RVfpga focuses more on aspects inside the CPU core. RVfpga-SoC focuses more on aspects outside the CPU core.

instruction

instructions

Lab 0: RVfpga Experiment Overview

Lab 1: Creating a Vivado Project

Lab 2: Programming in C

Lab 3: RISC-V assembly language

Lab 4: Function calls

Lab 5: Image processing: C and assembly

Lab 6: Introduction to 1/O

Lab 7: 7-segment display

Lab 8: Timers

Lab 9: Interrupt driven I/O

Lab 10: Serial Bus

**Programming**

Lab 15: Data Hazards

Lab 16: Control Hazards, Branch Instructions: the

Lab 12: Arithmetic/Logical Instructions: the add

Lab 13: Memory Instructions: the lw and sw

beg Instruction. The Branch.

Lab 14: Structural Hazards

Lab 17: Superscalar Execution

Lab 18: Adding New Features (Instructions,

Lab 11: SweRV EH1 Configuration and

Organization. Performance Monitoring

Hardware Counters) to the Core

Lab 19: Memory Hierarchy. The Instruction Cache.

Lab 20: ICCM and DCCM

Investigate, analyze, and modify the **RISC-V**

core and memory

system.

#### Two Courses: RVfpga vs. RVfpga-SoC (2)

RVfpga and RVfpga SoC are two courses. RVfpga focuses more on aspects inside the CPU core. RVfpga-SoC focuses more on aspects outside the CPU core.

#### **Closing Remarks**

From Verilog, to SoC, to RTOS, to Tensorflow

- All source code visible

A set of 5 labs that walk through students on how to set things up

#### **Acknowledgements**

#### **AUTHORS**

Prof. Sarah L. Harris Prof. Daniel Chaver M. Hamza Liaqat Zubair L. Kakakhel Olof Kindgren Robert Owen

#### **ADVISER**

Prof. David Patterson

#### **CONTRIBUTORS**

Robert Owen

Ivan Kravets

Valerii Koval

Ted Marena

Prof. Roy Kravitz

Prof. Luis Piñuel

Prof. J.I. Gomez

#### **ASSOCIATES**

Prof. Daniel León

Prof. José Ignacio Gómez

Prof. Katzalin Olcoz

Prof. Alberto del Barrio

Prof. Fernando Castro

Prof. Manuel Prieto

Prof Ataur Patwary

Prof. Christian Tenllado

Prof. Francisco Tirado

Prof. Román Hermida

Cathal McCabe

Dan Hugo

Braden Harwood

Prof. David Burnett

Gage Elerding

Prof. Brian Cruickshank

Deepen Parmar

Thong Doan

Oliver Rew

Niko Nikolay

Guanyang He

#### **Sponsors and Supporters**

#### Western Digital.

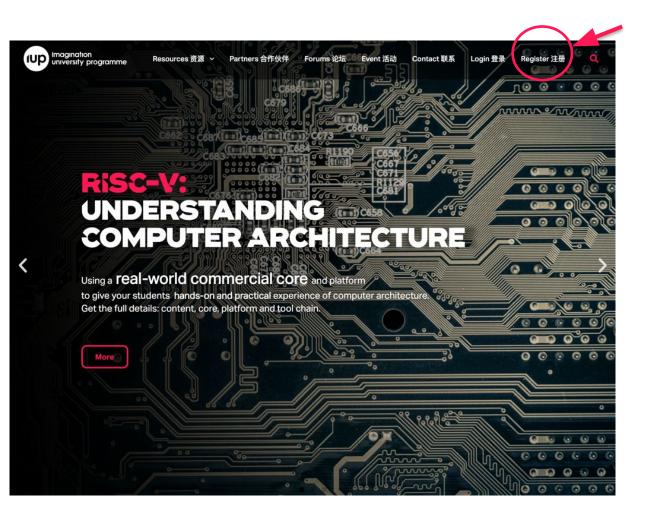

## Join the IUP today, and you can download free teaching materials!

→ university.imgtec.com

#### Our support hub:

- Brochures, info sheets

- Teaching materials, guides, software

- Tutorial video gallery

- Support forums

- References: books, platforms, photos Supported languages: Chinese, English Social media:

- ✔ Robert Owen @UniPgm

- Imagination Technologies

- @ImaginationTech

- ✓ WeChat & Weibo: ImaginationTech

扫一扫上面的二维码图案,加我微信

Please feel free to join the group on WeChat

# C Imagination