# The future of RISC-V has no limits

May 31, 2022

# Leading the RISC-V revolution

2018, 2019, 2020: SiFive Recognized as Most Respected Private Semiconductor Company

### We invented **RISC-V**

SiFive's founders are the same UC Berkeley professor and PhDs who invented and have been leading the commercialization of the RISC-V Instruction Set Architecture (ISA) since 2010

**Si**Five

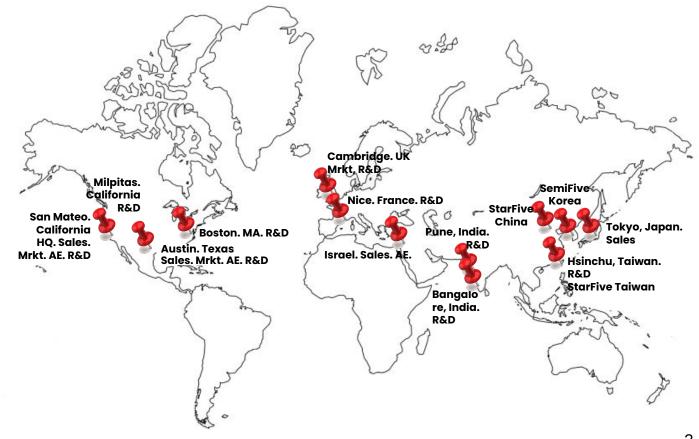

# **SiFive global presence**

#### Presence

- 10+ Offices

- 600+ Employees (420+ Engineers)

- 375+ Tapeouts(OpenFive)

- 300+ Design Win(100 companies)

- 8 of the top 10 semiconductor companies

#### World Leading R&D

- Inventors of RISC-V

- 100+ PhDs

- Highly experienced Processor team (e.g., Arm, Apple, AMD)

Backed by the World's Most Innovative VCs, Silicon Companies

#### SiFive

# **Undisputed leader in RISC-V computing**

Complete portfolio of processors from embedded to high-performance computing

#### CPU Cores

#### 32 and 64-bit Processors

- Microcontrollers, IoT devices, real-time control, control plane processing

- Highly customizable to application specific requirements

- Mature, industry proven designs

SiFive Performance™

#### **64-bit Application Processors**

- Networking, Infrastructure, Enterprise, Consumer

- Highest performance, most advanced

RISC-V Processor available

- Scale out, high performance, processing capabilities with vector compute

#### Al Cores

#### **Scalable AI Processors**

- Edge AI, Cloud, Training, Inference

- Very high performance and efficiency for AI workloads (vector processing)

- Built on top of RISC-V Vectors and the SiFive Intelligence Extensions

# \$2.5B+ V

# Valuation via \$175M Series F Funding

"The market has spoken and made it abundantly clear that RISC-V computing will be competing for the heart of all future computing platforms. As the founder and market leader of RISC-V computing it's our role to lead this ecosystem forward and offer customers advanced computing alternative to Arm and others. This valuation is a validation of our strategy, our incredible team, and our singular focus on building the leading portfolio of high-performance RISC-V compute products in the market. Our customers are signaling strong demand for SiFive to deliver the highest level of performance as quickly as possible."

- Patrick Little, President, Chairman, and CEO, SiFive

# The Top 3 Global ISAs

# x86 RRISC-V° arm

### Recent Announcements

- Introduced new Product family branding aligned to Market Focus

- Entered Performance-driven markets with the fastest commercially available RISC-V IP

- Entered AI & ML-enabled markets with 2 RISC-V vector enabled processor IP products

- Execution of 3 Performance product launches & 3 RISC-V portfolio feature in 1 year

- Intel Foundry Services IP-Alliance Partner with optimized RISC-V IP & Next-Gen Developer Board

#### Design Wins

- Renesas

- Tenstorrent

- Deep Vision

- ArchiTek AiOnIc

- eTopus

- FADU

- Synaptics

- Intel Foundry Services

- Samsung

- Qualcomm

- 0 Others Tess Constrainductor Col

#### Partnerships

- Intel Foundry Services

- IP Optimized for Intel 4 Process Technology

- "Horse Creek" RISC-V Developer Platform in 2022

- Samsung Foundry

- AI SoC Development Platform

- TSMC

- First N5 RISC-V SoC Tapeout

- DARPA

- First RISC-V IP provider

#### **RISC-V Ecosystem**

- Canonical

- Ubuntu OS

- Green Hills

- INTEGRITY RTOS

- SEGGER

- emRun library

- SYSGO

- PikeOS RTOS

- Wind River

- VxWorks RTOS

7

# **SiFive Vector Processors**

May 2022

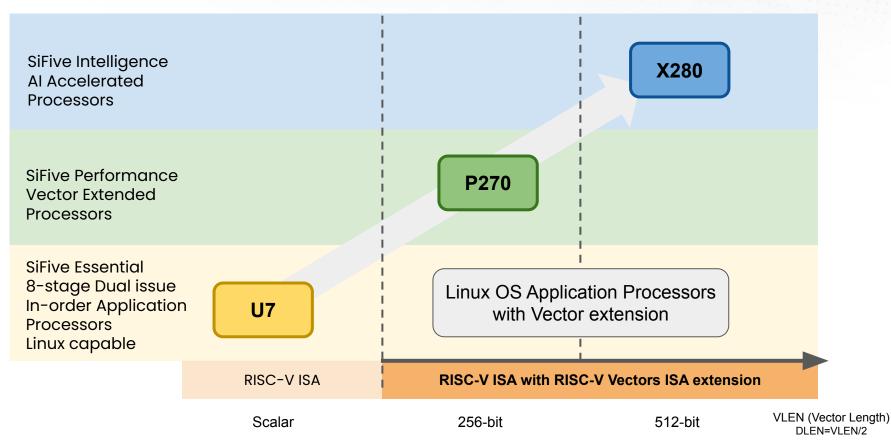

# SiFive RISC-V processor IP portfolio

|                                                            | SiFive <sup>®</sup> Intelligence™                                                                                      | SiFive <sup>®</sup> Pe                                                                              | erformance™                                                                                    |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

|                                                            | X200-Series<br>Optimal Al Acceleration<br>SW + HW Solutions                                                            | P200-Series<br>Performance efficiency<br>Integrated Vectors                                         | P500-Series<br>High performance<br>3-wide OoO Superscalar                                      |  |

|                                                            | X280                                                                                                                   | P270                                                                                                | P550                                                                                           |  |

| 64-bit<br>high-performance<br>Linux capable<br>application | Al processor for Edge and<br>DataCenter ML applications<br>Al acceleration instructions<br>512b vector register length | Optimized performance<br>Vector processor<br>256b vector register length<br>9 Stage Vector pipeline | >8.6 SpecINT2k6/GHz<br>Application processor<br>13 Stage Pipeline<br>Multi-core, multi-cluster |  |

| processors                                                 |                                                                                                                        | SiFive <sup>®</sup> Essential™                                                                      |                                                                                                |  |

|                                                            | 2-Series<br>Power & area optimized<br>2-3 stage single-issue                                                           | 6-Series<br>Performance efficiency<br>8 stage single-issue                                          | 7-Series<br>High performance<br>8 stage Superscalar                                            |  |

|                                                            |                                                                                                                        | U6                                                                                                  | U7                                                                                             |  |

|                                                            |                                                                                                                        | 64-bit, High performance                                                                            | 64-bit, Superscalar perf.                                                                      |  |

|                                                            | S2                                                                                                                     | S6                                                                                                  | S7                                                                                             |  |

| 32/64-bit real time<br>scalable<br>performance deeply      | 64-bit , Area optimized                                                                                                | 64-bit, power efficiency                                                                            | 64-bit, High perf. embedded                                                                    |  |

|                                                            | E2                                                                                                                     | E6                                                                                                  | E7                                                                                             |  |

| embedded<br>processors                                     | Smallest, most efficient                                                                                               | Balanced perf. and efficiency                                                                       | 32-bit, optimized performance                                                                  |  |

A

SiFive

High Performance Broadest Portfolio Relentless Innovation

### **Evolving modern application trends**

Drive towards simplicity, extensibility, and portability

Modern neural network models rapidly evolving Access to the open-source community

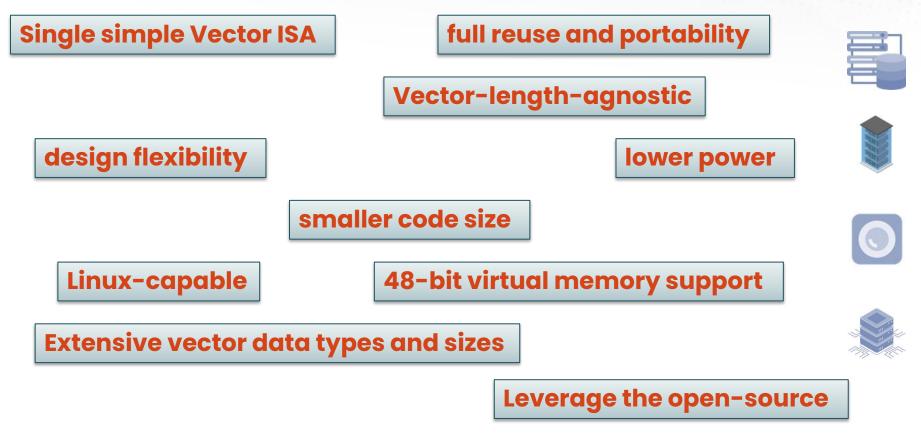

### **RISC-V Vectors benefits**

### **SiFive Vector Processors portfolio**

SiFive

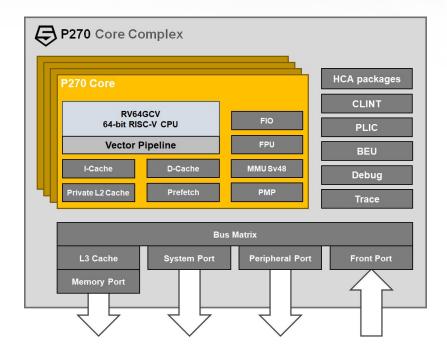

# SiFive Performance P270

64-bit RISC-V Core Virtual Memory, Linux OS Support Hypervisor Extension

Vector Unit executing RISC-V Vector 256-bit Vector Length

8-Stage Dual-Issue In-Order Superscalar Architecture. Decoupled Vector Pipeline

Coherent Multicore Complex Up to 16 cores

SiFive

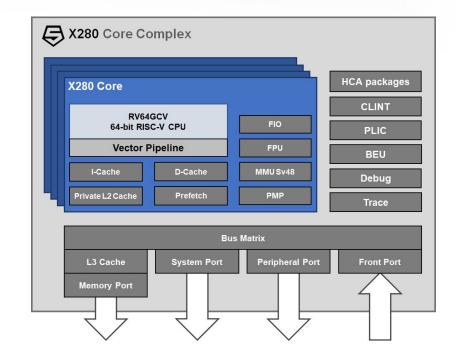

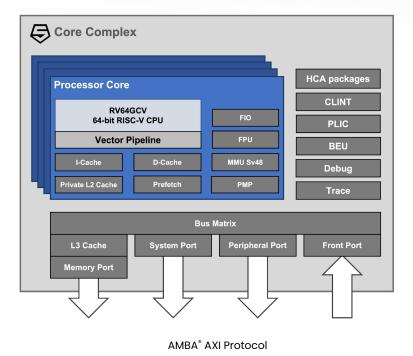

# **SiFive Intelligence X280**

64-bit RISC-V Core Virtual memory, Linux OS Support

512-bit vector register length SiFive Intelligence Extensions Al computation data type support

TensorFlow Lite Framework support Optimized NN operators Wide Range of NN models ported

8-Stage Dual-Issue In-Order Superscalar Architecture. Decoupled Vector Pipeline

Coherent Multicore Complex Core Local Ports for Accelerator Hardware connection

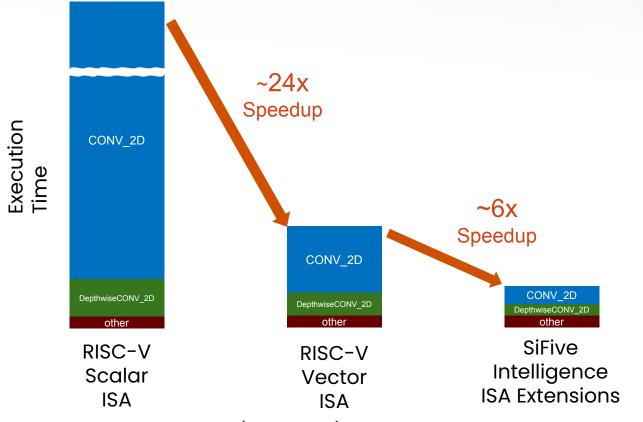

# SiFive Intelligence: Accelerate end-to-end models

MobileNet v1 Inference (batch size=1), VLEN=512

# Scalable solution for wide range of Al use cases

| Wearables SmartHome                                                                                                |                                                                             | Mobile                                                                                                                              | Industrial / Drones           | Data Center (Servers                                                                                                                                                                                                        |  |  |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ~0.1 - 1 TOPS                                                                                                      | ~0.1 - 2 TOPS                                                               | 1 - 5 TOPS                                                                                                                          | 1 - 20 TOPS                   | >100 TOPS                                                                                                                                                                                                                   |  |  |

| <ul> <li>Imaging</li> <li>Sensor / Signal Pro</li> <li>Sensor Filtering / F</li> <li>Speech Recognition</li> </ul> | usion                                                                       |                                                                                                                                     |                               | High Performance Computing<br>(HPC)<br>Dynamic Encryption / Security<br>Audio/Video Streaming /                                                                                                                             |  |  |

|                                                                                                                    | Prediction M                                                                | Iodeling / Control                                                                                                                  |                               | Compression                                                                                                                                                                                                                 |  |  |

| X280                                                                                                               |                                                                             | X280                                                                                                                                | NN<br>Accelerator             | 80 J NN<br>Accelerator                                                                                                                                                                                                      |  |  |

| core with AI op<br>Extensions                                                                                      | ntroller/Applications<br>otimized Vector<br>ofiguration options<br>er power | <ul> <li>Advanced Control<br/>core with AI optimi<br/>Extensions</li> <li>Multi-core configu</li> <li>Connectivity to NN</li> </ul> | ized Vector<br>ration options | Advanced Controller/Application<br>core with AI optimized Vector<br>Extensions<br>Multiple instantiations of<br>Multi-core configuration option<br>Connectivity to large NN<br>accelerators<br>Single unified system memory |  |  |

SiFive

### **SoC connection ports**

Memory Port Highest performance interface to memory

System Port Access to high-bandwidth uncached memory or devices

Peripheral Port Interface with lower speed peripherals

Front Port External Masters for accessing Core Complex devices and ports

FIO Fast I/O Improves the throughput of uncached IO transactions (MMIO) subsystem

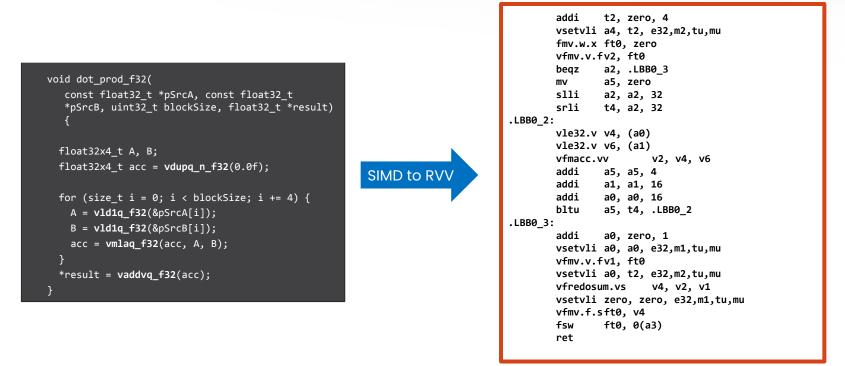

### **Translate SIMD code to RISC-V Vectors**

SiFive Recode: Protect your existing software investment, migrate with confidence

Compiled SiFive Assembly Code

SIMD Source code

# Extending LLVM with auto-vectorizing compiler

- SiFive Toolsuite includes both GCC and LLVM compilers

- SiFive LLVM compiler supports RISC-V Vector intrinsics and auto-vectorization

#### C Code

```

void saxpy (size_t n, const float a,

const float *x, float *y)

{

for (size_t i = 0; i < n; ++i) {

y[i] = a * x[i] + y[i];

}

}

```

#### Auto-Vectorized Code

.LBB0 5: a3, a4, -16 addi vle32.v v26, (a3) vle32.v v27, (a4) vfmul.vv v26, v26, v25 vfmul.vv v27, v27, v25 a3, a5, -16 addi vle32.v v28, (a3) vle32.v v29, (a5) vfadd.vv v26, v26, v28 vfadd.vv v27, v27, v29 vse32.v v26, (a3) vse32.v v27, (a5) addi a7, a7, -8 addi a4, a4, 32 addi a5, a5, 32 a7, .LBB0 5 bnez

#### **Re-Written Using C Intrinsics**

```

LBB0_1:

vsetvli a3, a0, e32,m8,ta,mu

vle32.v v8, (a1)

vle32.v v16, (a2)

vsetvli zero, a3, e32,m8,tu,mu

vfmacc.vf v16, fa0, v8

sh2add a1, a3, a1

vsetvli zero, zero, e32,m8,ta,mu

sub a0, a0, a3

vse32.v v16, (a2)

sh2add a2, a3, a2

bnez a0, .LBB0_1

```

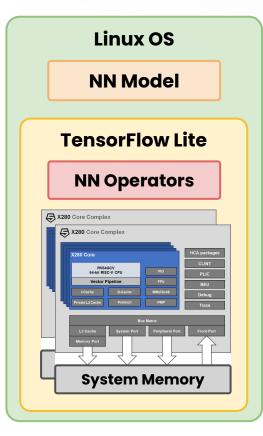

# **Edge Al inferencing running TensorFlow Lite**

Out-of-the-box full software and processor hardware solution with TensorFlow Lite, running under Linux OS

Run NN models in the Object detention, Image Classification, Segmentation; Text and Speech domains

Broad range of optimized NN operators in Float 32-bit and Quantized 8-bit

Enables NN models to be run with minimal porting effort SiFive

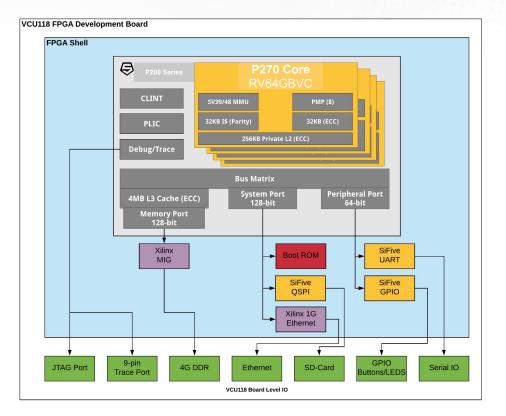

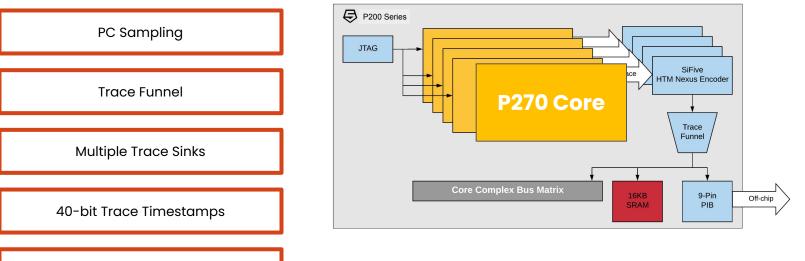

### **FPGA Software Development Platform**

#### Off the Shelf FPGA Platform for Multi-Core Software Development

- Based on Xilinx VCU118 Readily available high-capacity FPGA development board

- Image contains multi-core X280 or P270 and IO subsystem running at 32MHz.

- Ethernet, Serial, Debug, Trace, 4GB DDR

#### Freedom-U-SDK Linux BSP

- SD-Card based Linux boot image with naitive development tools

- Cross-Compiler environment for

User-Space application development

- Yocto based workflow also available for BSP level development

Nexus HTM Trace Encoder

Instrumented Trace (ITC)

B

SiFive

### **Future roadmap and enhancements**

#### SiFive Intelligence

X200-Series Optimal AI Acceleration SW + HW Solutions

#### X280

Al processor for Edge and DataCenter ML applications Al acceleration instructions 512b vector register length

#### **SiFive Performance**

P200-Series Performance efficiency

Integrated Vectors

#### P270

Optimized performance Vector processor 256b vector register length 9 Stage Vector pipeline New, significantly higher performance product line

Enriched feature set

Extended AI software library support

Enhanced support for Custom Accelerators

# SiFive Vectors The Intelligent Choice

SiFive Vector processors:

• High performance and built for scalability

#### SiFive is driving innovation in AI:

- SiFive Intelligence Extensions for optimized

power and performance

- Future proof from evolving ML models

- Easy adoption into existing platforms

RISC-V Vectors are the intelligent choice:

- Consolidating today's fragmented

alternatives

- Open platform with vast open-source community

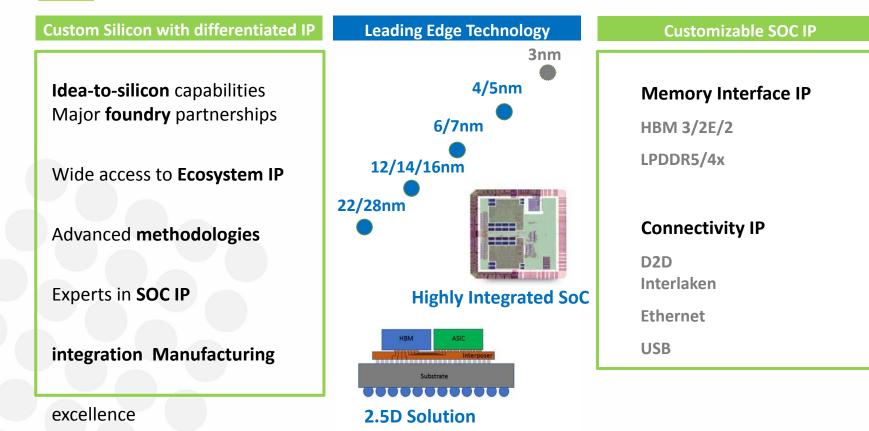

**Custom silicon with differentiated IP**

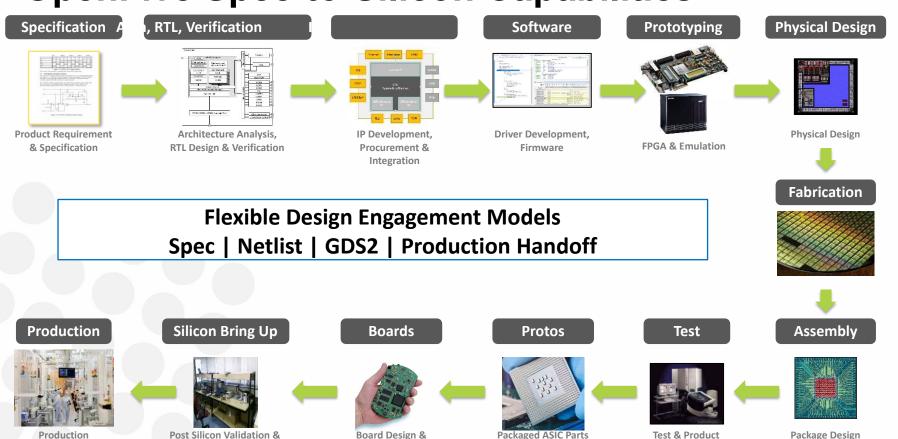

# **Custom Silicon Solutions**

May 2022

# **About OpenFive**

**Custom silicon focus** with differentiated IP

SoC design capabilities from spec-to-silicon

HQ in Silicon Valley, CA with offices globally

**SiFive Business Unit**

A solution-centric silicon company delivering high quality

2022 OpenFive™. All Rights Reserved.

### **Custom Silicon Optimized for your Applications**

**HPC/Compute/Networking**

#### Capabilities

5nm

TSMC 5nm silicon RISC-V, HBM3, D2D I/F

#### 2.5D & Chiplets

AI

| und constraints life                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LANS ST.      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | and the state |

| Contraction of the second seco | A A A         |

- OpenFive Die-to-Die (D2D) IP

- 2.5D Interposer Design Capabilities

- Advanced Packaging: PI/SI Flows

|                            | Processing   | Memory Controller / PH |                          | ntroller / PHY | Security                                                                                           |      | Vision Subsystem                      |        |

|----------------------------|--------------|------------------------|--------------------------|----------------|----------------------------------------------------------------------------------------------------|------|---------------------------------------|--------|

| Subsystem                  |              |                        | 100004984 54144          |                | SiFiveShield                                                                                       |      | CEVA **                               |        |

| €U74                       | <b>₽</b> 074 |                        | IDES AND MITS            |                | Criptia Acceleratory<br>(ARX SHATTANN)<br>Becare Back (Roat of Shar) (RDM)<br>OTF / Rey Managoment |      | Vake DOP CSI.                         |        |

| 🔁 U74                      | € U74        |                        | Platform Management Unit |                |                                                                                                    |      | Al Subsystem                          |        |

| -                          | -            |                        |                          |                | Real-time                                                                                          |      | CEVA Management                       |        |

| €U74                       | € U74        |                        |                          |                |                                                                                                    |      |                                       |        |

| € U74                      | € U74        | 1                      | Customer-specific Accel. |                | LANRT                                                                                              | SP90 | 25908 to 2018 12 Carto                |        |

|                            |              | 8                      | Syster                   | n DMA          | uic .                                                                                              | -    | Video Sub                             | system |

| Sector .                   | Inere        |                        | Low Speed I/O            |                | time<br>Stamp                                                                                      | Teer | III Sente Bidonve<br>Envisite-Geciste |        |

| 10.00                      |              | 1                      | INAT 1990                |                | Graphics/Display                                                                                   |      | PEC Crossin Decade                    |        |

| High S                     | ITO Marc     |                        | uc                       | P458           | 0FU 35/80 Accelerations                                                                            |      | Audio Subsystem                       |        |

|                            | -            |                        |                          | MUT/MIC        | Englay Contendar                                                                                   |      | CEVA AND OF                           |        |

| Gegatelite.<br>Vac ficture | PCIe Gan 8   |                        | Die-                     | 2.010          | HEME 2.0 OF                                                                                        |      |                                       | Ande   |

#### **RISC-V based Apps Processor SOC**

2022 OpenFive™. All Rights Reserved.

# **OpenFive Spec-to-Silicon Capabilities**

Manufacturing

2022 OpenFive<sup>™</sup>. All Rights Reserved.

& Logistics

Software Bring-up

& Assembly

Engineering

# Deep Partnerships and Engagements with Major Foundries

#### TSMC Value Chain Aggregator (VCA)

Early access to PDKs, foundry IP,

preferred business terms

Taped-out 250+ designs

Leading-edge engagements (16, 12, 7, 6, 5nm)

#### **Global Foundries**

22FDX platform ideal for wearable & hearables Multiple mission critical application engagements in 22FDX, 12LP+

OpenFive IP developed in 22FDx and 12LP+

# OpenFive SoC IP Portfolio – Customizable and Differentiated openfive

#### Connectivity

- 400/800GbE MAC

- RS/KR/KP FEC

- FlexE

- LL Chip2Chip Controller

- AXI add-on

#### **Memory Interfaces**

- HBM2E PHY & Controller

- HBM3 PHY & Controller\*

- LPDDR5/4X PHY

- AXI add-on

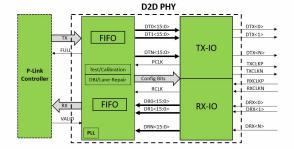

#### Chiplets

- Die-2-Die PHY

- Universal Die-2-Die Controller

- Light weight FEC

- Ethernet Chiplet subsystem\*

#### System IPs

- PVT Sensors

- Custom SRAMs/TCAMs

- PLLs

- DLLs

- LVDS IOs

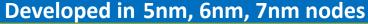

#### Soft and Physical IP on leading process nodes

### OpenFive Products – Custom Silicon Solutions with Differentiated IP

### Custom Silicon Experience with High Performance SoCs

# **OpenFive IP Portfolio**

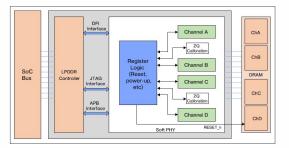

Memory Interface IP Subsystems HBM3, HBM2, HBM2E, LPDDR5/4X

#### Connectivity IP Die-2-Die(D2D), Interlaken(C2C), Ethernet, USB

System & Peripheral IP DMA, SPI & more ...

# OpenFive IP Sub-Systems - Differentiated and Customizable Openfive

LPDDR5

#### HBM

#### https://openfive.com/lpddr5-4x-ip-subsystem/

**D2D**

https://openfive.com/die-to-die-ip-subsystem/

#### 2022 OpenFive<sup>™</sup>. All Rights Reserved.

# Creating The Next Wave: Chiplet Solutions Openfive

Shrac

### **PROCESSOR CHIPLETS**

#### Scalable architecture:

• Add dies to increase performance

#### Cost effective:

• Better yields with smaller die

#### Time to Market:

• Combine custom SoC + available die

Chip Size limit : maximum reticle size Very large Die : Lower Yield, Power Limit Bandwidth limit: Number of IO on die

Time to Market: Design complexity and IP readiness

### **IO CHIPLETS**

- Higher Bandwidth:

- Increase # of IO

#### Time to Market:

- Mix die from different nodes

- Use pre-verified chiplets

#### Lower Development Cost

• Share chiplets across products

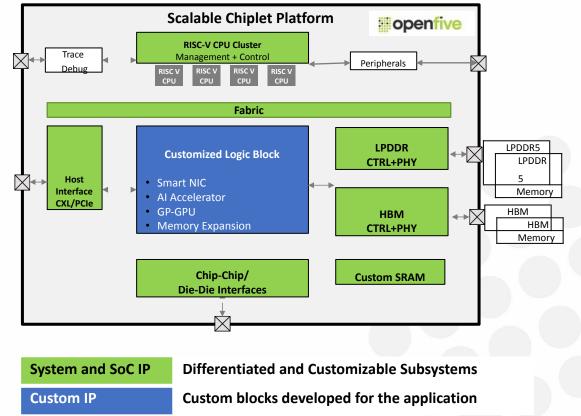

# OpenFive Scalable Chiplet Platforms (Compute, Memory and popenfive Connectivity)

- Die-to-Die Subsystem:

- 640Gbps throughput D2D (single word)

- Scalable up to 4Tbps/mm on beachfront

- Chip-to-Chip Subsystem:

- 32G NRZ SerDes to 112G PAM4 SerDes

- Scalable from 1 to N Serdes

- Memory Subsystem:

- 16/32-bit LPDDR5/4x at 6.4Gbps

- 8/16-channel HBM IOs at up to 7.2Gbps

- Custom SRAM Macros that can achieve up to 40% Area/Power benefits at up to 2GHz

- CPU Subsystem:

- 64b RISC-V multi-core, multi-cluster CPU

- P-I-E Depending on application needs

- Advanced 2.5D Package:

- Interposer to connect multiple die on advanced nodes – silicon proved!

Custom silicon with differentiated IP OpenFive RISC-V Based AI Vision SoC Platform

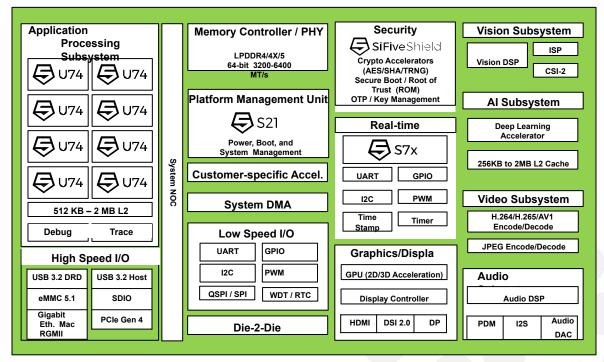

# **OpenFive Al Vision Platform**

- Customizable Application Processor Chassis

- Powerful Linux Capable RISC-V CPUs

- High Performance LPDDR4/5 for data processing

- Heterogenous subsystems to offload and accelerate various usages

- Reuse of pre-hardened subsystems

- Focus on your key differentiator

openfive

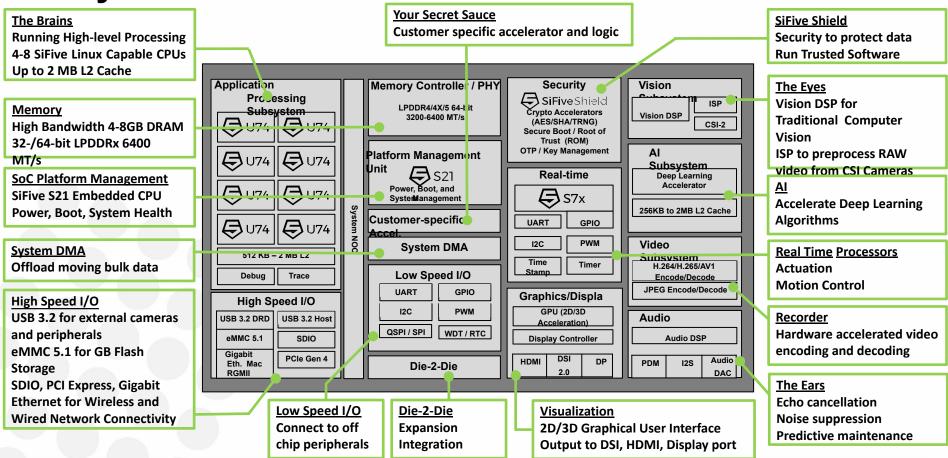

# Key Features of an Al Vision Platform

openfive

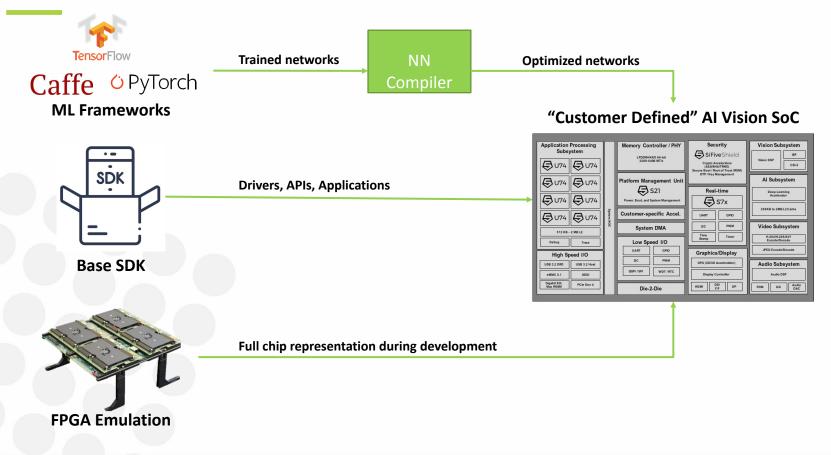

# Software Development for the AI Vision Socopenfive

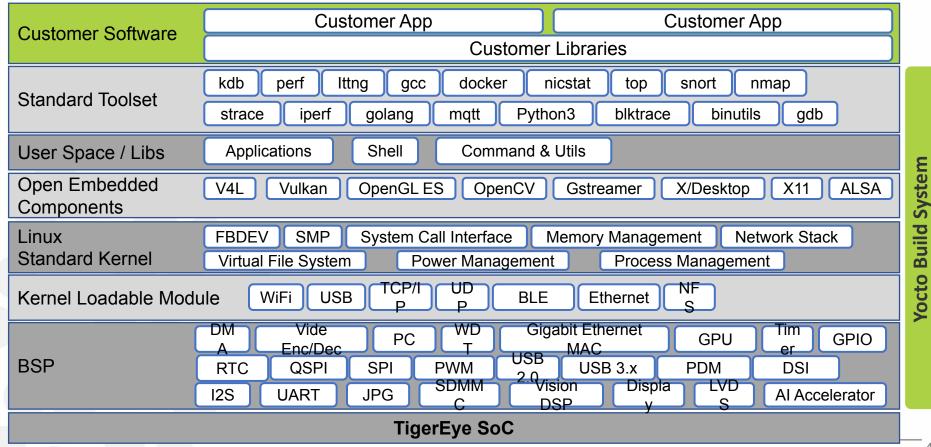

# **Software Stack**

# **Thank you**