## **Contributions**

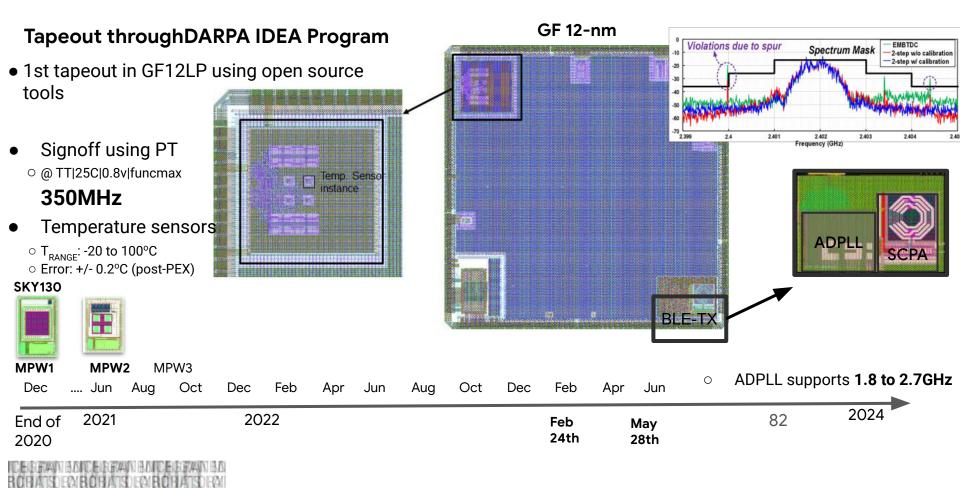

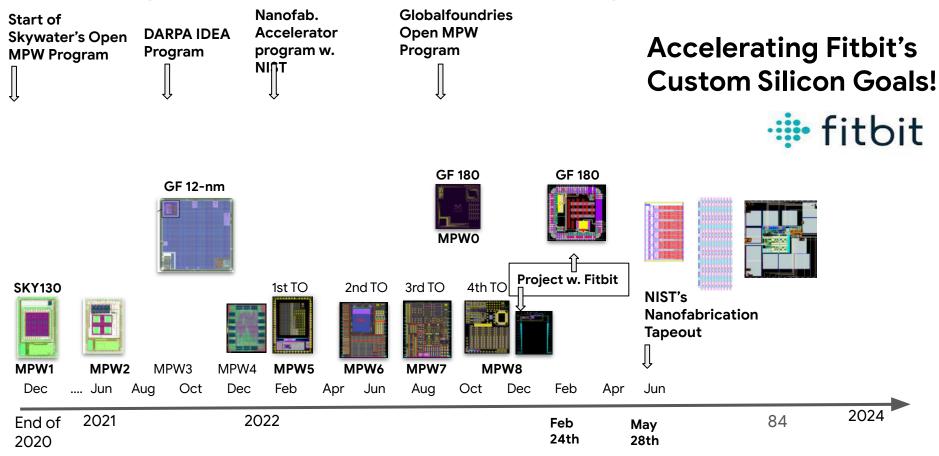

Open-Source IC & tapeouts → 1<sup>st</sup> Open Silicon Results

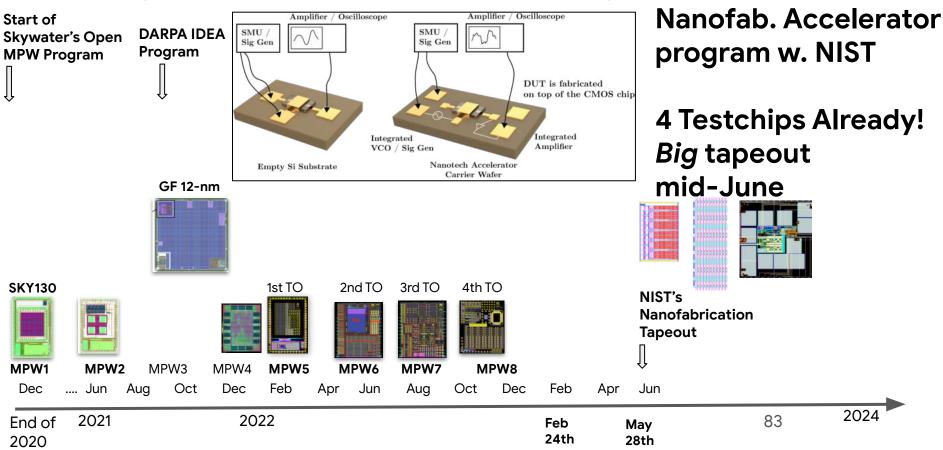

**NIST Nanofabrication Accelerator**

- → 1<sup>st</sup> Open Nanotechnology Platform

- → Cryogenic CMOS

Low-Power IC Design

→ **Rapid** Prototyping for Wearables

Hardware Security → 1<sup>st</sup> Open Root of Trust SoC

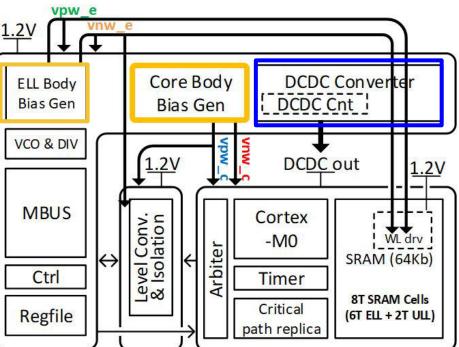

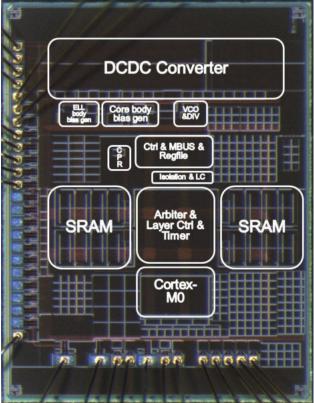

#### Low-Power SoC for Wearables Previous Work

- Taped out in 55-nm DDC (Fujitsu) and published in ISSCC 2019 and JSSC 2020

- Power Domains

- **1.2v**

- DC-DC converter

- Charge Pumps

- Clock generator

- Controller

- DC-DC Output

- Cortex-M0 Processor

- 8KB SRAM

A 6.4 pJ/Cycle Self-Tuning Cortex-M0 IoT Processor Based on Leakage-Ratio Measurement for Energy-Optimal Operation Across Wide-Range PVT Variation

Reconfigurable switched-cap. DC-DC converter

#### Low-Power SoC for Wearables Previous Work

| Technology                        | 55nm DDC process                    |

|-----------------------------------|-------------------------------------|

| Die Size                          | 1500µm x 1970µm                     |

| CPU                               | ARM Cortex M0                       |

| On-chip Memory                    | 8KB SRAM                            |

| Supply Voltage                    | 1.2V                                |

| Power<br>Management<br>Scheme     | On-chip Closed-loop<br>MEP-tracking |

| CPU & Memory<br>Operating Voltage | 0.48V ~ 0.75V                       |

| Clock Frequency                   | 100kHz ~ 6MHz                       |

| Power                             | 7.95µW @ TT, 25°C ,1MHz             |

| Minimum Energy<br>Per Operation   | 6.4pJ/cycle @ 0.55V, 500kHz         |

A 6.4 pJ/Cycle Self-Tuning Cortex-MO IoT Processor Based on Leakage-Ratio Measurement for Energy-Optimal Operation Across Wide-Range PVT Variation

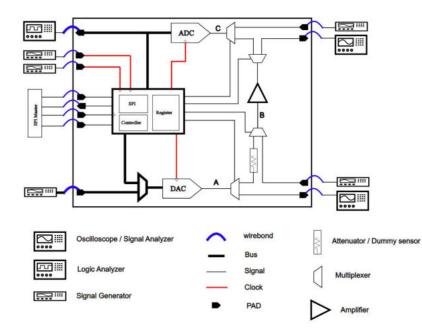

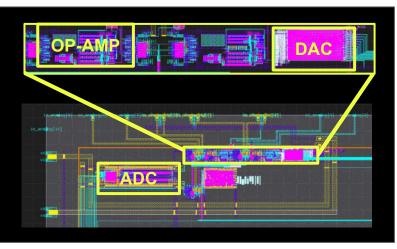

#### Low-Power SoC for Wearables Rapid Prototyping - AFE

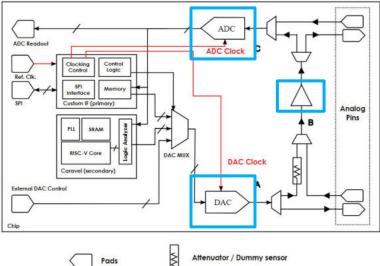

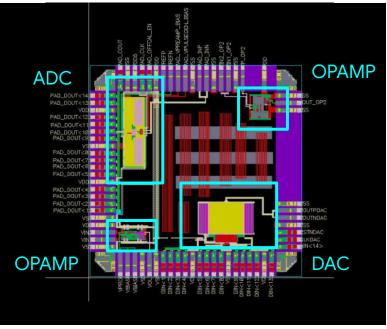

Sensor Test Harness in Skywater 130 Lab on a Chip Concept

Test Harness for Rapid Prototyping

#### Low-Power SoC for Wearables Rapid Prototyping - AFE

GF180 (Feb 2023)

### **On-Going Projects & Contributions**

Open-Source IC & tapeouts → 1<sup>st</sup> Open Silicon Results

# **NIST Nanofabrication Accelerator**

- → 1<sup>st</sup> Open Nanotechnology Platform

- → Cryogenic CMOS

- Low-Power IC Design

→ *Rapid* Prototyping for Wearables

Hardware Security → 1<sup>st</sup> Open Root of Trust SoC

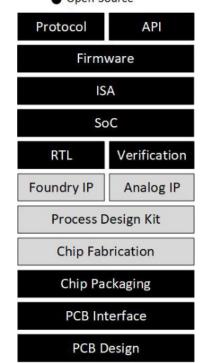

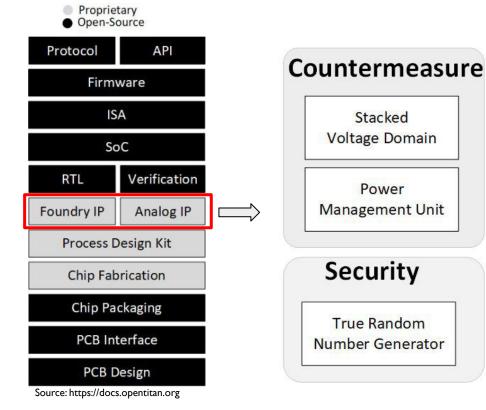

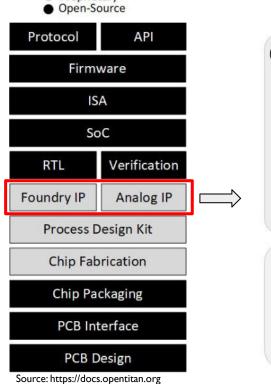

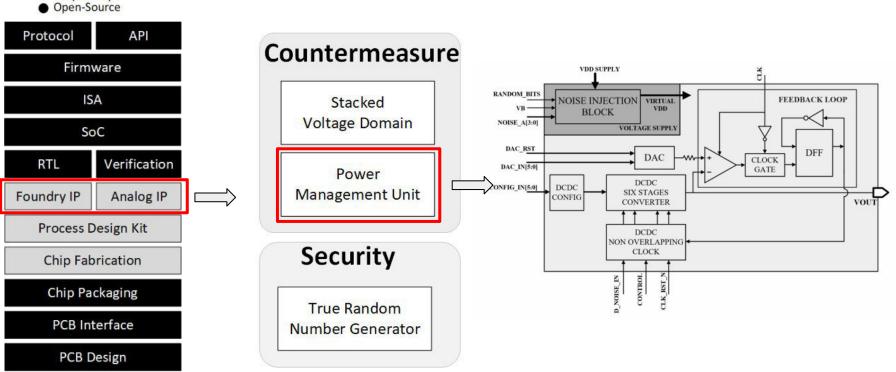

## **Open-Source** Opentitan RoT

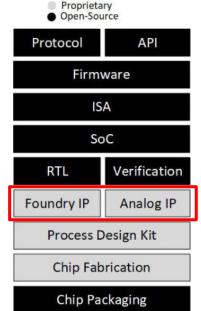

Proprietary

Open-Source

THERAN ANTE

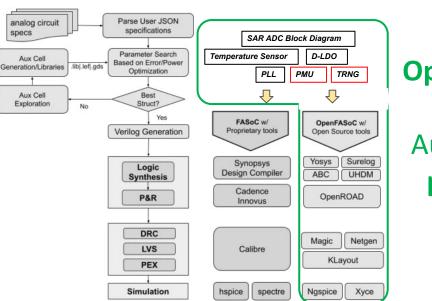

#### **Open-Source Opentitan RoT** With **OpenFASOC** Generated Blocks

PCB Interface

PCB Design

Source: https://docs.opentitan.org

TEERAN ANTE

Automated **portable** analog

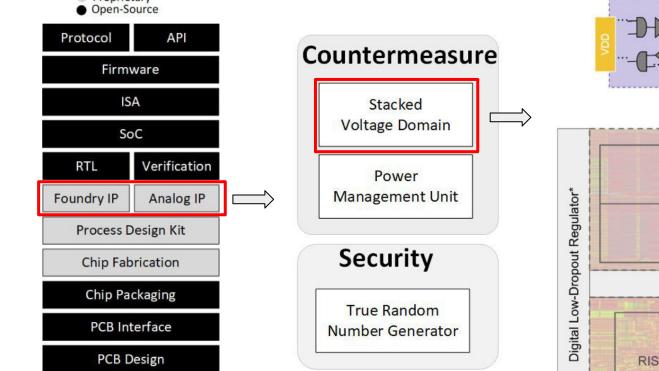

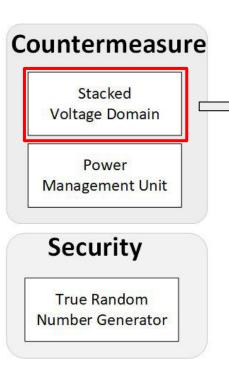

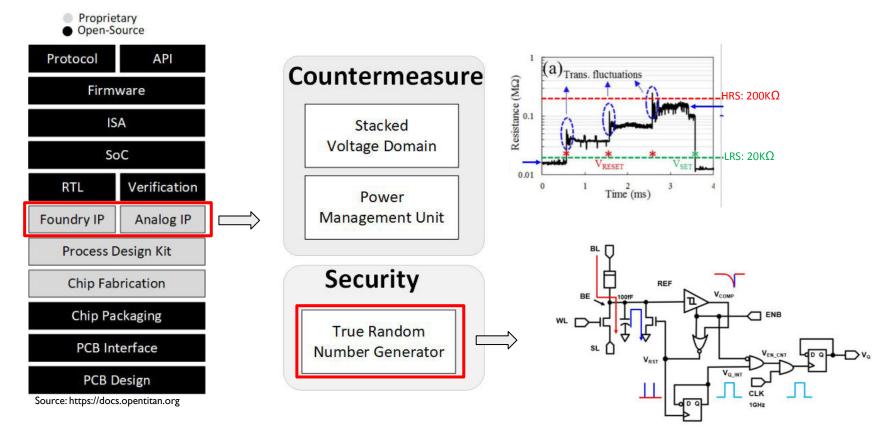

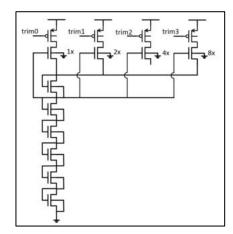

## **Proposed Techniques**

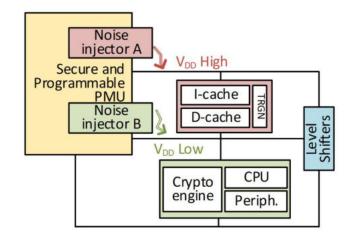

- Power Side-Channel Attack Resistant noise injection

- Cryptographic AES SoC in Stacked Voltage Domain

- Secure Programmable PMU with

- **ReRAM-based TRNG**

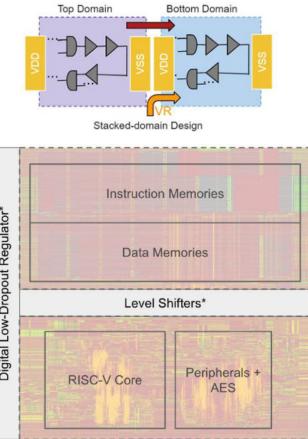

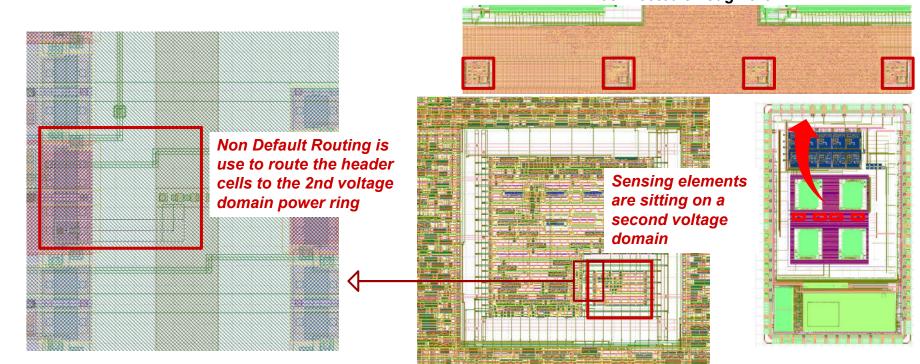

#### Cryptographic AES SoC Stacked Voltage Domain

Source: https://docs.opentitan.org

## **Open-Source** Opentitan RoT

Voltage Stacked SoC

- 1st version of the PMU

- SoC includes:

- Crypto engine

- IBEX Core

Goals:

- Perform DPA and check the efficiency of the power obfuscation techniques

- New open-source PPA (silicon results)

#### **Open-Source Opentitan RoT** Secure Programmable PMU with Noise Injection

Source: https://docs.opentitan.org

## **RRAM based TRNG**

BOBATSDEMBOBATSDEMBOBATSDEM

NIST

ROHATSDEM BOHATSDEM BOHATSDEM

intel.

foundry

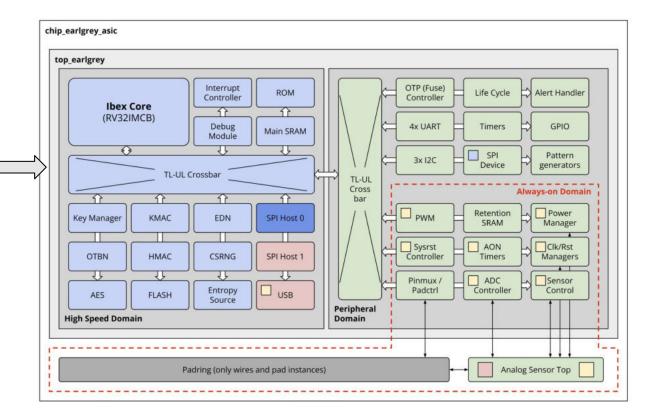

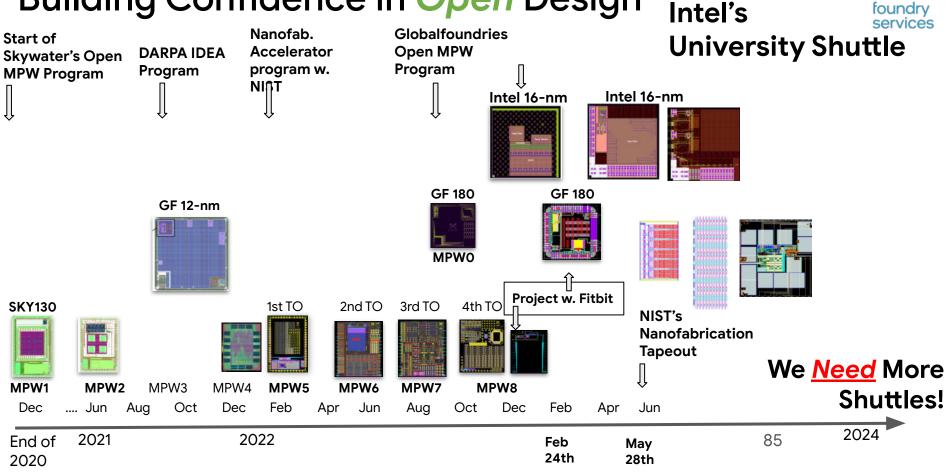

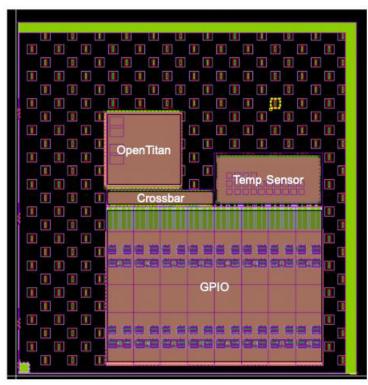

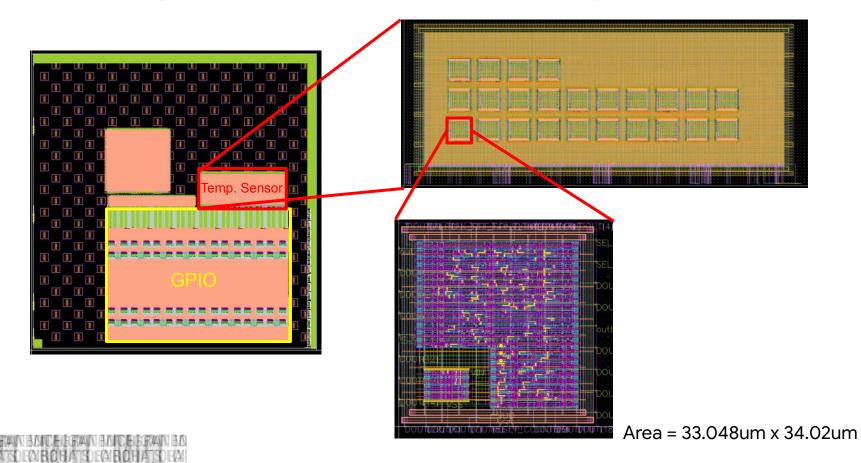

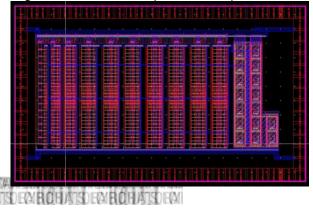

# Tape Outs in Intel 16 - OpenTitan SoC

- Tapeout in Intel 16nm using OS tools

- PD and timing optimization using OpenROAD

- Used a modular flow to smoothly fill-in the gaps using proprietary tools

- Temperature Sensor RTL to GDS flow is fully Open-Source

Floorplan of Intel 16 tapeout Including Opentitan, Temperature sensor array and crossbar using OpenROAD

86

## 24 Temperature Sensors Array

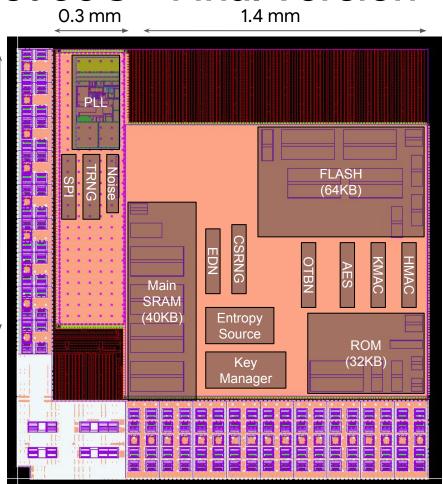

## **OpenTitan Root of Trust SoC - Final Version**

- All digital edge tracing TRNG

- Tunable Noise Injection

- On-chip high speed PLL

- OpenTitan security subsystem

- Crypto + Key Manager

- Secure Memory

| Frequency   | 28MHz               |

|-------------|---------------------|

| Memory Size | 16KB                |

| Gate Count  | 20K                 |

| # of Macros | 26                  |

| Area        | 2.18mm <sup>2</sup> |

1.25 mm

# What is next?

ICEORIAN ENCERERAN ENCERERAN EN ROBATSDEM ROBATSDEM ROBATSDEM

#### Make custom silicon easier to build, at scale, just like software

"My god, it's full of software!"

# \$ gcc -OSilicon

#### CONDA Packaging conda-eda github.com/hdl/conda-eda

conda install --channel litex-hub \

open\_pdks.sky130a \

openlane \

xls

CONDA Packaging conda-eda github.com/hdl/conda-eda

conda install --channel litex-hub \

open\_pdks.sky130a \

openlane \

xls

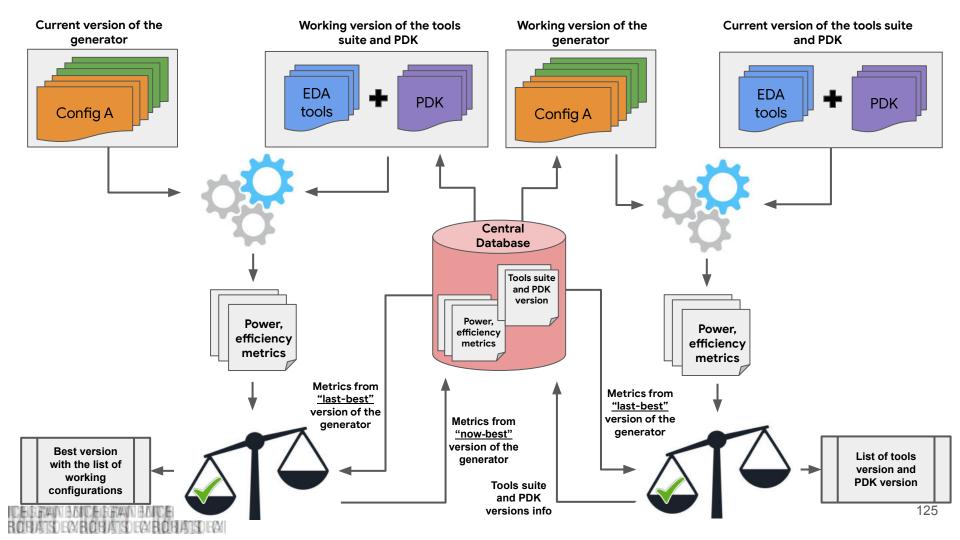

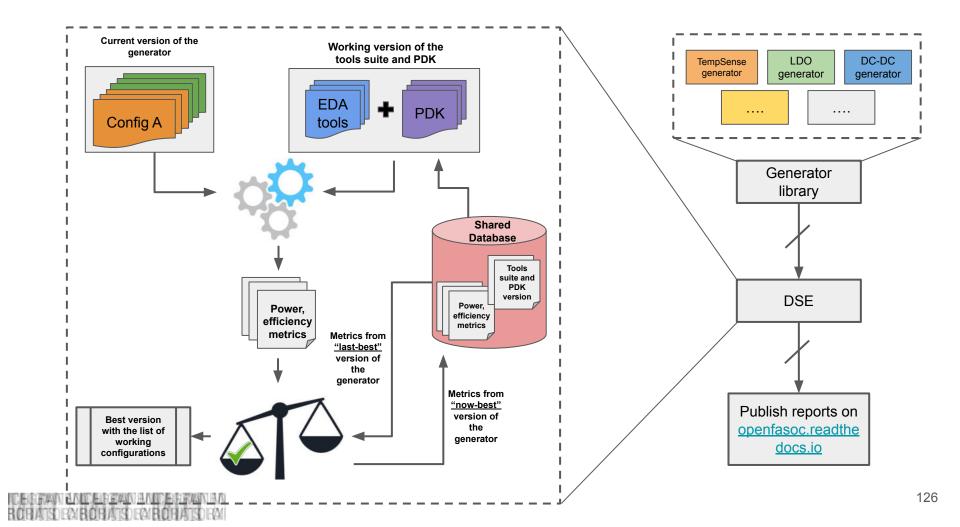

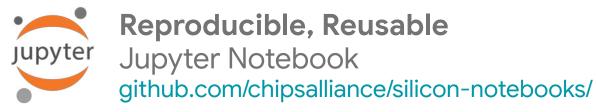

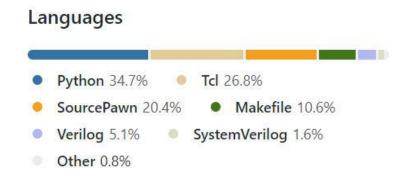

OpenFASOC GitHub Repo is mainly Code and Documentation

- OpenFASOC GitHub Repo is mainly Code and Documentation

- Auditable and Transparent

- Regression Tests

- Systematic Metrics Extraction

- Dashboards

- OpenFASOC GitHub Repo is mainly Code and Documentation

- Auditable and Transparent

- Regression Tests

- Systematic Metrics Extraction

- Dashboards

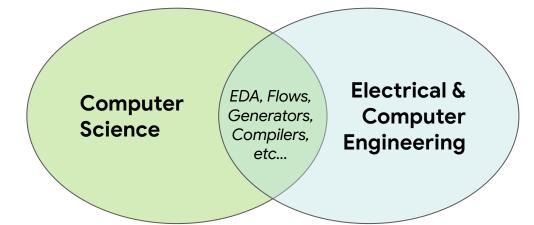

- Analog Automation requires collaborative Work

- EDA, Analog/RF/Circuits, Software

```

"My god,

it's full of software!"

```

# Bridging Gaps between **EE & CS**

• Existing efforts around Open-Source IC design

#### **SSCS PICO Chipathon**

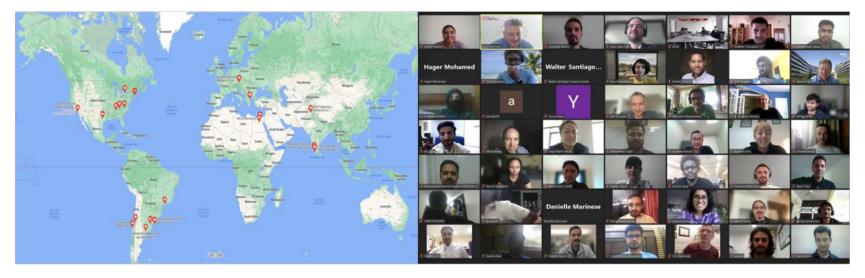

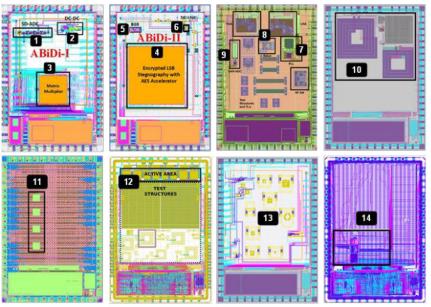

- 2021: 61 submissions, 18 selected (11 taped out)

- 2022: 54 submissions, 22 selected (14 taped out)

2022 selected teams from 10 countries, 5 continents

June 22, 2022, kick-off meetup with over 100 attendees

#### 2021 Chipathon

|    | Function                                            | Team                                      | Chip URL                          |  |

|----|-----------------------------------------------------|-------------------------------------------|-----------------------------------|--|

| 1  | 5G bidirectional amplifier                          | Pakistan3<br>(FAST National University)   |                                   |  |

| 2  | Wireless power transfer unit                        | Pakistan2<br>(FAST National University)   | https://efabless.com/projects/560 |  |

| 3  | Variable precision fused<br>multiply-add unit       | Pakistan1<br>(FAST National University)   |                                   |  |

| 4  | Oscillator-based LVDT readout                       | India2<br>(Anna University)               | https://efabless.com/projects/474 |  |

| 5  | Temperature sensor                                  | India1<br>(Anna University)               |                                   |  |

| 6  | GPS baseband engine                                 | India3<br>(Anna University)               |                                   |  |

| 7  | Ultra-low-power analog<br>front-end for bio signals | Brazil2<br>(U. Federal de Santa Catarina) | https://efabless.com/projects/476 |  |

| 8  | TIA for quantum photonics<br>interface              | USA4<br>(University of Virginia)          | https://efabless.com/projects/470 |  |

| 9  | Bandgap reference                                   | Egypt<br>(Cairo University)               | https://efabless.com/projects/473 |  |

| 10 | Neural network for<br>sleep apnea detection         | USA2<br>(University of Missouri)          |                                   |  |

| 11 | SONAR processing unit                               | Chile<br>(University of the Bio-Bio)      | https://efabless.com/projects/540 |  |

- Paid runs via Efabless chipIgnite (130 nm SkyWater)

- All designs are open source

Magazine article: "SSCS PICO Contestants Cross the Finish Line," https://ieeexplore.ieee.org/document/9694491

#### 2022 Chipathon

|    | Function                                                   | Team                                                                                                                                                                           | ChipURL                                        |

|----|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 1  | Spatial Sigma-Delta ADC                                    | Pakistan1<br>(FAST National University)                                                                                                                                        |                                                |

| 2  | On-Chip DCDC Converter<br>with Fast Transient<br>Response  | Pakistan4<br>(FAST National University)                                                                                                                                        | https://platform.efables<br>.com/projects/1486 |

| 3  | Matrix Multiplier for AI<br>atthe Edge                     | Pakistan7<br>(FAST National University)                                                                                                                                        |                                                |

| 4  | Encrypted LSB<br>Steganography with AES<br>Accelerator     | Pakistan2<br>(FAST National University)                                                                                                                                        |                                                |

| 5  | CMOS Bandgap Reference                                     | Pakistan3<br>(FAST National University)                                                                                                                                        | https://platform.efable<br>.com/projects/1443  |

| 6  | Self-Interference<br>Cancellation LNA                      | Pakistan4<br>(FAST National University)                                                                                                                                        |                                                |

| 7  | Sub-Sampling PLL for<br>SerDes Applications                | Austria<br>(Johannes Kepler Univ., Linz)                                                                                                                                       |                                                |

| 8  | 60 GHz Demonstrator Chip                                   | Brazil<br>(University of São Paulo)                                                                                                                                            | https://platform.efable<br>.com/projects/1431  |

| 9  | Low-Power 10-bit SAR ADC                                   | USA1<br>(University of Alabama & MIT Lincoln Lab)                                                                                                                              |                                                |

| 10 | Boost Converter for<br>Battery-Powered IoT<br>Applications | Greece<br>(Aristotle University of Thessaloniki)                                                                                                                               | https://platform.efable<br>.com/projects/1457  |

| 11 | Radiation-Hardened ALU                                     | USA2<br>(North Carolina A&T State University)                                                                                                                                  | https://platform.efable<br>.com/projects/1593  |

| 12 | DC-DC Buck Converter for<br>CubeSat                        | Chile¹/Argentina²/Uruguay³<br>¹Universidad Técnica Fed. Santa María<br>²Universidad Nacional del Sur & Instituto<br>Nacional de Tecnología Industrial<br>³Universidad Católica | https://platform.efable<br>.com/projects/1427  |

| 13 | Electrochemical Water<br>Quality Monitoring                | USA5<br>(University of Tennessee)                                                                                                                                              | https://platform.efable<br>.com/projects/1469  |

| 14 | Mix-Pix - A Mixed-Signal<br>Circuit for Smart Imaging      | Chile<br>(Universidad del Bío-Bío)                                                                                                                                             | https://platform.efable                        |

Magazine article: "Meet the SSCS PICO Chipathletes," https://ieeexplore.ieee.org/document/9950763

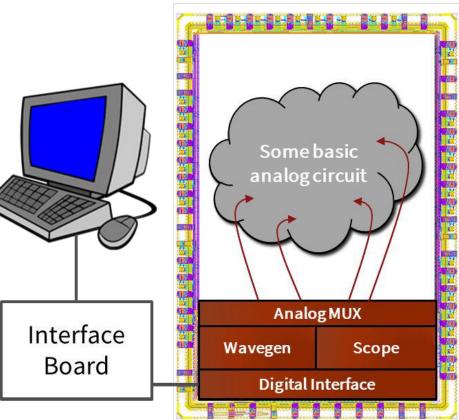

#### 2023 Chipathon (Ongoing)

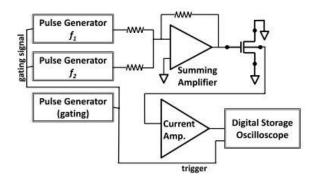

- Build on-chip waveform generator and "oscilloscope" macros

- Collection of generally useful IP blocks

- Enable testing of low frequency analog circuits using only a PC

- Tape out first prototypes and improve with community over time

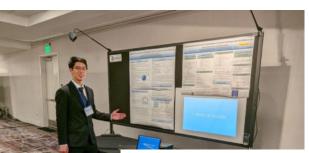

# Notebook Code a Chip Competition at ISSCC'23

2023

| Name                   | Affiliation                                                        | Notebook Title                                                                                 |

|------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Yihai Zhang            | Tsinghua-Berkeley Shenzhen<br>Institute, Tsinghua University China | GreenRio 2: A Linux-compatible RISC-V Processor<br>Developed with A Fully Open-Source EDA Flow |

| Anawin<br>Opasatian    | University of Tokyo (Japan)                                        | Bernstein-Yang Modular Inversion with XLS/OpenLane                                             |

| Mauricio<br>Montanares | University of Concepción (Chile)                                   | Sonar On Chip Project                                                                          |

| Nealson Li             | Georgia Institute of Technology<br>(USA)                           | Coordinate Rotation Digital Computer (CORDIC) with OpenLane                                    |

| HyungJoo Park          | Hanyang University (South Korea)                                   | Scan Register layout generation using laygo2                                                   |

| Ali Hammoud            | University of Michigan (USA)                                       | OpenFASoC: Digital LDO Generator                                                               |

| Nimish Shah            | KU Leuven (Belgium)                                                | DPU: DAG Processing Unit for probabilistic ML and sparse matrix algebra                        |

Muritikurg, Binghua-Berleiny Shenzhen Instituter, Tsinghua University (Chin Anawim Opeastian, University of Concepción (Chile) Anaucicio Montanares, University of Concepción Hummoud, University of Michigan (USA) Animah Shah, KU Leuven (Belgium)

CODE-A-CHIP TRAVEL GRANT AWARD

# Notebook Code a Chip Competition at VLSI'23

## Example: Winner of VLSI 2023 Code-a-Chip Contest

CO Open in Colab

## Design and Optimization of Analog LDO with Relational Graph Neural Network and Reinforcement Learning

Zonghao Li Team, March 2023 SPDX-License-Identifier: Apache-2.0

| Name                                                                            | Affiliation           | IEEE Member | SSCS Member |

|---------------------------------------------------------------------------------|-----------------------|-------------|-------------|

| Zonghao Li (Lead)<br>Email ID: zonghao.li@isl.utoronto.ca                       | University of Toronto | Yes         | Yes         |

| Anthony Chan Carusone (Advisor)<br>Email ID: tony.chan.carusone@isl.utoronto.ca | University of Toronto | Yes         | Yes         |

https://github.com/sscs-ose/sscs-ose-code-a-chip.github.io/blob/main/VLSI23/accepted\_notebooks/ldo\_rgcn\_rl/ldo\_rgcn\_rl.ipynb

# "Code-a-Chip" Notebook Competition at VLSI'23 - Kyoto

- IEEE Solid-State Circuits Society (SSCS) Open-Source Ecosystem (OSE)

- <u>https://github.com/sscs-ose/sscs-ose-code-a-chip.github.io</u>

/ Home / Membership / Awards / IEEE SSCS "Code-a-Chip" Travel Grant Awards

IEEE SSCS "Code-a-Chip" Travel Grant Awards

### IEEE SSCS "Code-a-Chip" Travel Grant Awards at the 2023 Symposium on VLSI Technology and Circuits

The IEEE SSCS Code-a-Chip Travel Grant Award was created to:

1. Promote reproducible chip design using open-source tools and notebook-driven design flows and

2. Enable up-and-coming talents as well as seasoned open-source enthusiasts to travel to IEEE SSCS conferences and interact with the leading-edge chip design community.

3 202 ISCAS ଡ Session Monday AM 11:30 - 13:00 Review of the First Silicon Results in the Open Source Ecosystem Room: San Carlos III (Marriott) Session Chair(s): Mehdi Saligane, University of Michigan Priyanka Raina, Stanford University

#### 11:30

2273: An Open Source Compatible Framework to Fully Autonomous Digital LDO Generation

Yaswanth Kumar Cherivirala, Mehdi Saligane, David Wentzloff University of Michigan, Ann Arbor, United States

#### 11:48

#### 2290: Design of Cryo-CMOS Analog Circuits Using the Gm/ID Approach

Christian Enz, Hung-Chi Han École Polytechnique Fédérale de Lausanne, Switzerland

#### 12:06

#### 2314: SRAM Design with OpenRAM in SkyWater 130nm

Jesse Cirimelli-Low{2}, Muhammed Hadir Khan{2}, Samuel Crow{2}, Amogh Lonkar{2}, Bugra Onal{2}, Andrew Zonenberg{1}, Matthew Guthaus{2} {1}IO Active, United States; {2}University of California, Santa Cruz, United States

#### 11:24

#### 2326: An Open-Source 4x8 Coarse-Grained Reconfigurable Array Using SkyWater 130 nm Technology and Agile Hardware Design Flow

Po-Han Chen, Charles Tsao, Priyanka Raina Stanford University, United States

#### 12:42

2327: Open-Source, End-to-End Auditable Tapeout of Hardware Cryptography Module Anish Singhani

Carnegie Mellon University, United States

# 180 Attendees!! Record attendance among all workshops at VLSI Symposium

### Open Source PDKs and EDAs, Community Experiences toward Democratization of Chip Design

Organizer : Makoto Ikeda (The University of Tokyo)å Mehdi Saligane (University of Michigan)

Since its launch in 2020, the Open MPW shuttle program has received over 500 to designers' experiences, including measured results, foundry perspectives, an

#### About Makoto Ikeda

Makoto Ikeda received his BE, ME, and Ph.D. degrees all in EE department of d.lab, the University of Tokyo. This workshop is co-organized with Dr. Mehdi S

1. Design experience: "The Journey of Two Novice LSI Enthusiasts: Tr Communications and Yuki Azuma, University of Tsukuba

2. From Zero to 1000 Open Source Custom Designs in Two Years, Mo

3. The SKY130 Open Source PDK: Building an Open Source Innovation

4. Open Source Chip Design on GF180MCU - A foundry perspective, Karthik Chandrasekaran, Globarte

# The end!

**Bonus slides**

## **Implementation Challenges**

- A. The quantized behavior is best shown in single-defect gate interfaces.

- a. When the device operates with a single defect, the CP current difference is either fully present or not, there is no middle values caused by randomness.

- b. It demands:

- i. Heavy binning to select a candidate device

- ii. Advanced process node that doesn't produce too much defects

- B. The current is extremely small (<10fA @ 40MHz, L/W=50nm/100nm [1])

- a. Leakages are everywhere. The author suggests DRAM-optimized technology to minimize junction leakage [1].

- b. Considering lock-in amplify or other low-level signal measurement techniques. [4, 5]

- c. Direct amplification of this signal can result in a very large low-freq AC noise that's difficult to fully eliminate on-die. Considering mixed-signal circuits.

# Charge Pumping (CP) Defect Measurement

ICP scales linearly with the CP gate pulse frequency such that

$$I_{\rm CP} = q A f D_{\rm it} \Delta E \tag{1}$$

where q is the electronic charge, A is the device area,  $D_{it}$  is the energetic and areal interface state density (cm<sup>-2</sup> eV<sup>-1</sup>), and  $\Delta E$  is the CP recombination energy window [3]. For the case

$I_{total} = I_{cp}(f) + I_{other}$

The number of SiO2-gate interface defects ( $N_{it}$ ) can be measured by: applying a square wave to the MOS stack and measure the change in bulk current. The CP current can be isolated because it behaves differently with frequency compared to the other leakages.

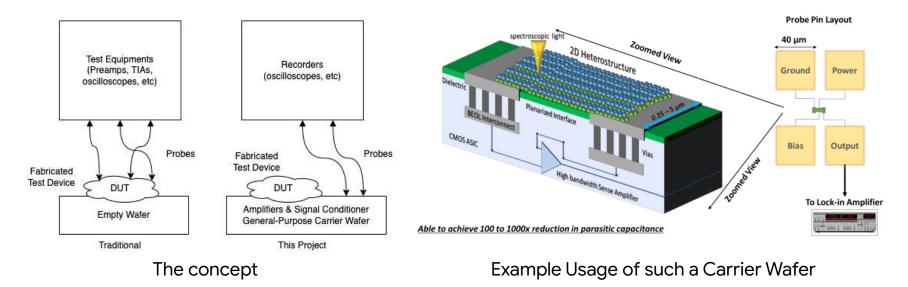

## Nanotechnology Accelerator

The aim of this project is to put some test apparatus on a silicon chip, which will be used as the carrier wafer for new nano device fabrication.

Drastically reduced parasitics can lead to improved measurement quality and test ranges.

# Tape Outs in Intel 16 - OpenTitan SoC

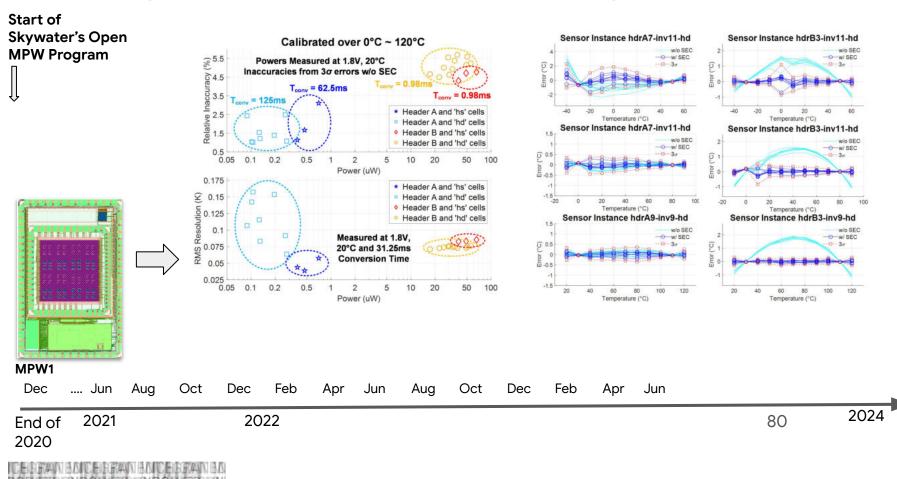

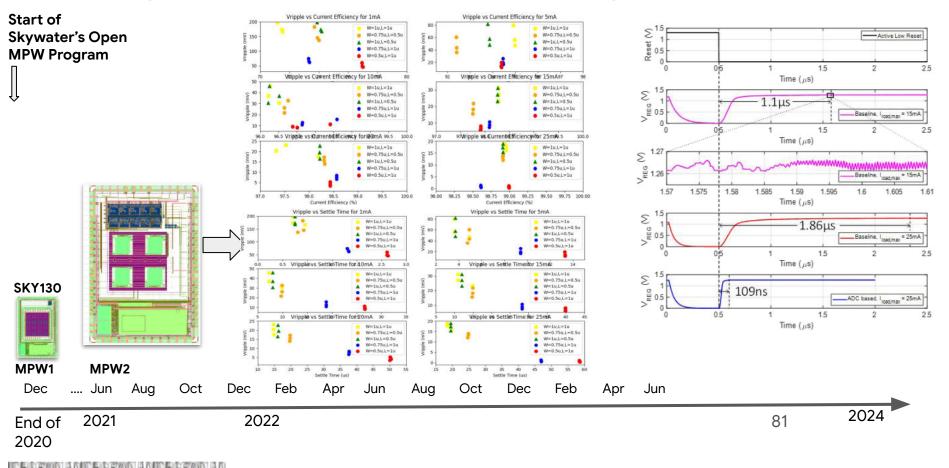

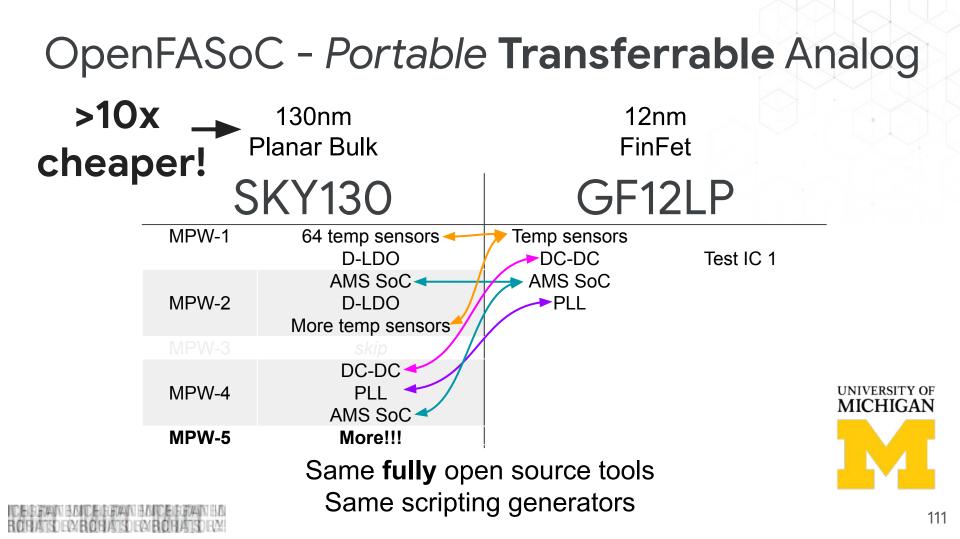

# **OpenFASoC** - Portable Analog

- Analog generators Power DCDC + LDO, Temperature Sensors, PLLs, ADCs.

- Example mixed signal SoC integration.

- Silicon proven with increasingly more tape outs, increasingly faster!

- Fully open source flow using fully open source tooling (OpenROAD, Xyce).

- Demonstrating acceleration of velocity and productivity.

130nm

# SKY130 - GF12LP

12nm

>10x 🗡 cheaper!

Planar Bulk FinFet

Same fully open source tools

Same scripting generators

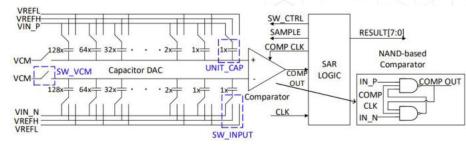

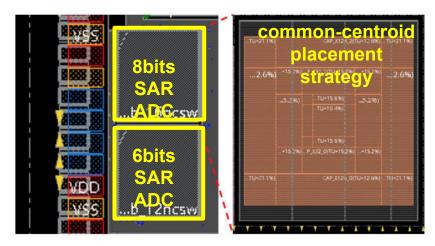

# SAR ADC Common Centroid Placement

Symmetrical Placement of unit caps and switches

| Output Spec.                       | CDL              | PEX  |  |

|------------------------------------|------------------|------|--|

| F <sub>SAMPLING</sub> (MHz)        | 1                |      |  |

| Unit Cap Value (fF)                | 2.6              |      |  |

| Area (mm <sup>2</sup> )            | -                | 0.04 |  |

| Power (µW)                         | 6.72             | 11.2 |  |

| Effective Number of Bits           | 7.86             | 7.75 |  |

| Blective Number of Blts            |                  |      |  |

| 6.5 2 4 6 8<br>Number of Vcm Switc | 10 12 14<br>thes | 16   |  |

SAR ADC Block Diagram

# Open Source RoT

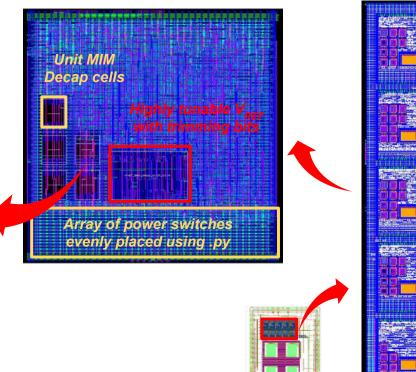

## OpenFASOC on MPW-II: Integrated Temperature Sensors

Sensors are embedded inside the OpenTitan SoC and connected through tilelink

The temperature sensor generator uses a fully open source flow

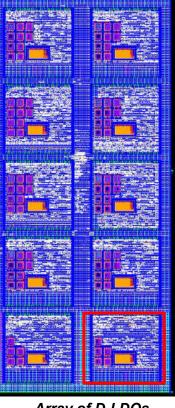

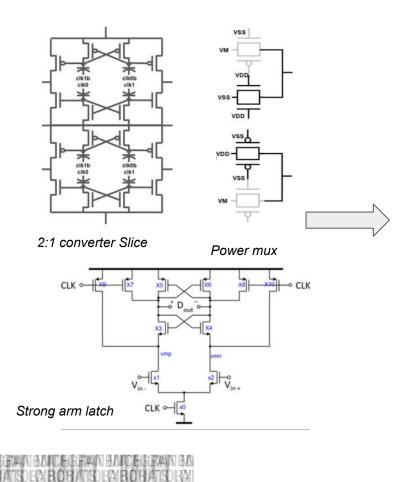

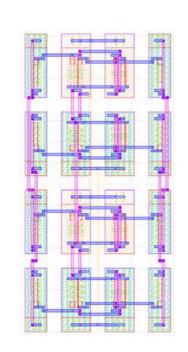

# **OpenFASOC on MPW-II: D-LDO generator**

Voltage Reference with symmetrical placement

Array of D-LDOs

## Analog Cell Generation using ALIGN

Generated Analog "Auxiliary Cells"

Power mux

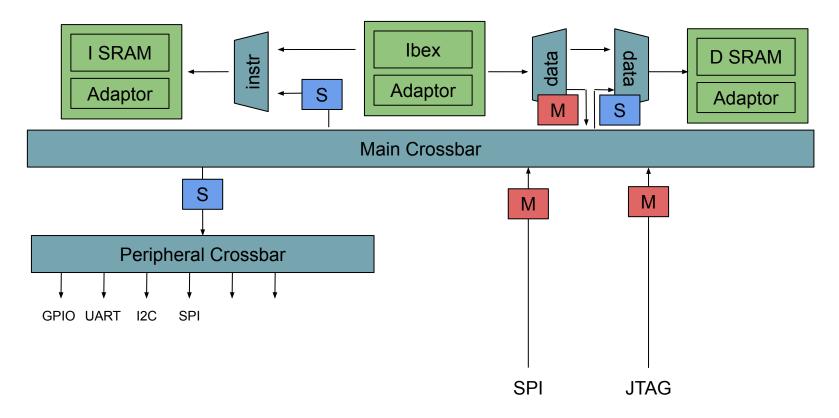

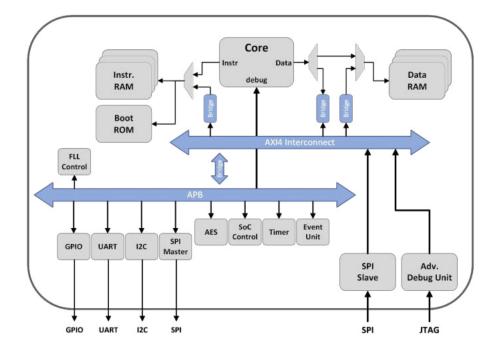

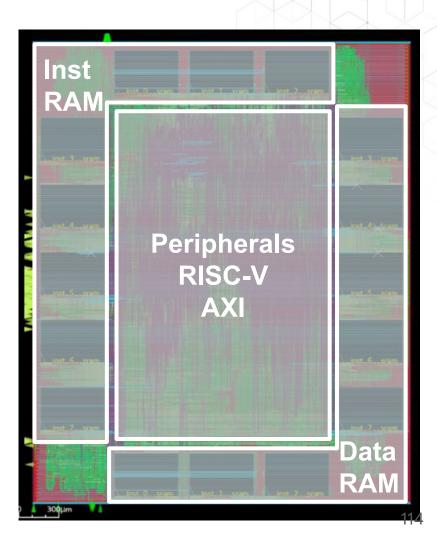

# Tape Outs in Intel 16 - OpenTitan SoC

- OpenTitan SoC contains

- SPI, GPIO interfaces

- Ibex CPU

- 16KB SRAM

- Main crossbar and peripheral crossbar

- All peripherals are connected through Tilelink

|                 | Macro Place<br>Channel | Macro<br>Place Halo | Cell Pad | Area           |

|-----------------|------------------------|---------------------|----------|----------------|

| <br>29%<br>*64% | 40 40                  | 20 20               | 2 sites  | 425x425<br>um2 |

Floorplan of in Intel 16 Including RAMs and an OpenROAD based implementation of the Opentitan SoC

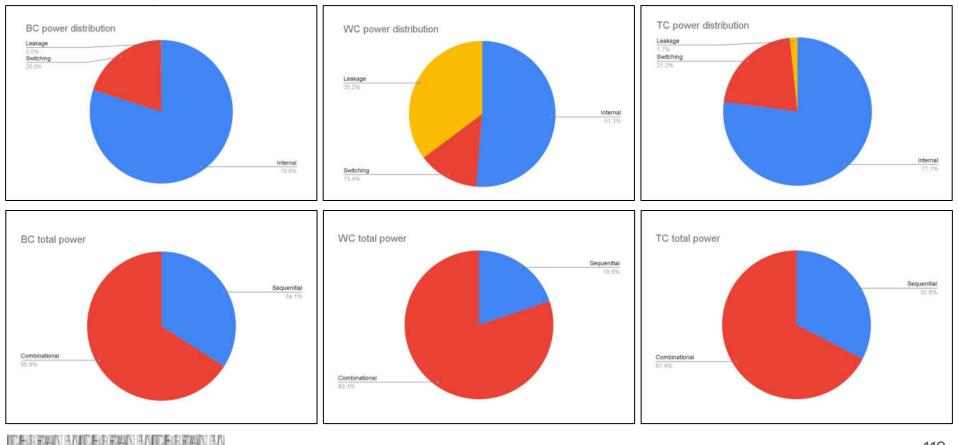

# Tape Outs in Intel 16 - Power Numbers

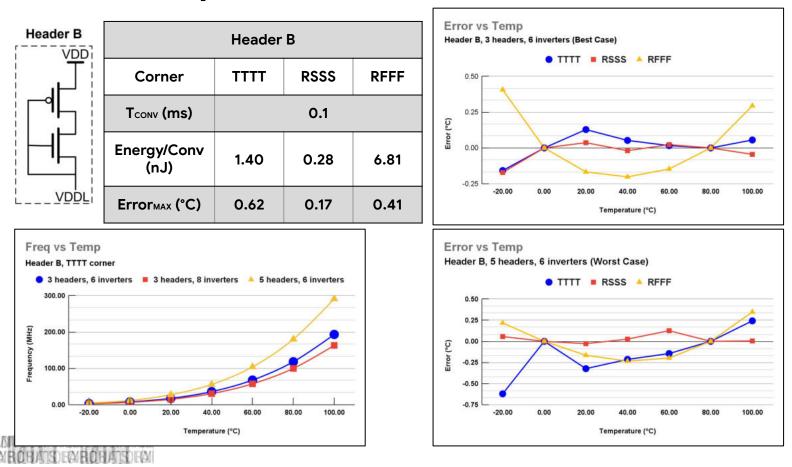

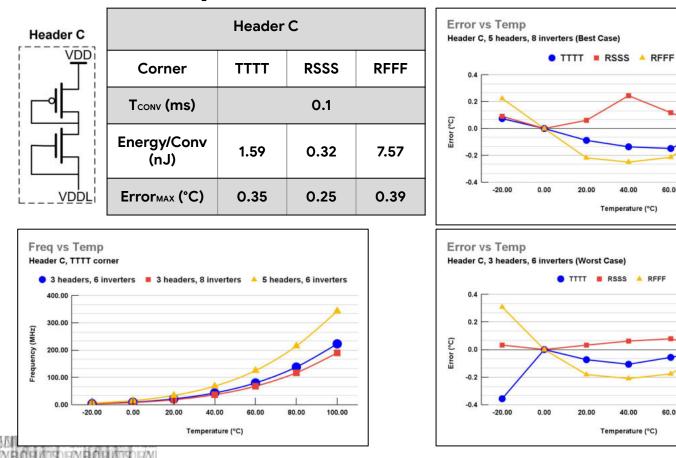

## **Temperature Sensor Variant B**

## **Temperature Sensor Variant C**

60.00

60.00

80.00

100.00

80.00

100.00

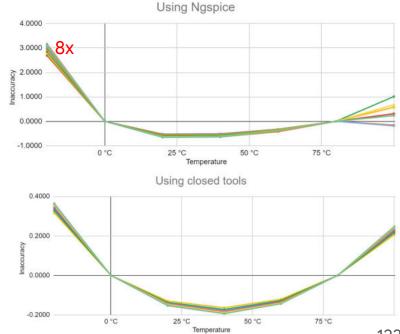

# CHIPS Alliance AWG Activities Techno/Design Loop New Measured Data, Models, CI

# Technology/Design Feedback Loop

- Compatibility between open-source models versus closed models

- Quality of models (Both closed and Open-source)

- We have to define a Technology/Design feedback loop in the Open-source real

| Discrepancies Closed vs Open-Source tools |         |        |            |  |  |  |

|-------------------------------------------|---------|--------|------------|--|--|--|

| Frequency                                 | Power   | VVDD   | Inaccuracy |  |  |  |

| -31.50%                                   | 539.63% | -0.82% | 780.93%    |  |  |  |

| -8.12%                                    | 181.81% | -0.85% | 0.00%      |  |  |  |

| -2.10%                                    | 106.59% | -1.58% | 323.15%    |  |  |  |

| -0.62%                                    | 87.81%  | -1.78% | 228.61%    |  |  |  |

| -0.08%                                    | 82.38%  | -1.70% | 192.13%    |  |  |  |

| -0.29%                                    | 80.25%  | -1.09% | 0.00%      |  |  |  |

| -0.56%                                    | 79.70%  | -0.72% | 117.29%    |  |  |  |

## Preliminary Measurements on Skywater 130nm

### Long-channel NMOS Measurements

Long-channel NMOS sEKV Extraction/Model