# Leading Semiconductor Design Revolution with SiFive 7-series RISC-V Core IP Enabling Embedded Intelligence

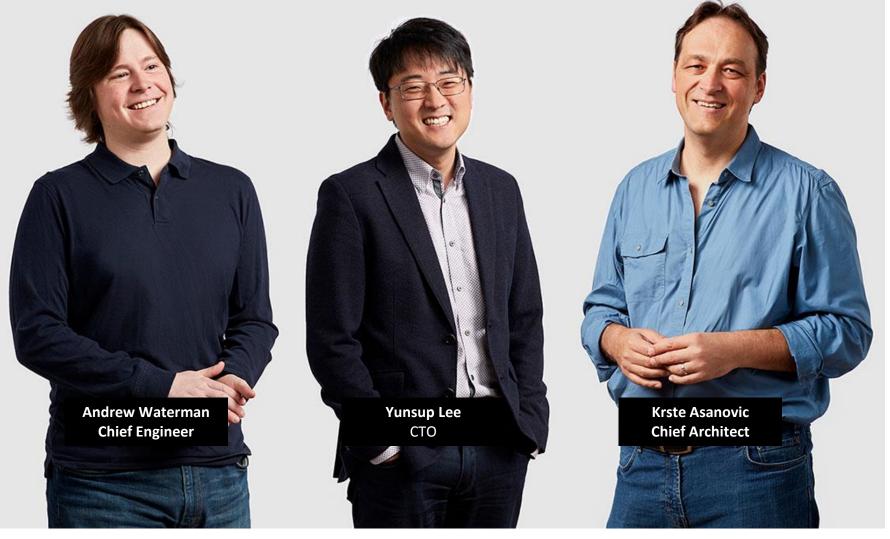

## We invented RISC-V

SiFive's founders are the same

UC Berkeley professor and

PhDs who invented and have

been leading the commercial

implementation of the RISC-V

Instruction Set Architecture

(ISA) since 2010

# **About SiFive**

#### Worldwide Presence

13 Offices 350+ Employees (275+ Engineers) 300+ Tapeouts

#### World-class expertise

- Inventors of RISC-V

- Chip Design in the Cloud

- RTL Design & Verification

- FPGA & Emulation

- Physical Design

- Wafer Fabrication

- Board Design

- Full Silicon Validation

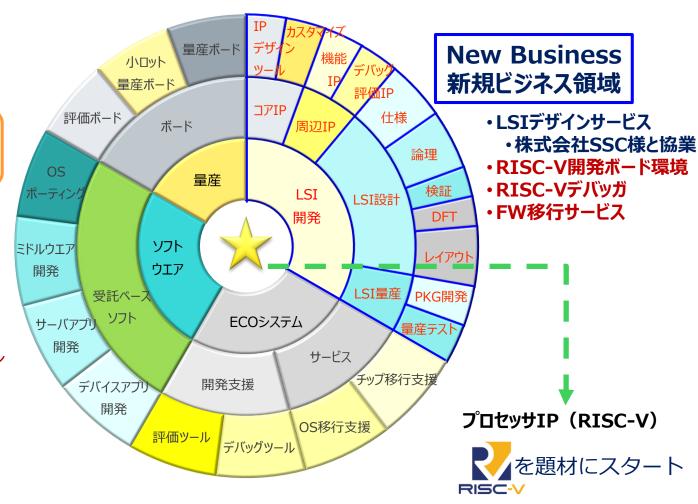

# SiFive社日本国内代理店 DTSインサイトが目指すビジネス領域

ハードウェア/ファームウェア組込などの得意領域を活かし、 お客様のあらゆるニーズにお応えする**One Stop Solution**をご提案いたします

#### Mainstream 既存ビジネス領域

- •組込みソフトウェア開発

- •ハードウェア開発

- (回路設計、PCB設計、機構・ 筐体設計から試作製造、量産)

- •デバッガ(ICEなど)

- データモニターツール

- •動的テスト/解析ツール

- •ソフトウェア構造分析ツール

- トレーサビリティ管理ツール

# What we do

#### **Leaders in RISC-V**

- Inventors of RISC-V

- Most complete product line of CPU IP: from microcontrollers, to embedded, to highperformance multi-core processors

- Very easy to customize

#### Leaders in taking Semiconductors to the Cloud

- Leverages software, highlevel design, and automation

- Dramatically reduce cost and increase innovation

- Builds custom CPU IP and ASICs

# Leaders in traditional ASICs (CSoC BU)

- Flexible engagement model (Spec2Chip, RTL, Netlist, GDS2, Production)

- Robust design methodology and extensive experience in integration of IP

- Manufacturing excellence

- Full responsibility of production supply chain

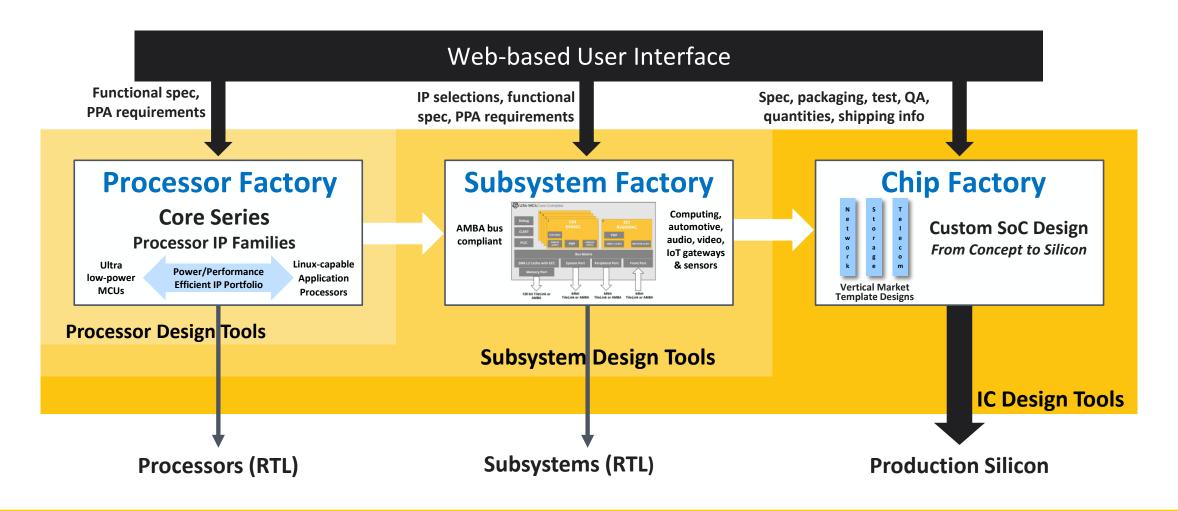

# **INNOVATION** by SiFive

Introducing a fundamentally new approach to developing processor IP and custom SoCs (CSoCs)

# **Custom SoC BU: Full Turnkey Custom SoC Solution Capability**

Product

Requirement &

Specification

Architecture

Analysis, RTL Design

& Verification

Software Design,

Development &

Test

FPGA & Emulation

**Physical Design**

Post Silicon

Validation &

Software Bring-up

**Board Design**

Test & Production Engineering

Package & Assembly

**Wafer Fabrication**

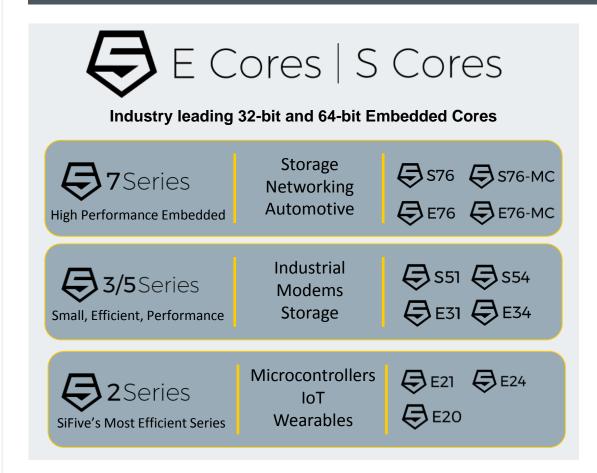

# SiFive RISC-V Core IP Product Overview

## SiFive Core IP: Efficient, High-Performance, Customizable Core IP

#### SiFive RISC-V Core IP

#### 32-bit Embedded Cores

- Edge Computing

- Artificial Intelligence

- Embedded IoT

- Wearables

#### **Industry leading 64-bit Embedded Cores**

- Embedded Intelligence

- Storage/SSD

- AR/VR

- · Machine Learning

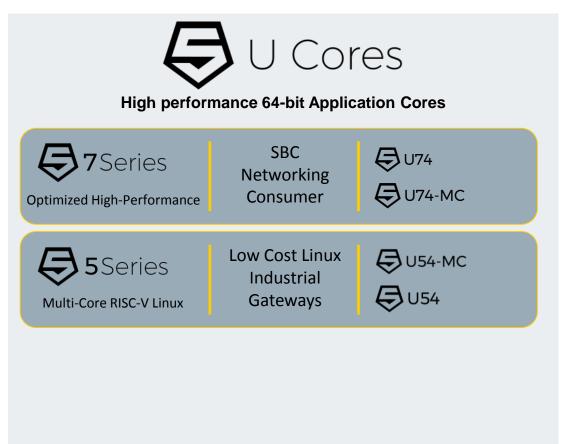

# High performance, 64-bit Application Processors

- Linux applications

- Datacenter Accelerators

- Storage system controllers

- · Networking baseband

#### Lowest Risk, Fastest Time to Market

- SiFive IP is silicon-proven and our licensees are shipping

- Leaders in RISC-V standardization and new spec development

- Broadest portfolio of mature cores and a well-funded roadmap

# Unique features that scale across entire product portfolio

- Single delivery with multiple cores, coherent memory subsystems, buses, assembled and verified by SiFive

- Highly Configurable, pre-integrated Verilog deliverables

#### Multiple Customization Options

- Highly configurable cores to achieve application specific requirements

- Custom Instructions interface allows for differentiation enabled via the extensibility of the RISC-V ISA

- Subsystem, memory map, etc.. are all customizable

#### Faster, Efficient Processors

Measured higher total performance and performance/mW vs similar designs in the same process node

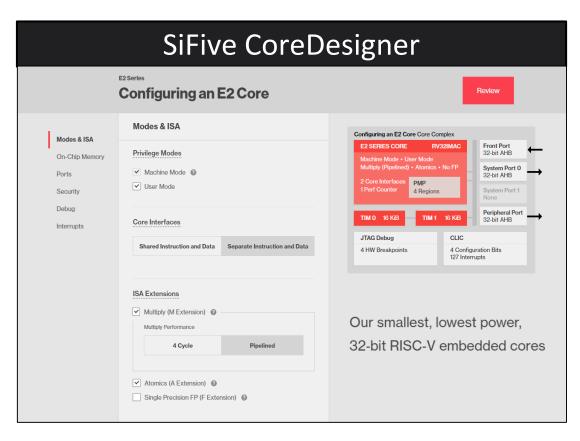

# **NEW IP PARADIGM: SiFive Core Designer** $\Leftrightarrow$

- Annual subscription allows a customer's engineers to access SiFive's entire processor portfolio via a simple web interface

- Configuring SiFive's processor IP is fast and easy

- A configured processor is generated in the cloud and the results are delivered to the user's SiFive dashboard (RTL, SDK, test bench, docs)

- Explore Before allows engineers to analyze their configured cores in their system simulations before committing to using them

- There is no processor modeling language to learn and no IP configuration tools to install

- FPGA bitstreams are provided to allow SW to run on a configured processor

RISC-V grants every user the right to modify their processor IP; SiFive has made it incredibly easy to do so.

# **BUSINESS MODEL**

# Subscription-based license for SiFive Core Designer

- Annual fee is based on which core series are included

- SaaS model significantly reduces your IT and EDA support requirements

- The most cost effective way of creating your own custom RISC-V cores

- Allows for exploration of different configurations

# Predictable usage costs

- Pricing is determined upfront and is valid during subscription term

- Prepaid upfront and/or negotiated usage table for follow-on projects

# SiFive IP Portfolio

| Core Series                                                                                                                                                                               |           | Area                                     | Standard Cores          | ARM Comparison               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------|-------------------------|------------------------------|

| Choose your foundation  —                                                                                                                                                                 | E2 Series |                                          | E20, E21, E24           | M0, M0+, M3, M4,<br>M23, M33 |

| Core Series provide powerful capabilities for your product ideas.  Choose one of our silicon-proven RISC-V Standard Cores – or customize a core to get the precise results that you need. | E3 Series | 10 10 10 10 10 10 10 10 10 10 10 10 10 1 | <u>E31</u> , <u>E34</u> | R4, R5                       |

|                                                                                                                                                                                           | E7 Series |                                          | <u>E76, E76-MC</u>      | M7, R7, R8                   |

|                                                                                                                                                                                           | S5 Series |                                          | <u>S51, S54</u>         | R4, R5                       |

|                                                                                                                                                                                           | S7 Series |                                          | <u>S76, S76-MC</u>      | M7, R7, R8                   |

|                                                                                                                                                                                           | U5 Series |                                          | <u>U54, U54-MC</u>      | A5, A7, A35, A53             |

|                                                                                                                                                                                           | U7 Series |                                          | <u>U74, U74-MC</u>      | A55                          |

Get best-in-class processor IP developed by the inventors of RISC-V and configure it to your exact specifications

# SiFive RISC-V Core IP Product Series

#### SiFive RISC-V Core IP

SiFive

**Core Series** are customizable to meet your requirements **Standard Cores** are pre-configured, silicon-proven implementations

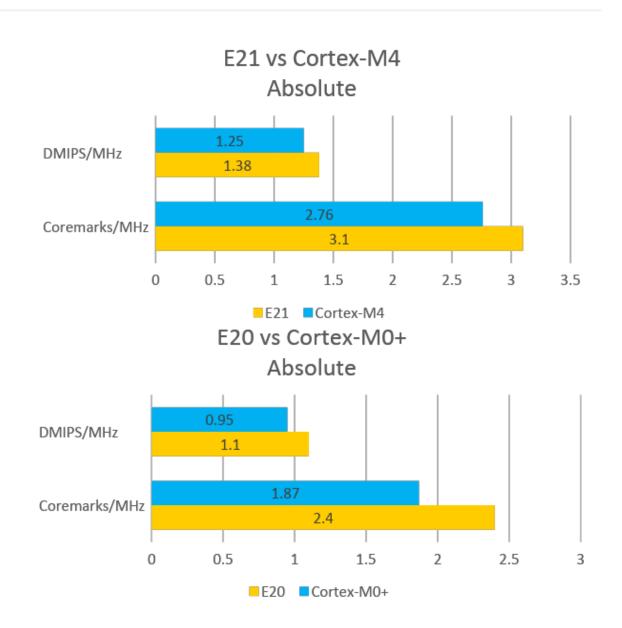

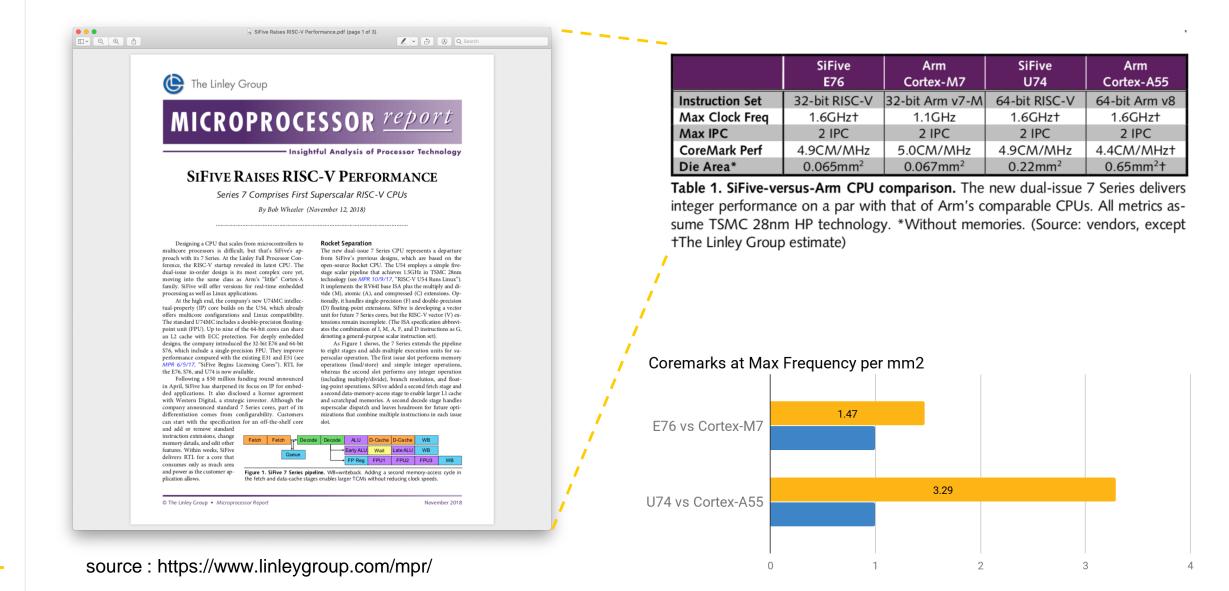

# **Better than the Competition**

- SiFive Standard Core outperform ARM equivalent cores

- E21 is 12% higher performance per MHz vs Cortex-M4 in CoreMark

- When using equivalent GCC Compilers

- E20 is 28% higher performance per MHz vs Cortex-M0+ in CoreMark

- When using equivalent GCC Compilers

- E2 Series configurability allows for the core performance and area to be tuned to the exact application requirements

- The E2 Series can be configured smaller than the E20 Standard Core

- The E2 Series can be configured with more features than the E21 Standard Core

# **Product Map**

**E**Cores

**32-bit embedded cores** MCU, edge computing, AI, IoT

**S** Cores

**64-bit embedded cores** Storage, AR/VR, machine learning

**U** Cores

**64-bit application cores** Linux, datacenter, network baseband

#### 7 Series

Highest performance: 8-stage, dual-issue superscalar pipeline

#### **E7 Series**

- > E76-MC Compare to Cortex-M7

Quad-core 32-bit embedded processor

- > E76 Compare to Cortex-M7 > S76

High performance 32-bit embedded core High-

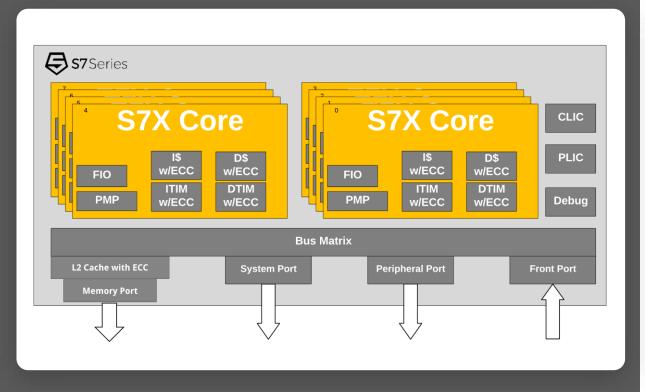

#### **S7 Series**

- > S76-MC No 64-bit Cortex equivalent Quad-core 64-bit embedded processor

- > \$76 No 64-bit Cortex equivalent > U74

High-performance 64-bit embedded core High

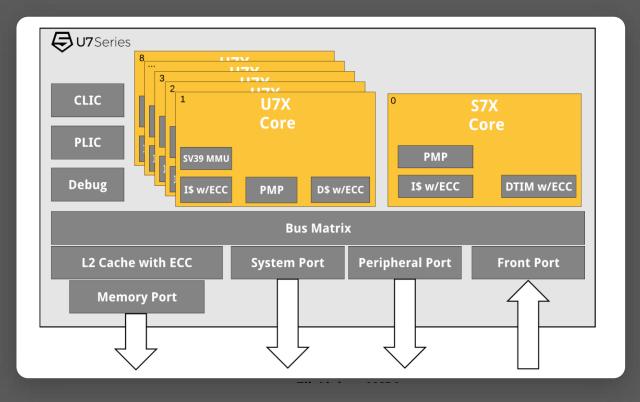

#### **U7 Series**

- > U74-MC Compare to Cortex-A55 MP4

Multicore: four U74 cores and one S76 core

- > **U74** Compare to Cortex-A55 High performance Llnux-capable processor

#### 3/5 Series

## Efficient performance:

5–6-stage, singleissue pipeline

#### E3 Series

- > E34 Compare to Cortex-R5F E31 features + single-precision floating point

- **E31** Compare to Cortex-R5 Balanced performance and efficiency

#### S5 Series

- > **\$54** No 64-bit Cortex equivalent S51 features + single-precision floating point

- > **S51** No 64-bit Cortex equivalent Low-power 64-bit MCU core

#### **U5 Series**

- V54-MC Compare to Cortex-A53 Multicore application processor with four U54 cores and one S76 core

- **> U54** Compare to Cortex-A53 Linux-capable application processor

#### 2 Series

# Power & area optimized:

2-3-stage, singleissue pipeline

#### **E2 Series**

- > **E24** Compare to Cortex-M4F E21 + single-precision floating point

- > E21 Compare to Cortex-M4 E20 + User Mode, Atomics, Multiply, TIM

- **E20** Compare to Cortex-M0+ Our smallest, most efficient core

#### S2 Series

> **S21** No 64-bit Cortex equivalent Area-efficient 64-bit MCU core

32-bit Embedded Processors

64-bit Embedded Processors

64-bit Application Processors

"SiFive's RISC-V Core IP was **1/3 the power** and **1/3 the area** of competing solutions, and gave FADU the flexibility we needed in optimizing our architecture to achieve these groundbreaking products."

-J. Lee, FADU CEO

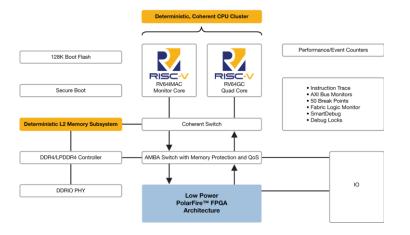

"SiFive's **64-bit S Cores** bring their hallmark efficiency, configurability and **silicon-proven** Core IP **expertise** to 64-bit embedded architectures"

-Ted Speers, Head of Product Architecture and Planning, Microsemi, a Microchip Company

64-bit Application Processors

64-bit Embedded Processors

32-bit Embedded Processors

# 86

# SiFive Core IP Embedding Intelligence Everywhere

#### Consumer

AR/VR/Gaming devices

Smart Home

Imaging/Wearables

### Storage/Networking/5G

SSD, SAN, NAS

Base Stations, Small cells, APs

Switches, Smart NICs, Offload cards

#### ML/Edge

Autonomous machines

IoT devices

SiFive realizes modern compute requirements with scalable, efficient and customizable IP

# SiFive Core IP Embedding Intelligence Everywhere

#### Consumer

Optimized power consumption

Differentiated products

#### Storage/Networking/5

Scalable portfolio

Total cost of operation (TCO)

64-bit addressability

#### ML/Edge

Custom instructions and coprocessors

Tightly coupled accelerators

Low power consumption

# SiFive Core IP 7 Series:

Embedded Intelligence Everywhere Efficient Performance

**~60% improvement** in CoreMarks/MHz\*

**~40% improvement** in DMIPS/MHz\*

~10% improvement in Fmax\*

Scalability

**8+1 coherent CPUs** in a cluster

512 coherent on-chip CPUs via TileLink

2048 multi-socket coherent CPUs via ChipLink

Compelling Feature Set

**In-cluster heterogeneous compute** for Application + Real-time processors

**64-bit architectures** across portfolio

Innovative L1 Memory microarchitecture

\*Compared to SiFive Core IP 5 series

## SiFive RISC-V Core IP - 7 Series

#### SiFive 7 Series RISC-V Core IP

Ultra-High Performance 32-bit Embedded Processors

Unprecedented Performance/Watt/mm2

Scalable Multi-Core with Coherency

Determinism for Hard Real-Time

Fast, Deterministic, Interrupt Response

Fast IO Access

Tightly Coupled Accelerators

Ultra-High Performance 64-bit Embedded Processors

Unprecedented Performance/Watt/mm2

Scalable Multi-Core with Coherency

Determinism for Hard Real-Time

Fast, Deterministic, Interrupt Response

Fast IO Access

Tightly Coupled Accelerators

Ultra-High Performance 64-bit Application Processors

Unprecedented Performance/Watt/mm2 Scalable Multi-Core with Coherency Determinism for Hard Real-Time Fast, Deterministic, Interrupt Response

#### **Common Feature Sets**

**Compared To SiFive 3 and 5 Series**

- Greater than 50% performance uplift

- Improved L1 Memory System

- 10% frequency uplift

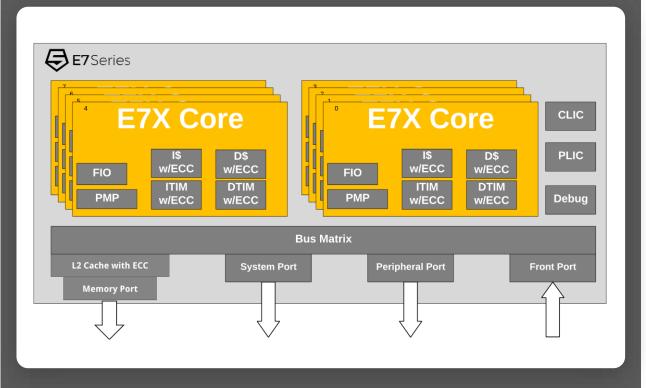

# E7 Series Features

- E7 core architectural features

- RV32GCV capable core

- Dual Issue, in-order 8-stage Harvard Pipeline

- Very flexible memory system

- Optional I\$ and D\$

- Optional I and D TIM interfaces

- Optional Fast IO Port (FIO) per core

- Multi-core capable with coherency and optional L2

- Deterministic fast interrupt responses

- Higher throughput and efficiency vs Cortex-M7

- 2.3 DMIPS/MHz

- 5.1 CoreMarks/MHz

# S7 Series Features

- S7 core architectural features

- RV64GCV capable core

- Dual Issue, in-order 8-stage Harvard Pipeline

- Very flexible memory system

- Optional I\$ and D\$

- Optional I and D TIM interfaces

- Optional Fast IO Port (FIO) per core

- Multi-core capable with coherency and optional L2

- Deterministic fast interrupt responses

- Higher throughput and efficiency vs Cortex-R8

- 2.5 DMIPS/MHz

- 5.1 CoreMarks/MHz

# U7 Series Features

- U7 Core Architectural Features

- RV64GCV capable core

- Sv39 Virtual Memory Support

- Dual Issue, in-order 8 stage Harvard Pipeline

- Heterogenous in-cluster combination of applications processor and real-time processor supported

- Configurable Level 2 Cache with cache lock capability and Tightly Integrated Memory available

- Functional Safety and Security and Real Time features

- SECDED ECC on all L1 and L2 memories

- PMP and MMU for memory protection

- Programmatically clear and/or disable dynamic

branch prediction for deterministic execution and enhanced security

- Extremely competitive performance vs Cortex-A55

with higher efficiency and throughput

- 2.5 DMIPS/MHz

- 5.1 CoreMarks/MHz

## 7 Series Core IP - More Efficient Performance than M7 and A55

# SiFive Silicon and Development Platforms

# HiFive1: Arduino-Compatible RISC-V Dev Board

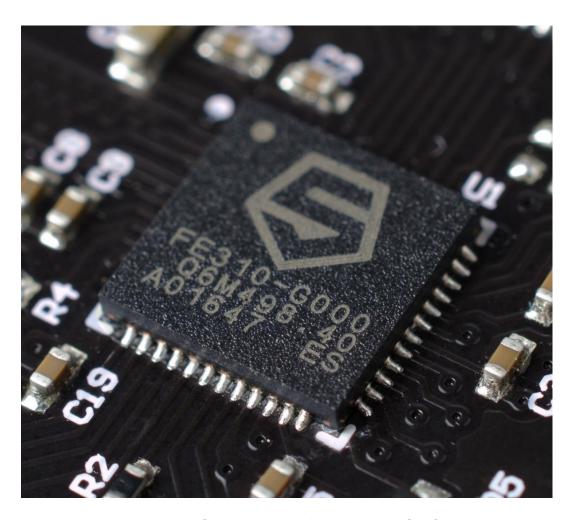

- SiFive FE310-G000 (built in 180nm)

- Operating Voltage: 3.3 V and 1.8 V

- Input Voltage: 5 V USB or 7-12 VDC Jack

- IO Voltages: Both 3.3 V or 5 V supported

- Digital I/O Pins: 19

- PWM Pins: 9

- SPI Controllers/HW CS Pins: 1/3

- External Interrupt Pins: 19

- External Wakeup Pins: 1

- Flash Memory: 16 MB Quad SPI

- Host Interface (microUSB): Program, Debug, and Serial Communication

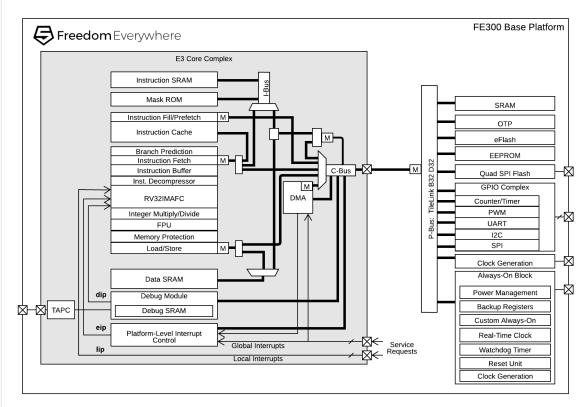

# Freedom Everywhere 32-bit Low-power microcontroller platform

- 320+ MHz SiFive E31 CPU

- 16KB L1I\$, 16KB Data Scratchpad

- Hardware Multiply/Divide, Debug Module

- Multiple Power Domains

- Low-Power Standby

- Wide Range of Clock Inputs

Freedom E310, QFN48, manufactured in TSMC 180nm

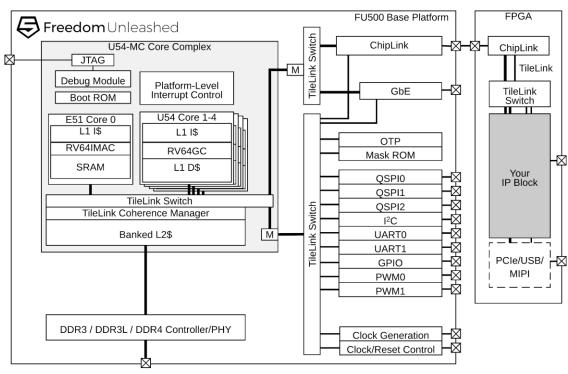

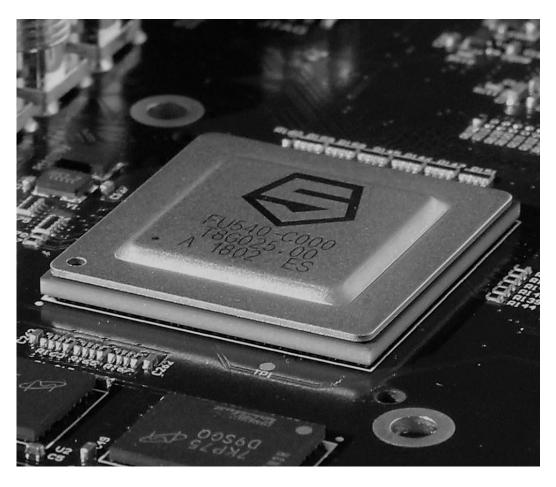

#### HiFive Unleashed: World's First Multi-Core RISC-V Linux Dev Board

- SiFive FU540-C000 (built in 28nm)

- 8 GB 64-bit DDR4 with ECC

- Gigabit Ethernet Port

- 32 MB Quad SPI Flash

- MicroSD card for removable storage

- MicroUSB for debug and serial communication

- Digital GPIO pins

- FMC connector for future expansion with add-in cards

# Freedom Unleashed 64-bit Multi-Core RISC-V Linux Platform

- 1.5+ GHz U54-MC SiFive CPU

- 1x S51: 16KB L1I\$, 8KB DTIM with ECC support

- 4x U54: 32KB L1I\$, 32KB L1D\$ with ECC support

- Single- and Double-precision floating-point support

- 2MB Banked L2\$ with directory-based cache-coherence & ECC support

- ChipLink

- Serialized Chip-to-Chip Coherent TileLink Interconnect

- DDR3/4, GbE, Peripherals

Freedom U540, FCBGA, manufactured in TSMC 28nm