# Challenges in Open-source RISC-V Implementations

### Differentiation & Customization

# Open Source Hardware – Promises and Hopes

- Great way to collaborate...

- Very good for academia

- But not so much for the industry ...

### Many Open source RISC-V cores(HW)

- 主に大学、研究機関が率先 (一部企業も)

- PULP、Ariane: ETH Zurich

- LowRISC: lowRISC

- BOOM: UCB Bar, Esperanto

- Rocket: UCB Bar, SiFIve

- SweRV EH1: Western Digital

- 。など

- GITHUB等を通して簡単にダウンロードできる。

- 。但し、ダウンロードできるだけで簡単にビルド、インストールできる ということではない。

### オープンソースは実際使えるのか?

- オープンソースはそもそも製品ではない。

- 。製品リリースとしてパッケージされているわけでは無い。

- 。 プロセッサIPはRTLとコンパイラ(SDK)だけで十分で無い。

- ・ EDAスクリプト、フロアプラン

- 検証、テスト環境(テストベンチ、テストプログラムなど)

- ・ リントレポート など

- 。 RTLにマッチしたシミュレータはあるのか?

- · ソフトウエア開発にはRTLにマッチしたサイクル精度のシミュレータは欠かせない

- 。ドキュメントは完備しているのか?

- サポートはどうするのか?

- 。SoC開発時のサポート

- RTLの不具合が見つかった場合誰にサポートを依頼すれば良いのか?

- · SoC開発のスケージュールに見合った不具合修正をしてもらえるのか?

- 。 SoC出荷後のサポート

- 出荷後オープンソースのコアにバグが見つかった場合のSDKパッチを誰がするのか?

- 。 長期的サポート

- 出荷したSoCが市場で使われている限りそのバージョンのプロセッサに対するSDKサポートは続く。

- オープンソースは結果的により費用が掛かることになりかねない。

### 例えば 車載SoCの開発において

- 自動車メーカーのISO 26262要求

- 。多大な費用が必要

- 。長期にわたるサポートコミットメント

- "コミュニティー"できるのか?

- 。誰が費用負担をする?

- 。誰が長期にわたるサポートを引き受ける?

- オープンソース、コミュニティベースは非現実的

- 。フリー(ノーコスト)コアは非現実的

- 利益にならなければ誰もやろうとはしない (費用を負担したくない)。

### Challenges – Possible Solutions

- 自社開発

- 。社内に相応のエンジニアリングチームが必要

- 。多額のコストがソフトウエアツールの開発とメンテナンスに必要

- off-the-shelf RISC-V processorをライセンスする

- 。費用面では一番ローコスト

- 。だが、カスタマイズには対応していない。

- 製品化した設計ツールを用いた設計開発

- 。ISA拡張を含めたカスタマイズが可能

- 。費用面で完全自社開発に比べ優位

- ・ 少人数のエンジニア

- 長期にわたるサポート(アップデート)を自動化できる

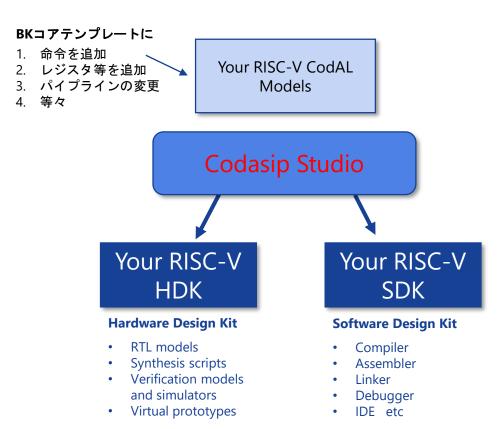

### **Codasip Solutions**

RISC-Vコアとプロセッサ設計ツールの同時提供

- コア: Codasip Bk = portfolio of RISC-V processors

- ツール: **Codasip Studio** = unique design automation toolset for easy BK processor modification

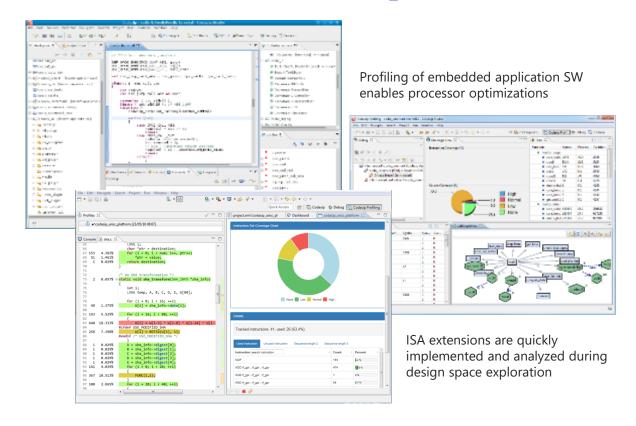

- Performance/power efficiency and low-cost

- Algorithm acceleration (DSP, security, audio, video, etc.)

- Profiling tools of embedded SW for tailoring processor IP

Codasip introduced its first RISC-V processor in November 2015

### Bk: Customizable RISC-V Cores

**Bk** = the Berkelium series, Codasip's RISC-V processors. Multiple Options

- Available immediately

- Pre-verified, tape-out quality IP

- Users do not need to verify IP

- Support for all RISC-V ISA standard extensions

- Industry-standard interfaces

- AMBA for instruction and data bus

- JTAG (4pin/2pin) for debugging

- ✓ カスタマイゼーションを強力に推進

- ✓ ユーザー定義の命令セット

- ✓ ユーザー定義のレジスタセット

- ✓ ユーザー定義のFIFO, メモリ等のインタフェース

- ✓ BKコアのパイプラインの拡張も可能

# Codasip BK RISC-V IP パッケージ

完全なIPパッケージ。オープンソースをダウンロードしてインテグレーションする必要無し。 Codasip カスタマーサポートチームのフルサポート。

#### ハードウエアパッケージ (HDK)

- Verilog RTL

- SystemVerilog UVM test environment (including SystemC co-simulation)

- Automated test suite

- Sample EDA scripts

- Document

#### ソフトウエア開発キット (SDK)

- Studio/Codespace (Eclipse IDE)

- C/C++ LLVM Compiler

- C/C++ Libraries (Newlib)

- Assembler, linker, disassembler (GNU based)

- Debugger (LLDB)

- High performance instruction set and cycle accurate simulators

- Document

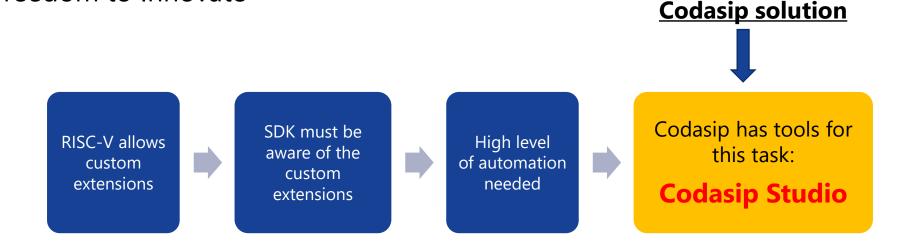

### Configuration and Custom Extensions

- RISC-V ISAセットはユーザー拡張 スペースを用意

- 。ユーザーによるアプリケーション向 けプロセッサ設計が可能

- Freedom to Innovate

しかしユーザーによる命令拡張は容 易ではない。

- -SDKツールとシミュレータ

- -RTL

- 一検証

Codasip GmbH

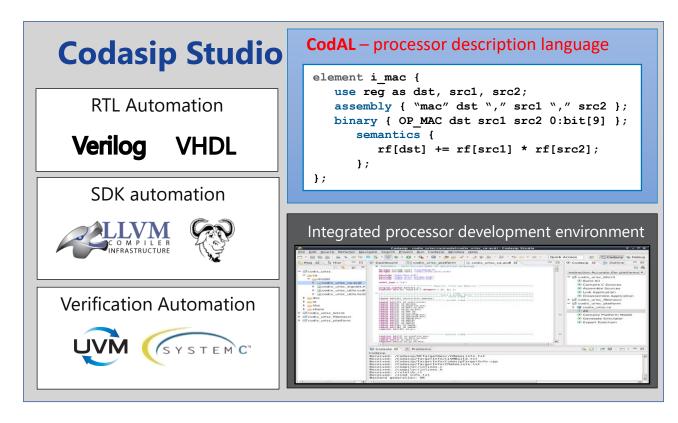

### What is Codasip Studio?

RISC-Vコアを設計する統合開発環境

silicon-proven by major vendors.

- プロセッサ生成を完全自動化

- SDK, HDKの同時生成

- C/C++ライクな設計言語(codAL)で拡張命令を記述

- 命令

- リソース(レジスタ、インタフェース)

- codALモデルの記述、デバッグ、プロファイル、検証を統合的に行えるIDE

Codasip GmbH

### **Bk Core Customization with Codasip Studio**

Codasip StudioがユーザーカスタマイズしたRISC-Vコア(HDK,SDK)を自動生成。 ユーザーは直ちにコアの評価を開始することができる。

### Conclusion

### Open Source Hardware

- 。コラボレーションのプ ラットフォーム

- 。しかし

- 。実際のSoC設計で使うに はまだ初期段階にある。

- 。全ての人にとって容易に 扱えるものにはなってい ない。

### Codasip RISC-V Solutions

- 。シリコンプルーフなRISC-V IPパッケージとRISC-Vコアを 設計する開発環境の同時提供

- Reduce the cost of custom processor development

- Simplify custom processor programming

- Enable extensible and fully custom processor methodologies

# Thank you